# A High Performance C4 Probe: TFI Market A High Probe: TFI Market A High

By

Gobinda Das and Frederick Taber

IBM Microelectronics

### A High Performance C4 Probe: TFI<sub>M</sub>

- Introducing IBM's Advanced C4 Probe Technology

- Development Background

- Technology Description

- Application & Use

- Interface Requirements

- Performance

- Summary

#### A High Performance C4 Probe: TFI<sub>m</sub>

- IBM's Advanced C4 Probe Technology TFI (Thin Flexible Interposer)

- Collaborative Effort Between IBM Sites

- SWTW: First Public Report

- Provide Awareness to Probe Community

- Patented Technology

# A High Performance C4 Probe: TFI<sub>™</sub> Development Background

- Traditional C4 Area Array Probes: Inadequate for Escalating Technical Demands

- High End Semiconductors

- Tighter Pitch

- Large # of I/O's

- Higher Power & di/dt

- Higher Frequency

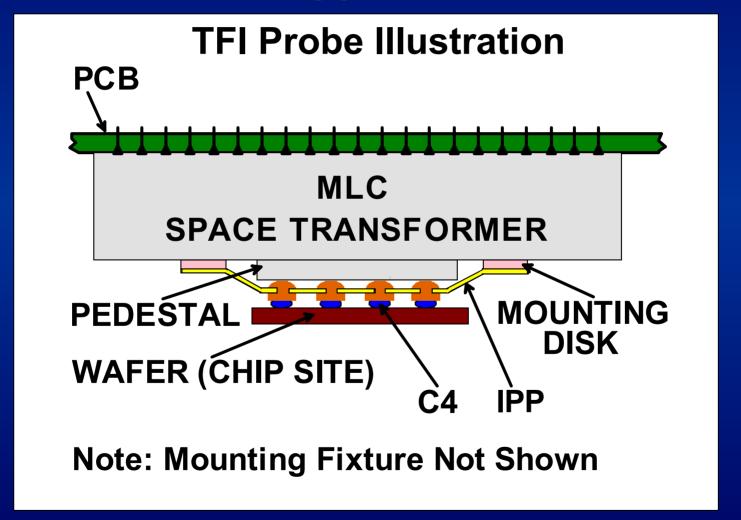

- TFI Probe System

- Interface Pellicle Probe (IPP)

- Multi-Layer Ceramic Space Transformer (MLC SXF)

- With Pedestal

- Fixturing

- Printed Circuit Board (PCB)

#### A High Performance C4 Probe: TFI

#### **Technology Description**

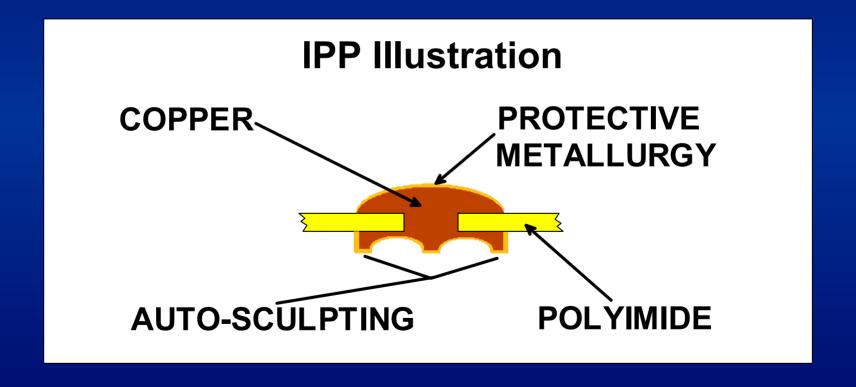

- IPP Interface Pellicle Probe

- Probing/Contact Element

- Vertical & Rigid Probe

- Array of Copper Studs On a Plated Polyimide Film

- Protective Metallurgy

- Copper Studs Match Device Footprint

- Photolithographically Defined

- Auto-Sculpted

- Diverse Densities and Configurations

#### A High Performance C4 Probe: TFI

#### **Technology Description**

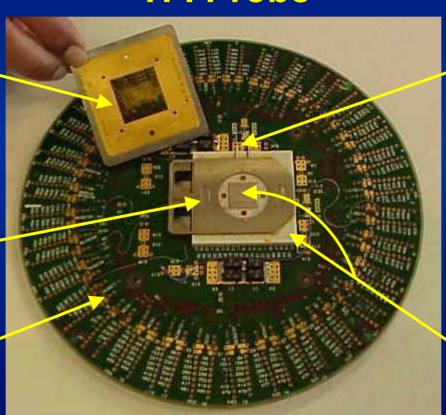

**TFI Probe**

IPP w. \_\_\_\_ Mounting Disk

**Mounting Fixture**

**PCB**

Vacuum Lines

Clamp Ring Not Shown

MLC SXF

w. Pedestal

- How Does it Work?

- Precision Assembly & Alignment to PCB

- Vacuum Mounted IPP

- Installation & Alignment Ease

- Sculpting

- Low Contact Force/Resistance

- Minimize PbSn 'Pick-up'

- C4 Reflow Integrity

- C4 'Compliance'

# A High Performance C4 Probe: TFI<sub>M</sub> Application and Use

- C4 Bumps

- Single DUT

- High Power / High Frequency / di/dt

- Very High Pin Count Area Array

- Layout Independent

- ->/= 4 on 8 Pitch

**High End Logic / ASICS**

### A High Performance C4 Probe: TFI<sub>™</sub> Application and Use

- Experience in IBM

- Initial Probe Fixture Set-up Precision

- Prober

- Test Head

- Multiple Tester & Prober Platforms

- HP, Advantest, Teradyne, etc....

- TEL, E-Glas, etc......

- Manufacturing Use

- Thousands of Wafers; Many Diverse P/N's

- 8mm to 25mm Chips

# A High Performance C4 Probe: TFI<sub>M</sub> Requirements

- Wafer / TFI Co-Planarity: +/- 0.2 mils

- C4 to Probe Misalignment: +/- 2.0 mils

- Chuck Tilt: +/- 0.2 mils

- Vacuum: 20 inches

#### A High Performance C4 Probe: TFI<sub>M</sub> Performance

- Probe Force: 2 5 Grams/Pad

- Overdrive: 2 5 mils

- Inductance: 20 pH

- Bandwidth: 3db @ 20+ GHz)

- Temperature: 55c to 85c

- Dimensionally Scalable

- Pitch, I/O Count & Layout

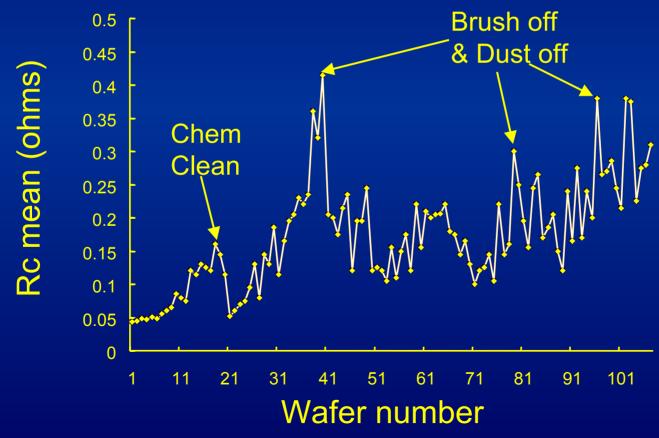

### A High Performance C4 Probe: TFI<sub>M</sub> Performance

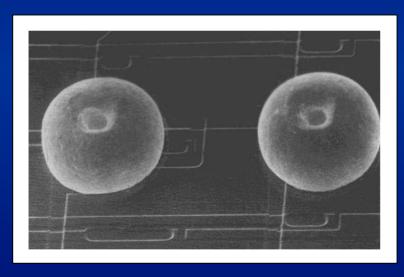

- C4 Bump (PbSn)

- Evaporated

- Plated

- Cleaning

- On-line: Brush

- Off-line: Chemical and/or Brush

- No Tweaking

- Limits Metrology Tool Need

### A High Performance C4 Probe: TFI<sub>m</sub> Performance

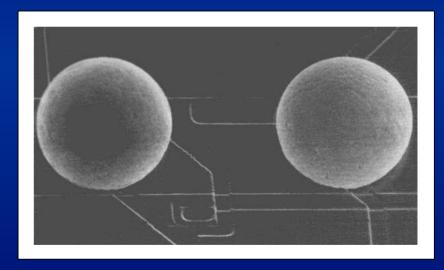

Reflow: C4 Integrity

**Post Probing**

**Post Reflow**

#### A High Performance C4 Probe: TFI...

#### **Performance**

Contact Resistance

# A High Performance C4 Probe: TFI<sub>™</sub> Summary

- TFI: A New IBM C4 Probe Technology

- Addresses High Performance Demands

- Implemented in Wafer Test Manufacturing

- Scalable For The Future

# A High Performance C4 Probe: TFI<sub>™</sub> Acknowledgements

Special thanks to Dennis Dubois, Steve Duda, Frank Egitto, Paul Gaschke and Mike Scheuermann for their dedicated & talented efforts on behalf of the TFI Project

The authors extend their thanks to Sam McKnight for his advice and contributions to this paper