## An integrated solution for KGD: At-speed wafer-level testing and full-contact wafer-level burn-in after flip chip bumping Yuan-Ping Tseng/ An-Hong Liu **TD** center

ChipMOS Technologies Inc. June 5, 2001

### Outline

- Purpose of the study

- ChipMOS KGD integrated solutions

- Cost issues

- Challenges

- Applications and future development

- Conclusion

## Purpose of the study

- An integrated solution for KGD.

- The shortest process flow for IC backend processing.

- The lower total backend processing cost.

- Meet the demand of high speed/ high frequency and light, thin, short, and small hand-held applications.

- Meet the future trend of continuous process shrink and 300mm technologies.

### Known Good Dies

- KGD are bare dies or "bumped dies" without any traditional packaging.

- KGD must

- Pass all back-end testing.

- Pass burn-in processes

- After redundancy repair on memory IC.

- Guarantee for "GOOD" functions

- Ready for applications, such as MCP, MCM, FCOB, 3D CSP, SOP, ...etc.

## ChipMOS KGD solutions

- All testing after flip chip bumping

- At-speed wafer-level testing

- No probed mark testing

- Full-contact wafer-level burn-in

- Redundancy repair after flip chip bumping and wafer-level burn-in

- FCOB memory modules

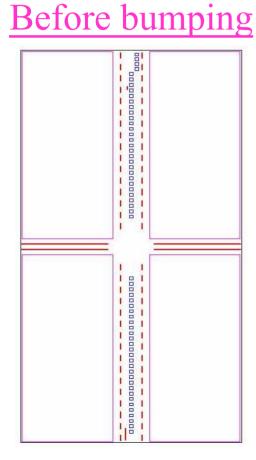

# $\begin{array}{c} \text{Major process flow (1)} \\ \hline Bumping & \Longrightarrow & WLBI & \Longrightarrow & WLT1 & \Rightarrow & Laser & \Longrightarrow \end{array} \end{array}$

Flip chip process flow:

•Design

- •(1st passivation)

- •Metal trace patterning

- •Metal trace deposition

- •2nd passivation

- •Bump base opening

- •UBM deposition

- •Bump patterning

- •Bump deposition

- •UBM etching

•Reflow

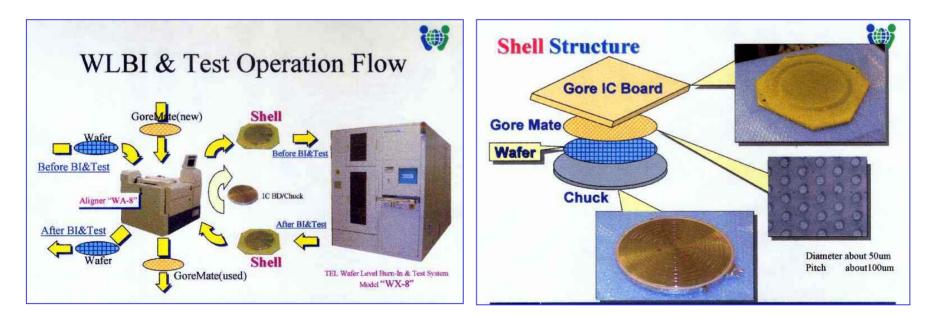

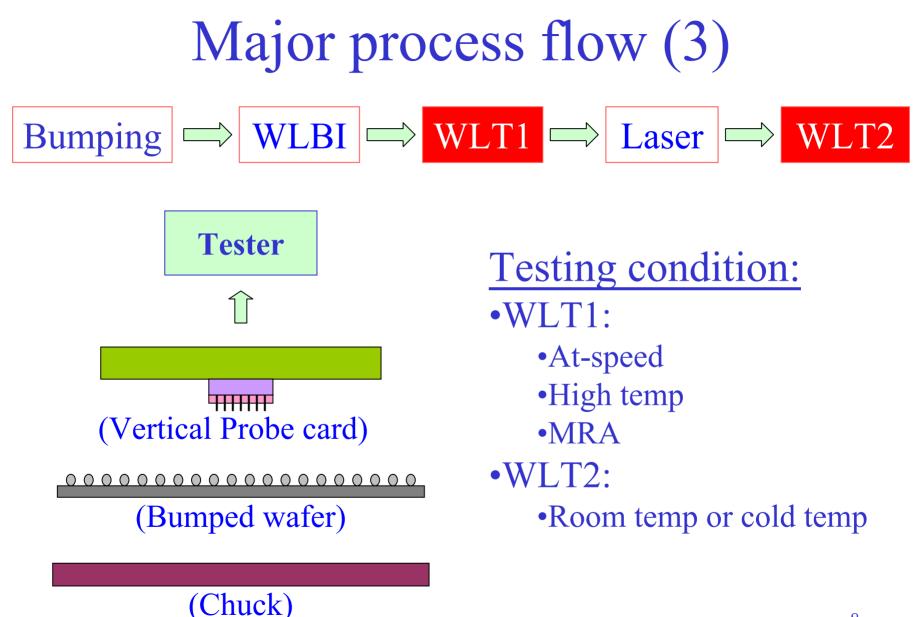

Major process flow (2)

Bumping

$$\Longrightarrow$$

WLBI  $\Longrightarrow$  WLT1  $\Rightarrow$  Laser  $\Rightarrow$  WLT2

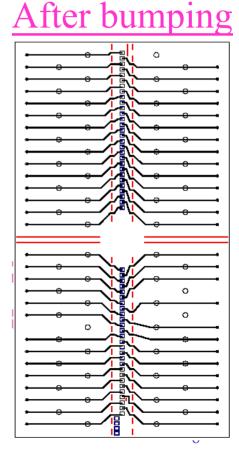

#### **Full contact wafer-level burn-in:**

### All testing after flip chip bumping

| TSOP II                             | Flip chip         | <b>ChipMOS solutions</b>    |

|-------------------------------------|-------------------|-----------------------------|

| • W/S 1                             | • W/S 1           |                             |

| • Laser repair                      | Laser repair      |                             |

| • W/S 2                             | • W/S 2           |                             |

| • <u>Assembly</u>                   | • <u>Bumping</u>  | Bumping                     |

|                                     |                   | • WLBI                      |

| • FT 1                              | • Die-level FT 1  | • WLT 1                     |

|                                     |                   | • Laser repair              |

| • B/I                               | • Die-level B/I   |                             |

| • FT 2                              | • Die-level FT 2  | • WLT 2                     |

|                                     |                   | • Wafer saw                 |

| • Laser marking                     | • Laser marking   | • Laser marking             |

| • FT 3                              | • Die-level FT 3  |                             |

| <ul> <li>Inspect/ reform</li> </ul> | • Inspect/ reflow | <ul> <li>Inspect</li> </ul> |

#### The shortest backend process flow!

## All testing after flip chip bumping

• Benefits:

– Shortest processes flow

Bumping >> WLBI >> WLT 1 >> Laser >> WLT 2

- Lower backend cost

- No investment for FT1, FT2, and FT3.

- Minimum turn around time for backend processes.

- Reduce the impact of probe cards pitch limitation by I/O redistribution.

- Lower backend cost for process shrink/ 300mm technologies.

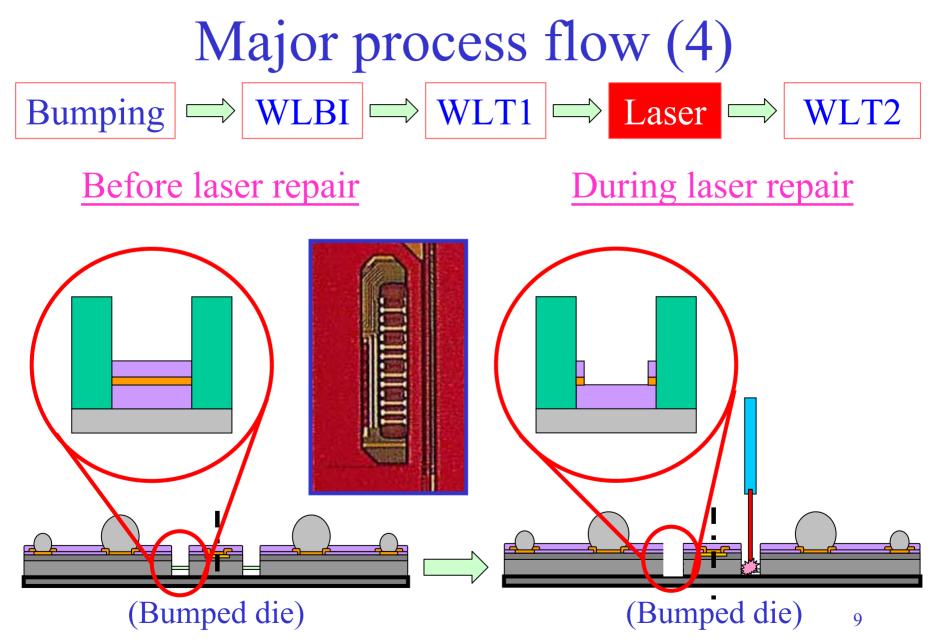

# At-speed wafer-level testing

• Benefits:

#### Testing frequency

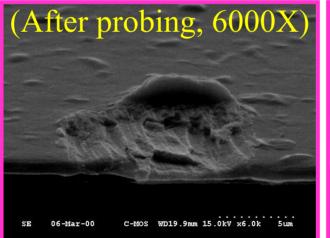

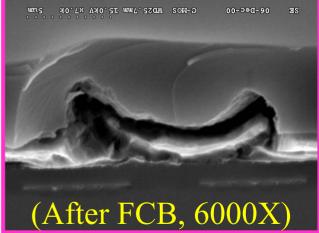

## No probed marks testing

- Benefits:

- No extra cost in making testing bumps.

- No impact of probe marks on Al pads or flip chip bumps.

- Reliability improvement in packages/ modules assembly.

Testing bumps on dies or on scribe lines.

### Full-contact wafer-level burn-in

- Benefits:

- More cost effective

- for process shrink

- for 300mm technologies

#### • Comparison:

| Items           | Solutions                           | Advantages                           | Disadvantages                 |

|-----------------|-------------------------------------|--------------------------------------|-------------------------------|

| <b>Built-in</b> | • Traditional probe                 | • Low cost                           | • Extra wafer area            |

| circuit         | card                                | <ul> <li>High throughput</li> </ul>  | for built-in circuits         |

|                 | • Tester/ prober                    |                                      | • B/I cells only              |

| Full            | <ul> <li>Special contact</li> </ul> | <ul> <li>Good B/I quality</li> </ul> | <ul> <li>High cost</li> </ul> |

| wafer           | board                               | • Cost effective                     |                               |

| contact         | • WLBI oven                         | Process shrink                       |                               |

|                 | system                              | 300mm technologies                   |                               |

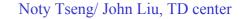

#### Redundancy repair after FCB/ WLBI

- Benefit:

- Yield gain for laser repair

| <b>During B/I</b>    | Laser before B/I | Laser after B/I |  |  |  |

|----------------------|------------------|-----------------|--|--|--|

| Passed >> Passed     | Passed           | • Passed        |  |  |  |

| Passed >> Repairable | • Failed         | • Passed        |  |  |  |

| Passed >> Failed     | • Failed         | • Failed        |  |  |  |

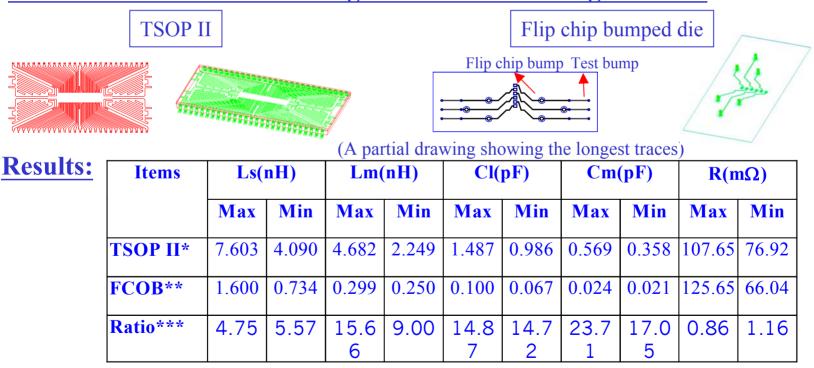

#### Electrical simulation of FCOB

#### **Condition:**

- •Software: ANSOFT Maxwell Spicelink V4.5/ AutoCAD

- •Module: Boundary Element Method Quick 3D Parameter Extractor

- •Method: Quasi-TEM Method

#### AutoCAD 2D Outline Drawing/ Maxwell 3D Package Module

\*: From pad to lead, including gold wire without considering the effect of the die.

\*\*: From pad to bump including traces without considering the effect of the die.

\*\*\*: FCOB as 1.

TSOPII

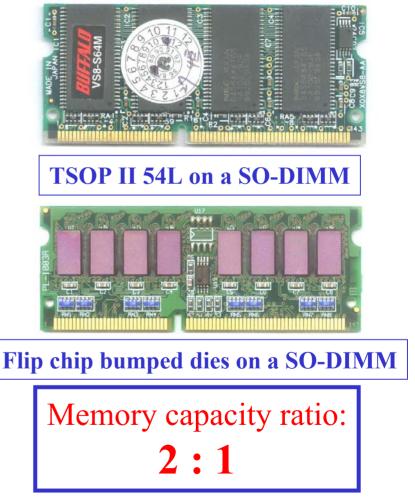

#### Footprint comparison of FCOB

#### •With same memory capacity:

•Same footprint (SO-DIMM):

Note: Use 0.20µm 64Mb SDRAM as examples.

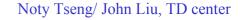

## Flip chip bumping vs. TSOP II

#### Flip chip bumping cost =

f(bumping, gross dies, wafer yield)

#### Assumptions:

- •Wafer yield: 90%

- •Bumping: 200USD/ wafer

•Gross dies:

| Process(µm) | Gross die |

|-------------|-----------|

| 0.25        | 500       |

| 0.20        | 600       |

| 0.17        | 1,000     |

#### **Process(µm)**

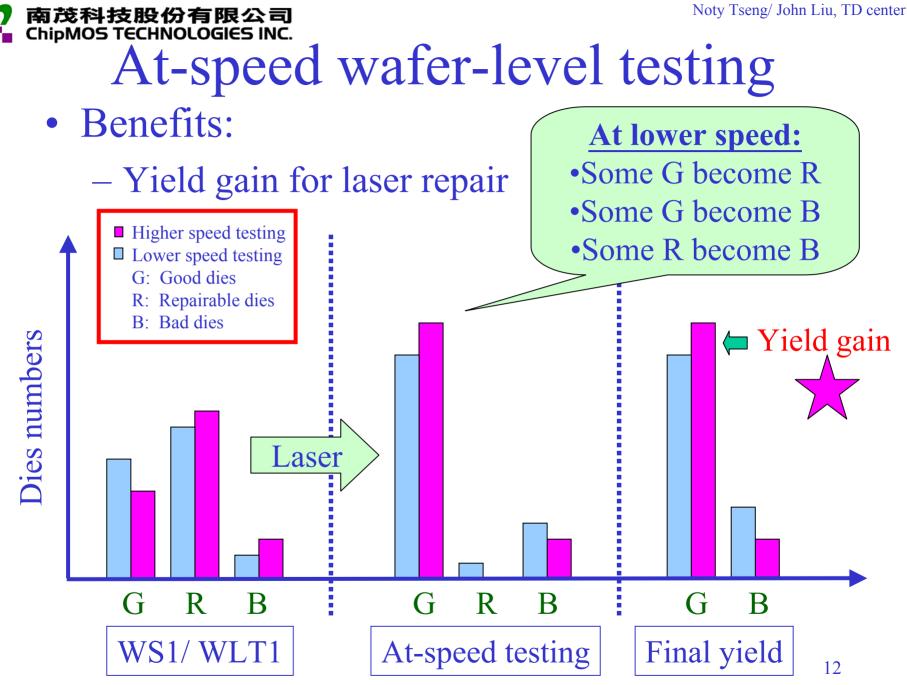

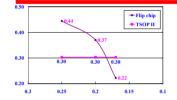

#### Wafer-level testing vs. TSOP II

#### Wafer-level testing cost = f(equipment, testing steps, throughput, wafer yield)

# Cost (US\$)

Assumptions: •Gross die: 600 •TSOP II: W/S 1, W/S 2, FT 1/2/3 •WLT: WLT1, WLT2 •Wafer yield: 90% •Probing efficiency: 80%

•Cost per die: 5US\$

•Throughput gain & yield gain:

| Testing | Throughput | Yield gain     |           |  |  |  |

|---------|------------|----------------|-----------|--|--|--|

| speed   | gain       | <b>TSOP II</b> | Flip chip |  |  |  |

| 30MHz   | 0%         | 0%             | 0%        |  |  |  |

| 50MHz   | 15%        | 0%             | 1.5%      |  |  |  |

| 100MHz  | 30%        | 0%             | 3.0%      |  |  |  |

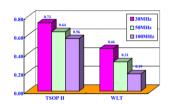

#### Wafer-level B/I vs. TSOP II

#### Wafer-level burn-in cost =

f(equipment, gross dies, wafer yield, yield gain, die cost)

# Cost (US\$)

#### Assumptions:

- •Burn-in time: 24hours

- •Wafer yield: 90%

- •Cost per die: 5US\$

- •Oven capacity: 13 wafers

- •Gross dies:

| Process(µm) | Gross die |

|-------------|-----------|

| 0.25        | 500       |

| 0.20        | 600       |

| 0.17        | 1,000     |

#### Process(µm)

# Challenges (1)

- Flip chip bumping & I/O redistribution:

- RLC for bumping and I/O redistribution design.

- Possible defects caused by wafer saw

- At-speed wafer-level testing

- Probe cards design for high speed applications.

- Accuracy of tester during high speed testing.

- Memory repair analysis during high-speed testing

# Challenges (2)

- No probed mark testing

- RLC effects of testing bumps and traces.

- The impact of testing bumps during assembly.

- Full-contact wafer-level burn-in:

- Number of contact points per wafer.

- Contact quality

- Contact coplanarity

- CTE matching

- Circuit isolation

# Challenges (3)

- Redundancy repair after FCB/ WLBI:

- Protection of fuses during FCB

- Reliability of opened laser windows during package/ module assembly

- FCOB memory modules:

- KGD issues

- Pitch limitation of module PCB.

- Reliability of FCOB.

- Warpage of PCB during module assembly.

- Accuracy of die attach

- Underfill processes on modules.

## Applications and future development

| Applications | Current    | ] | Phase 2 | P | hase 3 | P | hase 4 | Phase 5  |

|--------------|------------|---|---------|---|--------|---|--------|----------|

| KGD type     | Bumped     |   | Al pad  |   | Cu pad |   |        |          |

| Devices      | High speed |   | Other   |   | Logic  | • | CPU    | BIST     |

|              | memory     |   | memory  |   | ASIC   |   | DSP    | Embedded |

|              |            |   |         |   |        |   |        | SOC      |

| Packaging    | MCP        |   | 3D CSP  |   | SOP    |   |        |          |

| Module       | MCM        |   | FCOB    |   | FCOB   |   |        |          |

| assembly     |            |   | MCM     |   | SOM    |   |        |          |

Note:

- 1. Current device/ packaging/ module: DDR SDRAM.

- 2. SOP: System On Package, the best alternative for SOC.

#### Conclusions

• ChipMOS KGD integrated solutions:

Noty Tseng/ John Liu, TD center

#### Questions & discussions