# **Probing Lead Free Solder Bumps in Final Wafer Test**

By Sam McKnight Southwest Test Workshop June 2002

# Outline

Why lead free ? Background Info Focus areas Setup Lead/Tin and Tin "Rich" results Summary Acknowledgements

# Why Lead Free?

Increasing use of integrated circuits and shortened product life cycles prompted a world wide environmental concern regarding the disposal of electronic components.

Lead countries with environmental initiatives are Japan, Europe and the US

All levels of packaging including the interconnect to the integrated circuit are being addressed.

This presentation focuses on wafer level only

## Background Info

Cobra probe (5 mil diameter - flat tipped) is the primary contacting system for C4 VLSI test

C4 = Controlled Collapse Chip Connection (Solder Bumps)

C4's are normally reflowed before and after test

Tests temperatures -10, 25, 85 and 100C

Thermal unit range is -10 - 140C probe space transformer limit 100C (self imposed)

### **Focus areas**

- Baseline comparison measurements to Lead Tin

- Contact Resistance

- Cleaning

- Material Transfer (Pickup) To Probe Tip

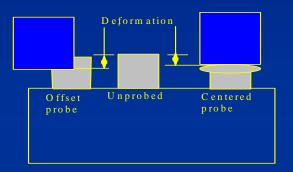

- Pad Deformation

- Alignment to C4's (Solder Bumps)

### **Probe layout**

76 contacts total Die size ~ 9.1 mm square

#### Probed pads <

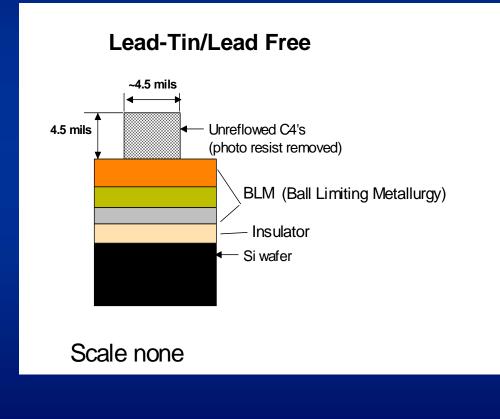

### Test wafer build structure

Sam McKnight

- TEL P8XL wafer probing system with integral -10 to 140C thermal unit w/ IBM custom tester interface with hand wired space transformer

- Z drive maximum impact velocity (~40 mm/sec)

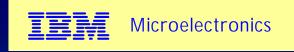

- SARA (Socket Analog Resistance Analyzer) (DC switching matrix with measurement unit)

- Cres Measurement method "pin return" with 10 ma forcing current and 5V clamp w/nulling file - to subtract path resistance

- Cleaning frequency 1/wafer (>300 sites) 5 micron abrasive material

- Environment mini-clean hood over prober

### **Contact Resistance Measurement**

#### Microelectronics

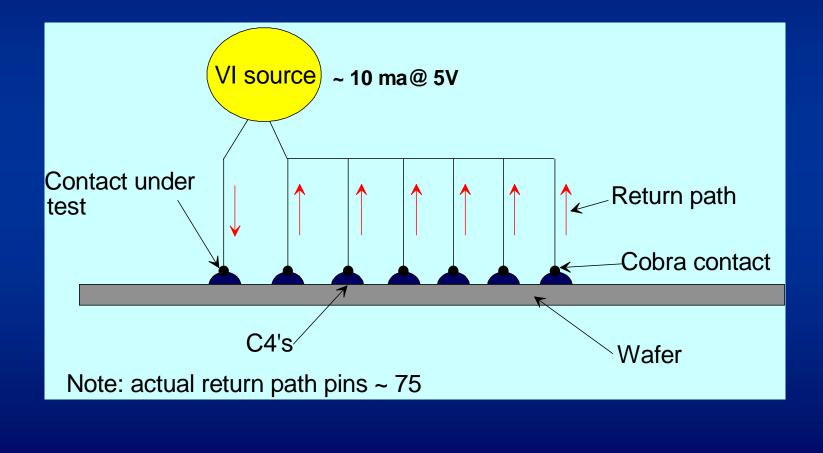

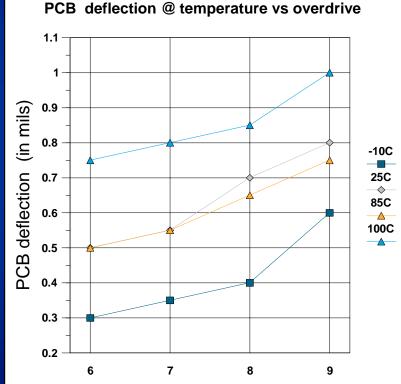

### **Cobra Probe Measurements**

Overdrive setting (in mils)

Sam McKnight

June 2002

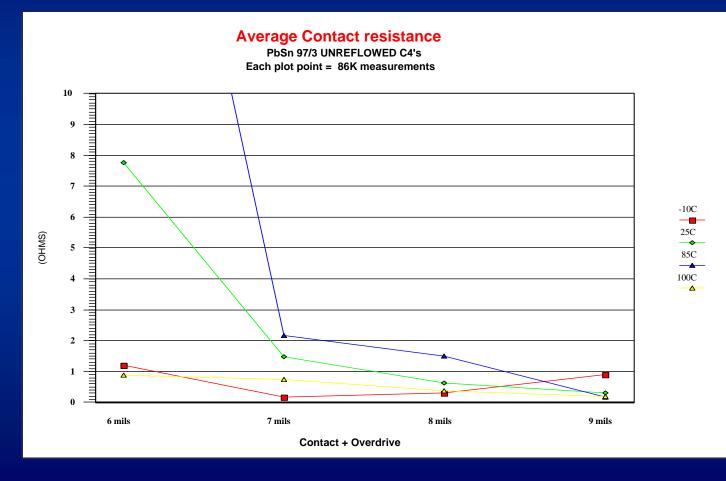

### **Un Reflowed C4's**

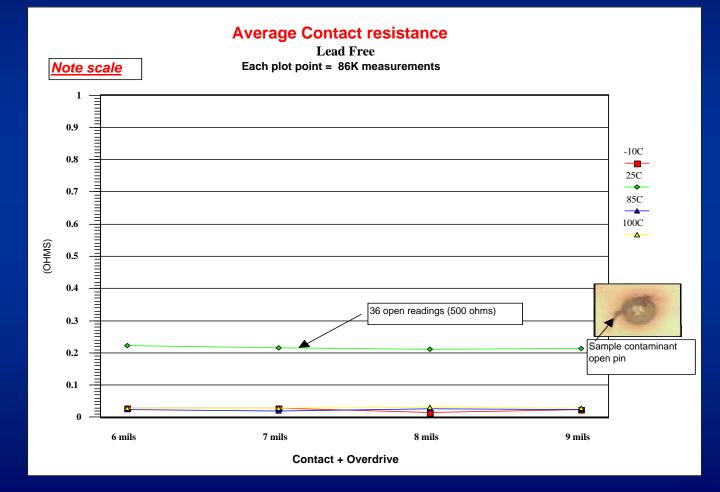

#### Lead free

Sam McKnight

### **Contact Resistance – Lead Tin C4's**

Sam McKnight

June 2002

### **Contact Resistance - Lead Free C4's**

Sam McKnight

June 2002

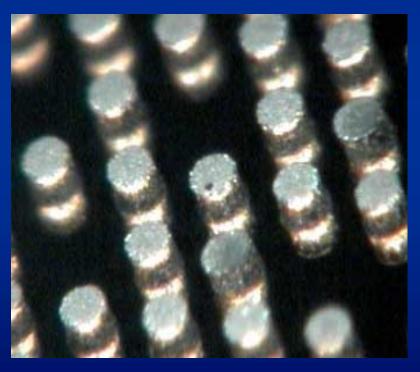

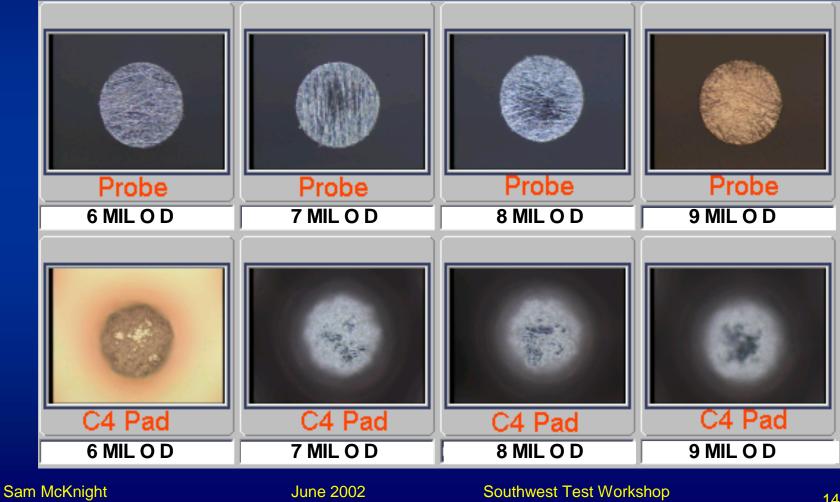

### -10°C Cobra/C4 Photos

### 25°C Cobra/C4 Photos

Sam McKnight

June 2002

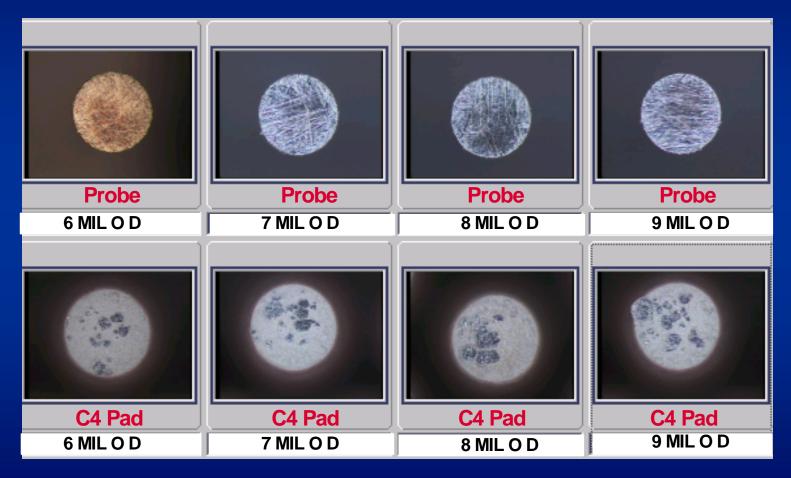

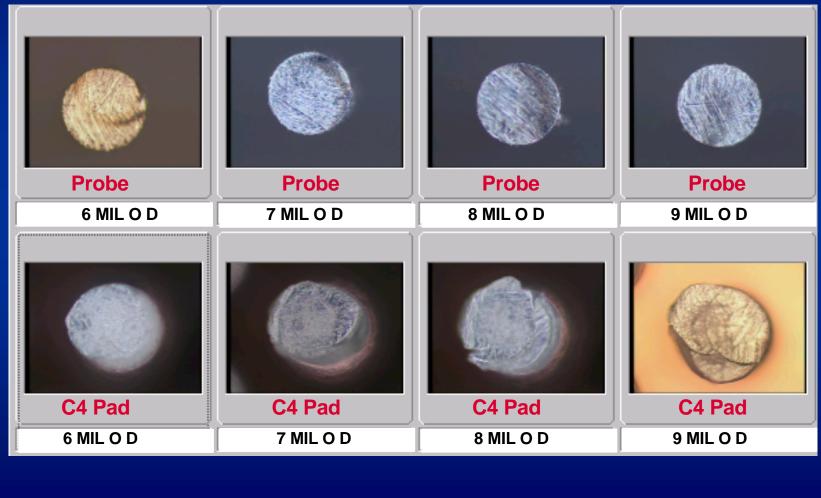

### 85° C Cobra/C4 Photo's

Sam McKnight

June 2002

### **100°C Cobra/C4 Photo's**

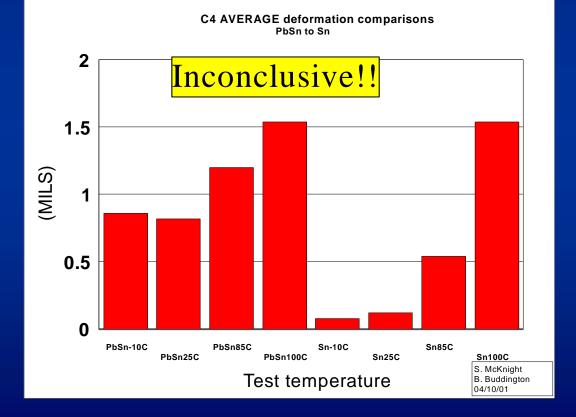

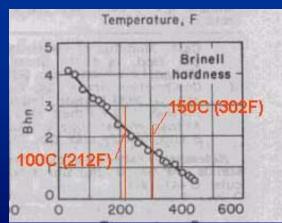

### **Pad Deformation**

Sam McKnight

June 2002

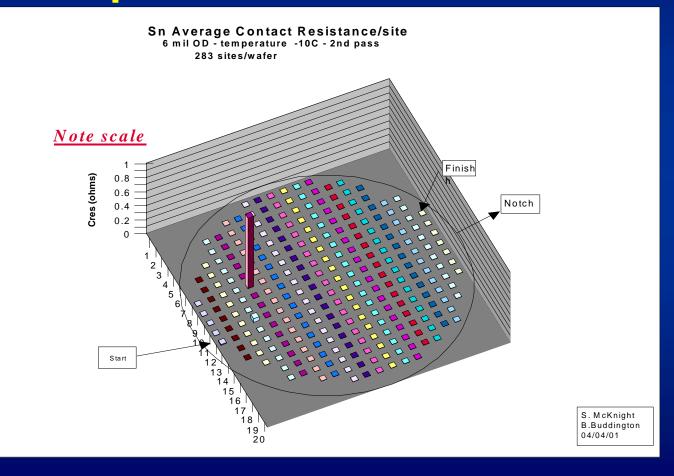

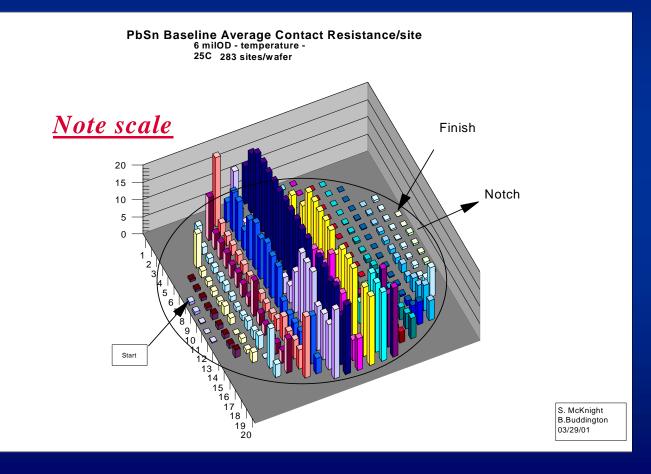

### Typical Wafer level Contact Resistance plot Lead Free C4's

Sam McKnight

### Typical Wafer level Contact Resistance plot for Lead/Tin C4's

Sam McKnight

- Contact resistance for Lead Free << 1-2 Ohms (temperature independent)

- Pad deformation inconclusive not an issue for post reflow operation

- Prober issues auto alignment (non production wafers) Partial radius on top of pad not an issue

- Cleaning frequency, 1/wafer (~300+Die) is anticipated using standard (abrasive) cleaning materials

- Material transfer to probe tip comparable to Lead/Tin

## Acknowledgements

Barry Buddington – IBM - software/setup operations Gobinda Das – IBM – PhD Steve Kilpatrick – IBM – PhD Amador Cantu Jr. – TEL Field Service