# New Tools for Probing Process Management

Cary Kiest Electroglas, Inc.

South West Test Workshop 4 June 2003 Long Beach, CA USA

## **Presentation Overview**

#### Probing Process Management

- Background

- Today's Tools

- Motivation

- An Inline Probing Process Management System

- Requirements

- System Elements

- Validation

- Practical Considerations

- Conclusions

## Background

- Technology Trends

- Test Cell Efficiency (Throughput):

- Test time per wafer is falling in many applications

- More Parallel Test

- BIST on whole wafer

- Faster Testers

- Cost of Downtime is increasing:

- Higher cost testers

- Higher cost probe cards

- Impact

- Test Cell Efficiency and Cost of Ownership are key measures

## Background

- Technology Trends

- Fine Pitch Probing:

- I/O larger than circuitry on IC's drives need for smaller pads

- Lithographic probe cards improve probe card accuracy

- 25ųm bonders means probing is only barrier to smaller pad

- Impact:

- Greater emphasis on PTPA and prober control

- Thermal stability has become vital

- Many probers are on the verge of not being capable for new probe cards

#### Definitions

- Process management is the control and improvement of business processes through understanding, measuring, innovating, and managing how work gets done to accomplish organizational goals

- Applied to wafer test, we aim to offer process characterization and understanding that facilitate improvement through reduced costs and less waste (higher yield)

- Today's Tools

- waferWoRx Probing Process Analysis:

- Enables automated root cause analysis for rapid corrective action, yield optimization and control

- Helps users differentiate between prober and probe card issues

- Eliminates need for wasteful trial-and-error problem solving

Enabling the world's core technologies

7

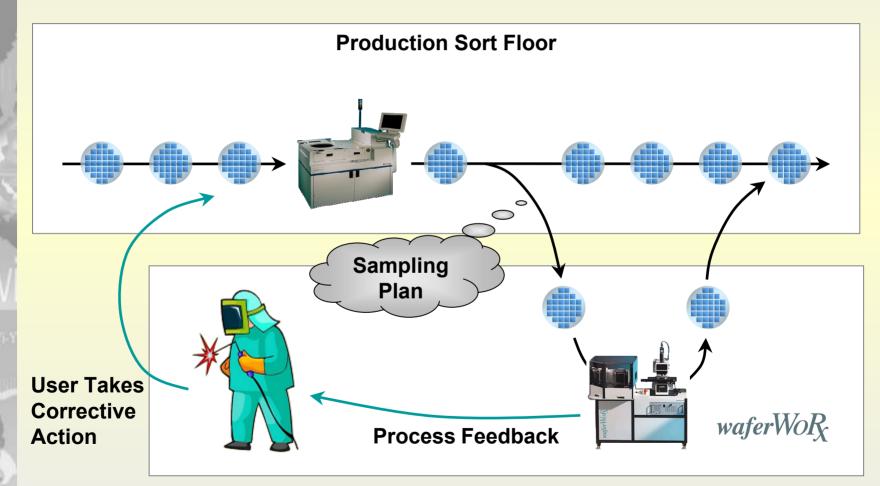

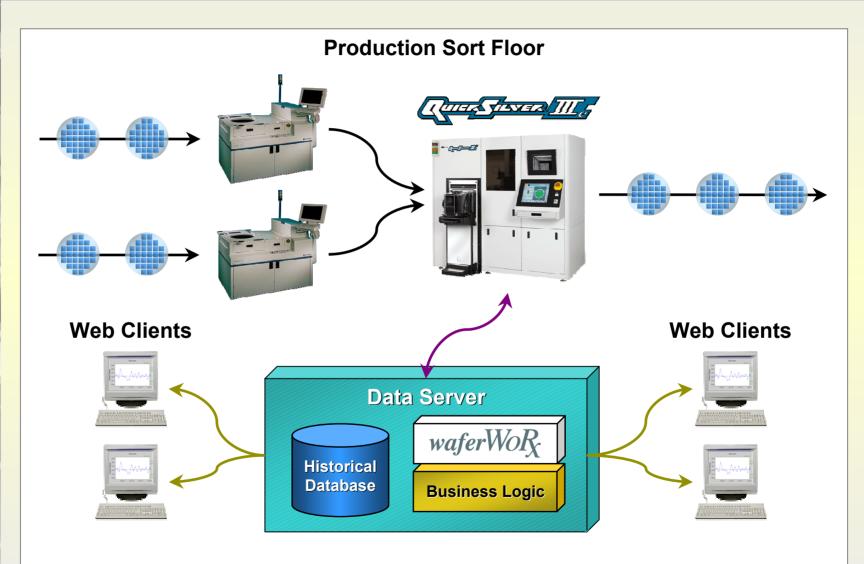

#### Product and Data Flow with Today's Tools

- Objectives for New Inline Tools

- Leverage waferWoRx analysis capability

- Increase Test Floor Coverage

- Analyze more wafers from more test cells

- Catch and correct process deviations earlier

- Expand Test Cell Performance Characterization

- Track performance history for each test cell

- Automate analysis operation

- Show trends and predict future events

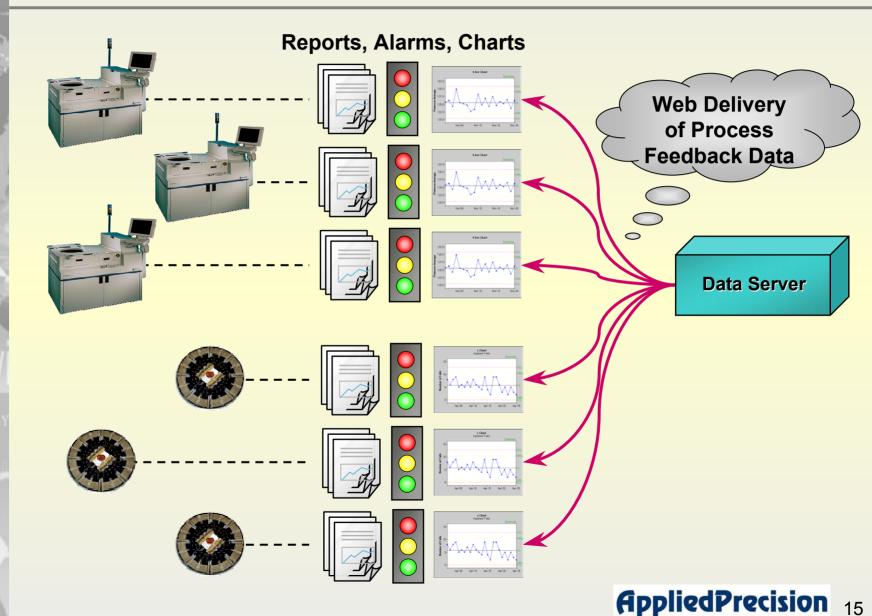

- Deliver Process Management Information

- Fast feedback response

- Format results for quick, accurate interpretation

- Make results available at all beneficial locations

### **Motivation**

- Why Do This Inline?

- Get as Close as You Can to the Probing Process:

- Faster problem detection

- Faster problem correction

- Kill Two (or more) Birds With One Stone:

- Detect and classify other wafer defects

- Detect and classify other probing problems (PMI)

- Automate wafer map updates

- Share procurement justification across multiple benefits

## An Inline Probing Process Management System

# Inline System Requirements

- Accurate Probing Process Analysis

- As throughput increases, output validity must be maintained

- Cost Effective Deployment

- Maximize Test Floor Coverage

- High throughput is key

- Track multiple test cells

- Minimize Ongoing COO

- Reliability

- Fast and Easy Setup

- Process Data Delivery

- Easy to Access and Understand

- Zero in on Priority Events Quickly

## **Inline System Elements**

| Element            | Contribution                                                                                           |

|--------------------|--------------------------------------------------------------------------------------------------------|

| waferWoRx Software | Established Standard for Probing Process<br>Root Cause Analysis                                        |

| QuickSilver        | High Throughput Metrology and<br>Inspection, 300mm Capability, Production<br>Floor Networking          |

| Data Server        | Historical Database, SPC Analysis,<br>Business Logic, Analysis Drill-Down, Web<br>Server               |

| Web Browsers       | Fast, Easy Data Delivery, Leverages<br>Existing PC / Workstation Investment,<br>Minimal Learning Curve |

## **Inline System Overview**

**AppliedPrecision** 14 Enabling the world's core technologies

#### **Process Data Delivery**

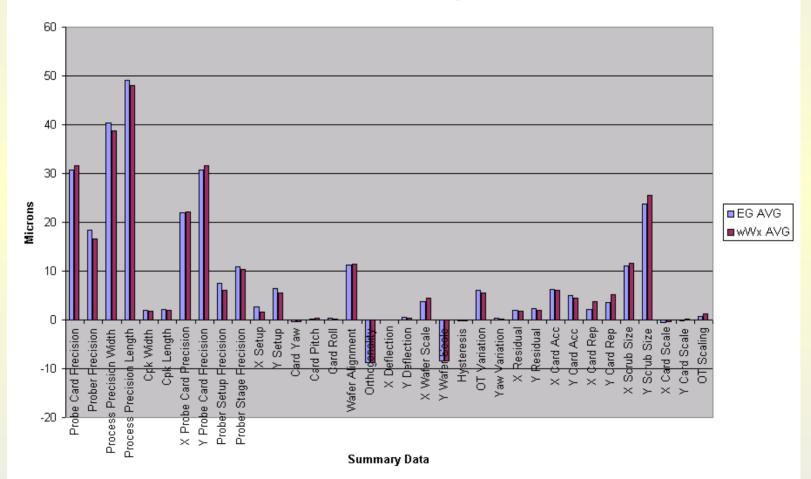

## **Probe Mark Metrology Accuracy**

- Can Data From QuickSilver Be Used?

- QuickSilver tool must supply 46 parameters for each scrub mark with comparable accuracy to waferWoRx

- Validation Study:

- Measure same probed wafer on waferWoRx and QuickSilver systems

- Focus on Repeatability and Reproducibility

- Run PMI results from both tools through waferWoRx analysis algorithms

- Compare results (Report Card format)

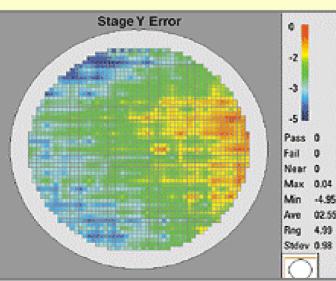

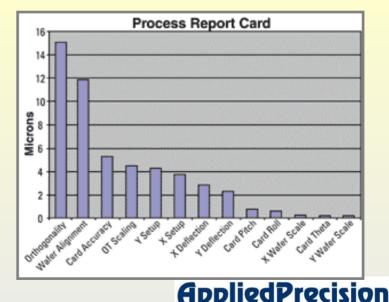

## **Probe Mark Metrology Accuracy**

#### Validation Study Results

**AppliedPrecision** 17 Enabling the world's core technologies

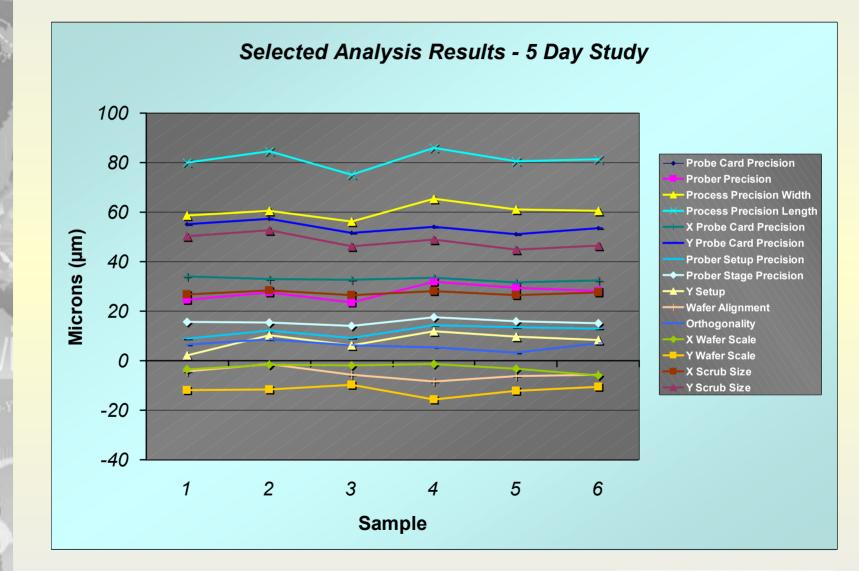

## **Probing Process Variation**

- What Trends Can We Expect?

- Gradual Process Variations

- PTPA drift

- Probe card lifecycle; cleaning, wear, repairs

- Abrupt Events

- Equipment failure

- User intervention

- Fab lot issues

- Validation Study:

- Manually trend data from existing, installed waferWoRx tool:

- Wafers must come from same prober and probe card

## **Probing Process Variation**

**AppliedPrecision** 19 Enabling the world's core technologies

#### Wafer Tracking

- System needs to know which prober and probe card were used on each wafer analyzed:

- Can be obtained through test floor network more desirable

- Can be entered manually by operators less desirable

#### Lag Time

- Process control benefit decreases as Lag Time Increases

- Problems persist while test cell impacts yield

- Sub optimal scheduling of probe card repair increases cost

- Slower time-to-data adds delay to setup validation

- Ways to reduce effects of Lag Time

- Measure probe marks immediately after they're created

- Measure and analyze them quickly

- Allow (and prompt for) job priority scheduling

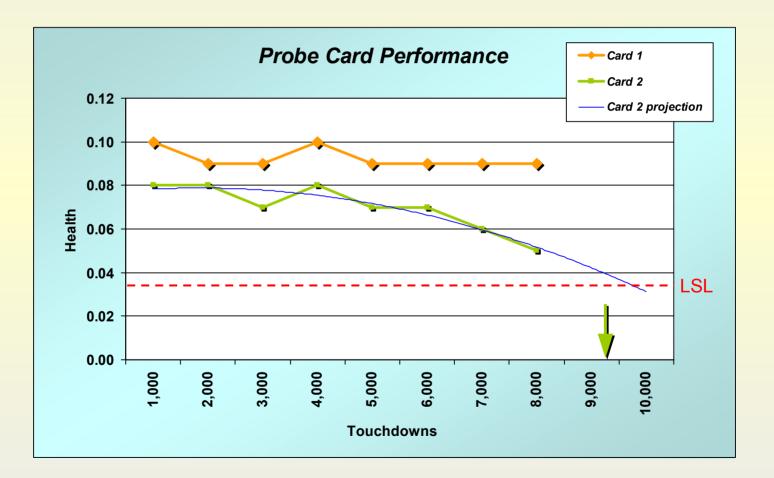

#### Prober Networking and Trend Prediction

#### In-Situ PMI Analysis

- Best way to defeat lag time is to monitor while probing:

- Cannot reduce test cell throughput too costly

- How to do this on a prober without affecting wafer throughput? No easy solution

- Next best way is to monitor immediately downstream from test cell:

- Must be on production floor

- Minimize operator workload

#### **Conclusions**

## **Conclusions**

- The need for probing process control continues to escalate

- Inline probing process analysis is feasible:

- It leverages proven tools

- It can be combined with inspection for added value

- Benefits:

- Data when you need it where you need it

- Higher test cell utilization

- Higher yield

## **Acknowledgements**

- The following contributors helped make this presentation possible:

- Jim Andersen Applied Precision

- Jon Heine Applied Precision

- Jeff Hintzke Electroglas

- Darren James Electroglas

- John Goulding Consultant