#### **Scanimetrics Inc.**

Edmonton, Alberta, CANADA

www.scanimetrics.com

Chris Sellathamby, Ph.D.

Director of Engineering

Keith Brown, Ph.D.Steven Slupsky, M.Sc.Brian MooreMEMS EngineerChief Executive OfficerCo-Founder

June 9, 2004

## Outline

Objectives

1

- Wafer Probe Overview

- Wireless Wafer Probe

- Results

- Applications

- Future Work

- Summary

#### Objectives

Non-contact wafer probing

- Eliminate scrubbing issues

- Increase reliability, reduce maintenance

- Increase yield (front-end and back-end)

- High speeds (Gbps) with high pin counts

- Maintain signal integrity

- Improve price/performance

- Maintain compatibility with existing equipment and processes

- Enable transition to full wafer probing

- Hybrid approach for high power devices

#### Wafer Probe Overview

Limitations

- Support for increased parallelism

- High contact forces reduce yield

- High frequency testing at high pin counts

- Reliability (up to 10% retest)

- Automated manufacturability (manual assembly required)

- Maintenance and cleaning of probe cards

- Probing chips made with new materials (e.g. low-k dielectrics)

- Scaling as pad pitch and size decreases

- Eliminates contact force and scrubbing issues

- Increased test speeds (Gbps) at high pin counts

- Good signal integrity

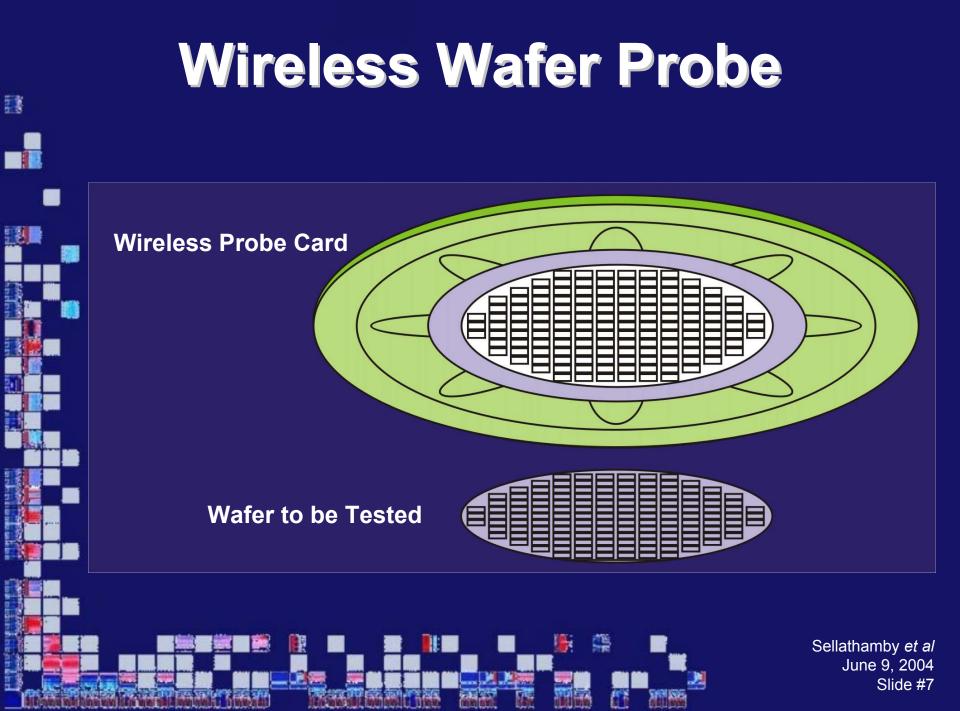

- Enables increased parallelism up to full wafer probing

- Automatic alignment capability with less alignment accuracy requirements

- Significantly reduces need for re-test

- Supports internal test points with no ESD protection requirements (less chip real estate usage)

- Compatible with existing equipment and processes

- Capability to work with new materials (low-k dielectrics)

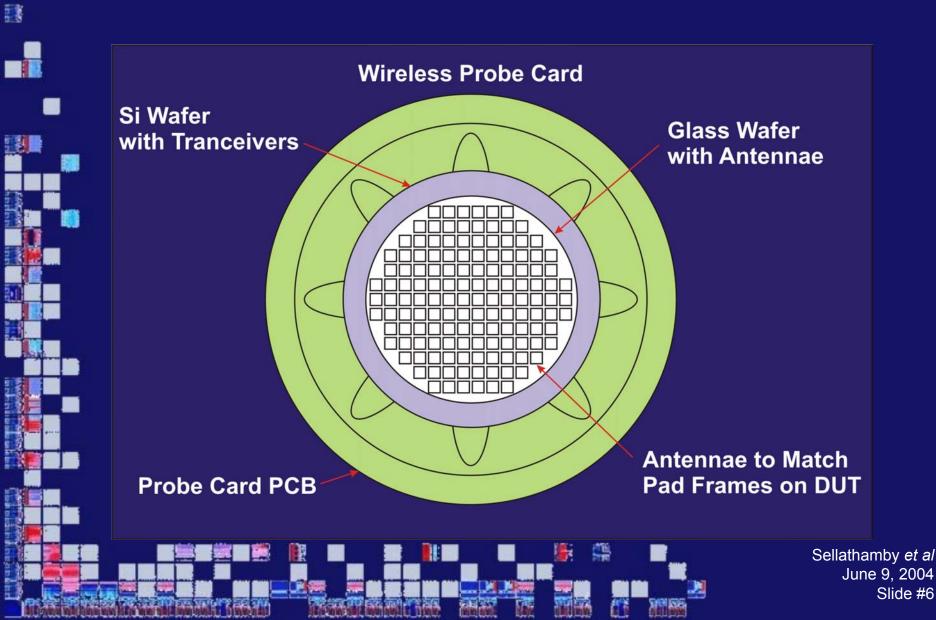

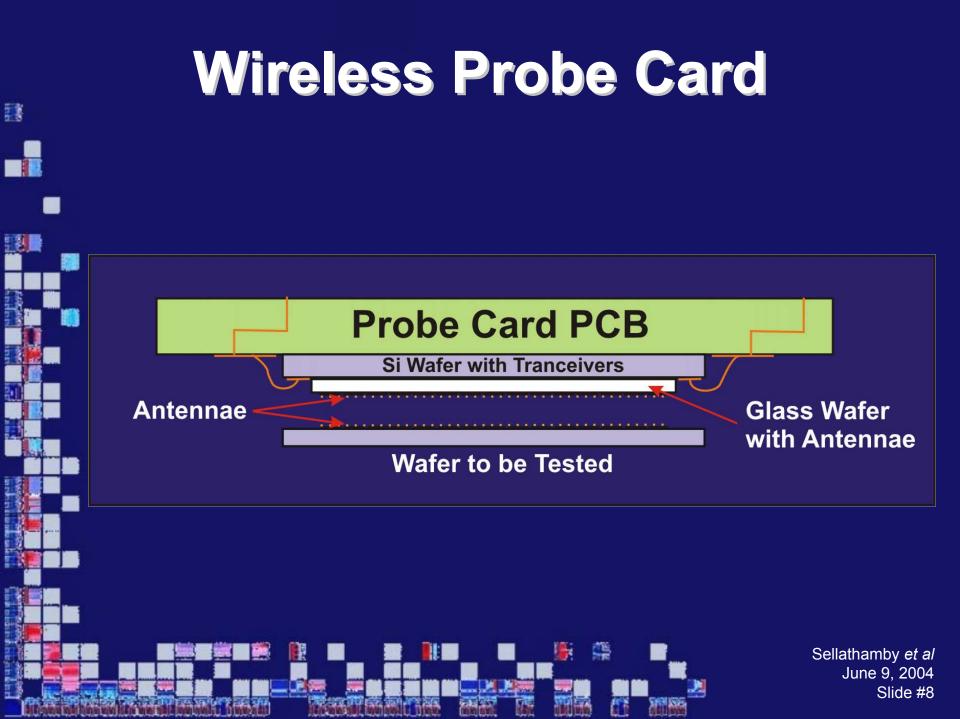

#### **Wireless Probe Card**

#### **Wireless Probe Card** = **Single DUT Die Matching Antenna** with Standard I/O **Pattern on Wireless Cells Replaced with Probe Card** Wireless I/O Cells

#### **Wireless Probe Card**

Specifications

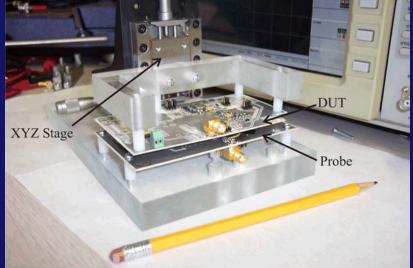

- Probe separation distance < 100 μm</li>

- Antennae for data communications

- Separate antennae for power transfer

- Bi-directional communication at Gbps

- Power delivery of few hundred mW per pin

- Probe pitch scales down to 35  $\mu m$

- Performance Impact

- Power to transceivers disabled after test

- Single transistor loading per I/O site

#### **Wireless Probe Card**

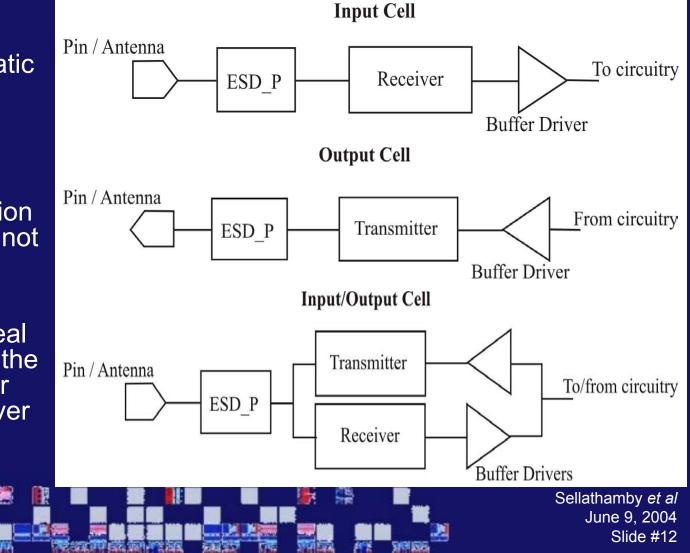

#### Chip Real Estate Required on DUT

1

- Standard I/O cells must be replaced with wireless I/O cells

- No impact on silicon real-estate for devices with pad frames since transceiver circuits are embedded beneath the bond pad

- Power rectification circuitry is also embedded beneath bond pads and connects to existing power bus

- Minimal routing required for enabling transceiver circuits

- Solder bump technology requires 60 µm x 60 µm area per pad for transceiver circuits

ESD\_P is electro-static discharge protection

Clocked transmission gates are not shown

Minimal real estate for the transmitter and receiver circuitry

- Hybrid Solution for High Power Devices

- Contact probes for power

1

- Wireless probes for data

- Redundancy of power pins in hybrid solution eliminates need for multiple touchdowns

- Hybrid approach uses silicon micromachined probes

50 µm features

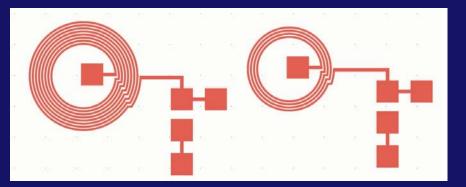

- Frequencies in the range 0.5 1 GHz

- Near-field coupling

- Power delivery through antenna

- Powered up electronics on DUT

- Transmitted sideband signals to probe

- CMOS compatible

Aluminum 0.53µm Borosilicate glass substrate

Aluminum 0.53μm Thermal Silicon dioxide (1.6 μm) Silicon substrate

Overall antenna dimensions: ~2800 to 3500 µm

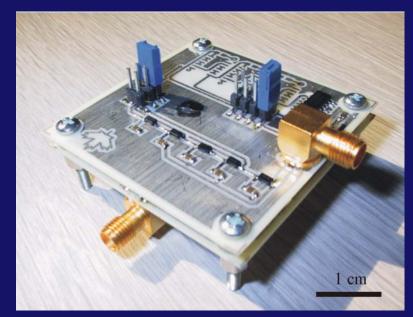

- *P<sub>in</sub>* (min) is 12.7 dBm or 1.15 V<sub>CC</sub>

- Antenna die mounted on RF PCB

- 3.3V CMOS components on PCB

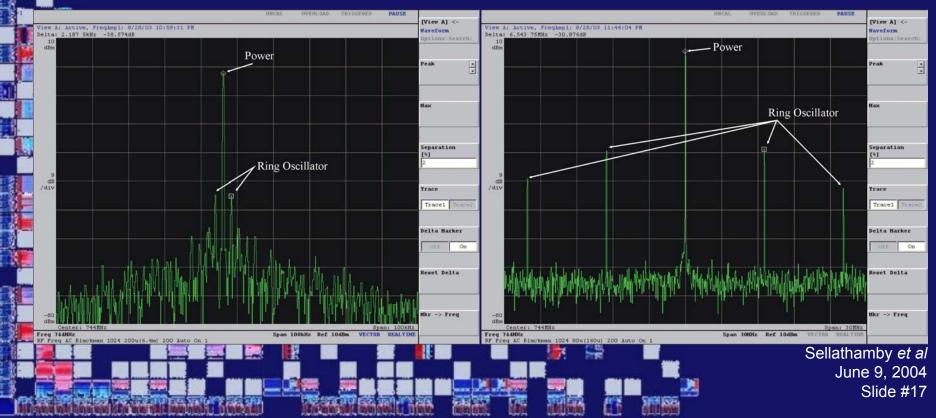

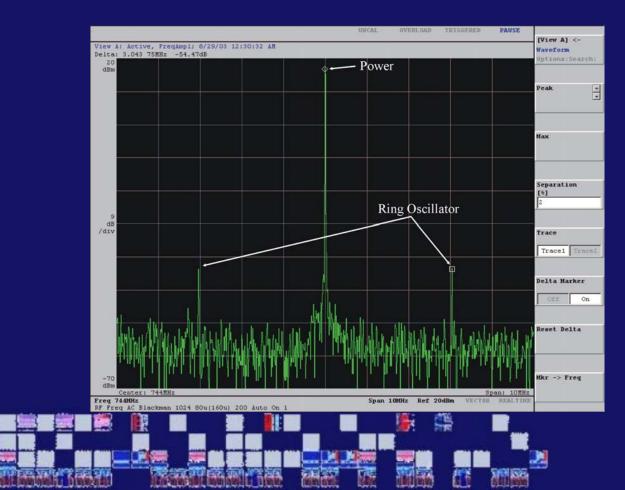

Left figure: turn on of ring oscillator (12.7 dBm)

- Right figure: ring oscillator at full operation (20.0 dBm)

- Ring oscillator frequency proportional to VCC

- Centre freq = 744 MHz, Sidebands at +/- 3.0 MHz

- Ring oscillator signal transmitted back to probe

- Sidebands 15 20 dB above ambient

1

- Reduced antenna size by up to 28x

- Antenna feature sizes of 5 μm

- Antenna dimensions of 100 1000 μm

- Demonstrated that technology can be scaled

- Created elementary I, O, and I/O cells for demonstration

- Demonstrated bi-directional data communication with multiple antennae

- Demonstrated power transfer to DUT

1

- Proved that cell-to-cell interference is not an issue

- Demonstrated that there is no interference with nearby electronic circuitry

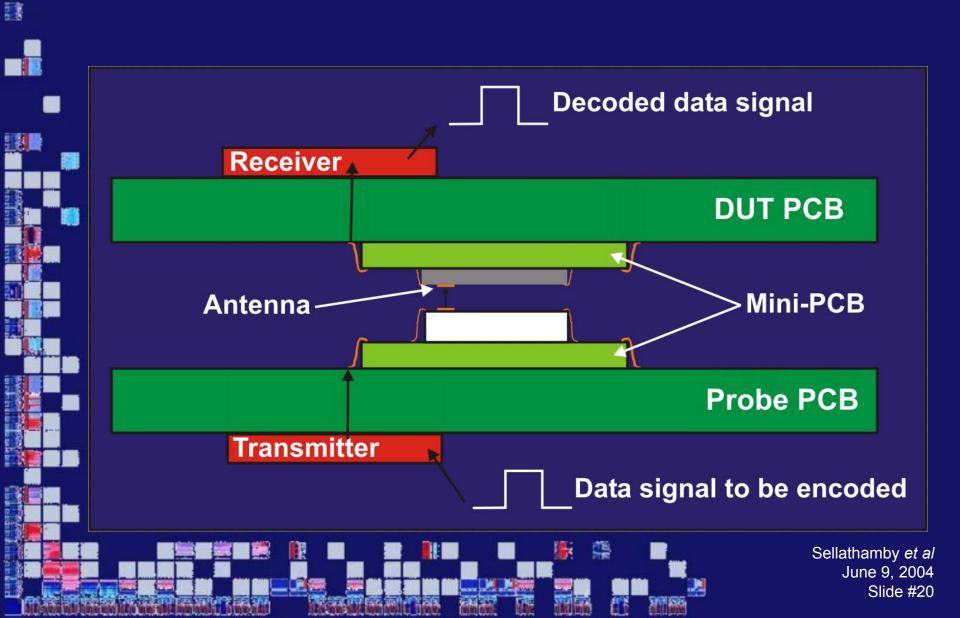

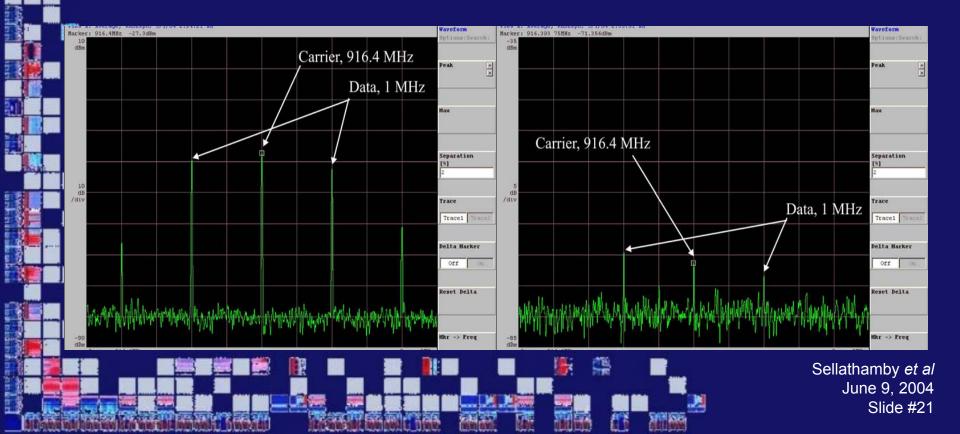

- Amplitude modulated: 916 MHz carrier, 1 MHz data

- Left figure: transmitted spectrum from probe

- Right figure: received spectrum at DUT

- Initially multiple receivers detected single transmitter

- Interference eliminated by:

1

- Reducing transmit power to 1 μW for data channels

- Reducing receiver sensitivity

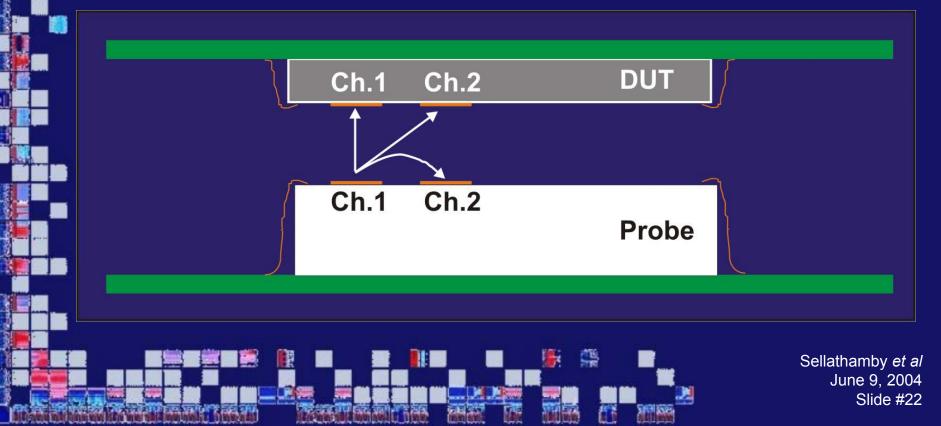

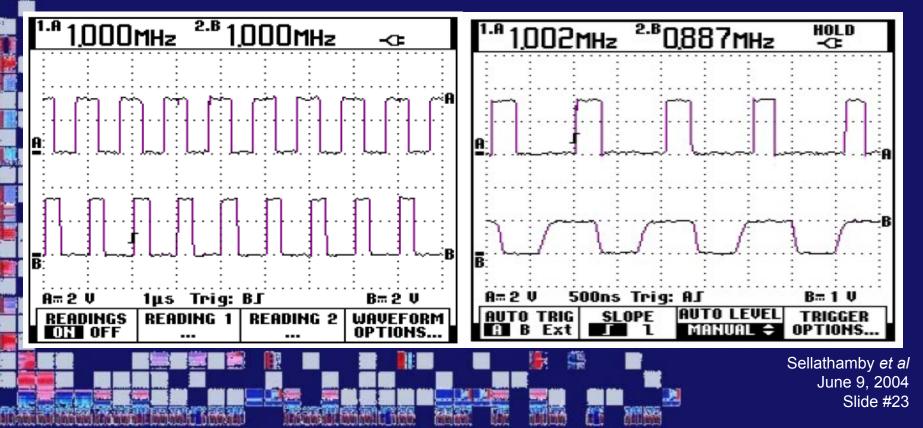

• Simultaneous data Tx, Rx, and power with four separate antennae

- Top left waveform: 1 MHz data signal before modulation and transmit

- Bottom left & top right waveform: 1 MHz demodulated signal at DUT

- Bottom right waveform: ring oscillator on DUT wirelessly powered

Power transfer > 30 mW per antenna at 15% efficiency

1

- Signal transmission power levels less than 1 µW

- Separation distance between probe and DUT of 200 µm

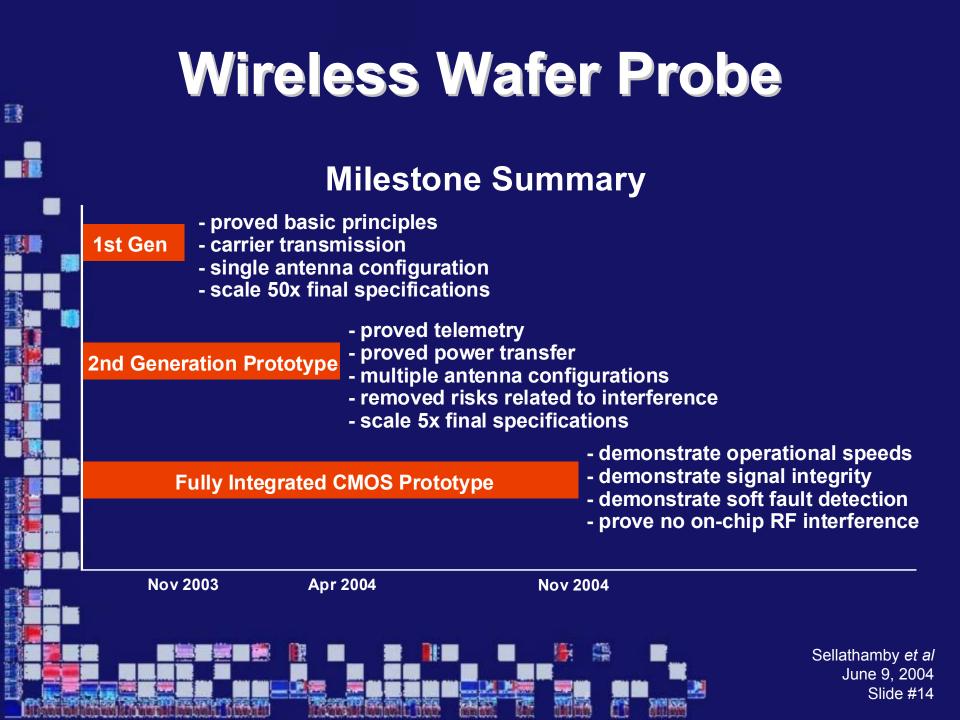

#### Technology Risks Addressed

– Scaling risk:

- Proved signal I/O down to 100 μm

- Extrapolation of results confirm scaling to 35 µm pads

#### - Real estate:

- Simulated transmitter circuits in 0.18 μm (30 μm x 30 μm)

- Designing receiver circuits in 0.18 μm (30 μm x 60 μm)

- Simulated performance of 1 Gbps data rates

- Power delivery:

- Proved power delivery using 300 µm antennae

- RF interference:

- Proved pad to pad interference is minimal & manageable

- Data transmit power reduced to microwatts eliminating radiation effects on circuit function and performance

- Technology Risks Being Addressed

- Signal integrity

- Clock delivery and/or recovery

- Soft fault detection (parametrics)

- Effects of the wireless I/O cells after wafer probe (loading effects)

- Performance of contact probes in a hybrid solution used for high power devices

# Applications

- Wafer probe / Functional Test

- PCM / E-Test / Parametric Test

- Chip-Scale Communications

- Inter-die communication

- Intra-die communication

- Die-to-PCB communication

- Wireless Buses

Probing of Mixed Signal Systems

## **Future Work**

#### Third Generation Prototype

- Timeframe: November 2004

- Fully integrated CMOS design (TSMC 0.18 μm)

- Reduce antenna size by an additional 2x

- Antenna feature sizes of 1 μm

- Antenna dimensions of 50 100 μm

- Demonstrate that the technology can be integrated into an existing CMOS IC I/O cell

- Prove that RF signals do no effect on-chip performance

- Demonstrate that signal integrity at test speeds is maintained

- Demonstrate soft fault detection techniques

#### Summary

- Fundamentally new technology for wafer probe and other applications

- First two prototypes have proved and verified technology

- Design of fully integrated CMOS prototype is underway

- Enables full wafer probing

Significant benefits contributing to increased throughput and increased yield

# **Acknowledgements**

University of Alberta

#### **Scanimetrics Inc.**

Suite 3057 (RTF), 8308 – 114 Street Edmonton, Alberta, CANADA T6G 2E1 Phone: 780.433.9441 Fax: 780.988.1558 www.scanimetrics.com info@scanimetrics.com