#### Pintail Technologies, Inc.

#### **Meeting the New Challenges of Test**

#### Southwest Test Workshop

June 8, 2005 www.pintail.com Micky Ray Program Manager micky.ray@pintail.com

### What are the challenges?

- Cost of test is too high

- Statistical Process Control (SPC) sampling

- Reduce re-test, scrap, yield losses via monitoring

- Zero defects initiatives

- Part Average Testing (PAT) outlier removal

- Improve DPM and ensure reliability

- Parts are getting more complex

- ATE companies struggle to lower capital costs

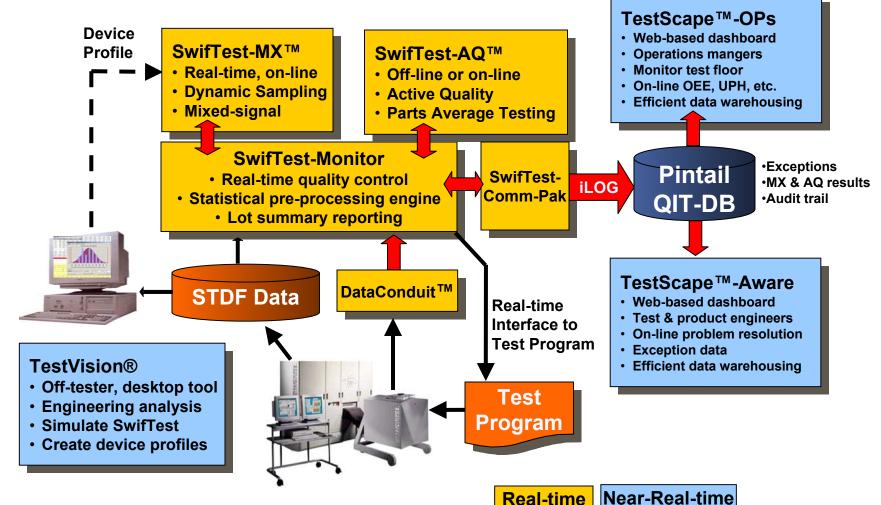

## **Real-time Software Solutions**

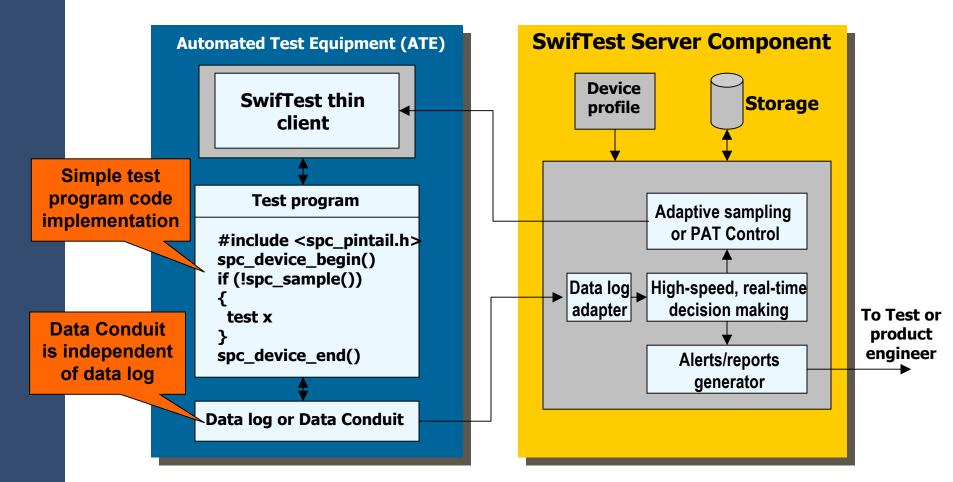

# **Client/Server Design**

All statistical processing done during Index time

# **Real-time Monitoring**

- A real-time data capture and analysis tool

- Monitors the test process

- Thresholds, triggers, alerts, actions

- Prerequisite for sampling and PAT

- Runs on the ATE or on a server

- Written in Java for portability

- Data conduit streams data to monitoring engine

- Very small footprint (minimum CPU, memory & disk)

- Independent of ATE data log

- Data port for optional TestScape DBMS

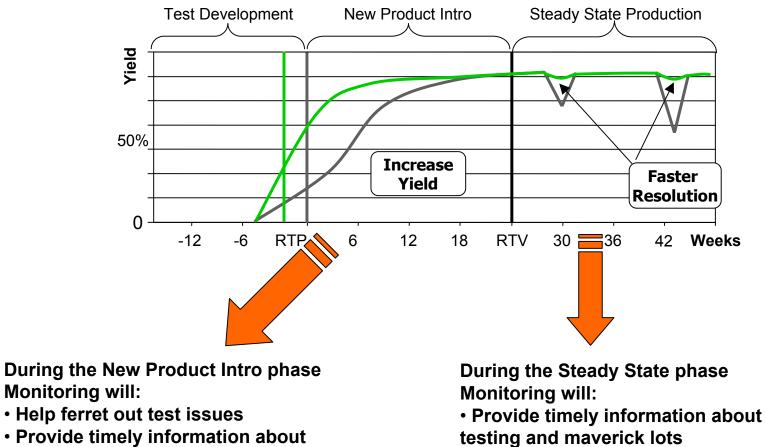

# **Real-time Monitoring**

Reduce re-test and scrap

Monitor OEE

- Provide timely information about testing

- Reduce re-test and scrap

Slide 6

# **Real-Time Sampling**

- Real-time statistical sampling works!

- Proven in production by major IDMs & Fabless users

- Works at **both** probe and final test

- Supports single and multi-site configurations

- Dramatically reduces test time

- Assures highest quality standards

Slide 7

## **Test Program Preparation**

- Add skip code to test program

- Check for dependencies

```

/* add img_skip function for each TESTF selected for sampling */

TESTF MyTest_A()

{

if (! img_skip())

{

/* do regular test processing */

}

```

## Validation: Fabless User

- Major Fabless vendor of wireless devices

- Real-time sampling at wafer test

- <u>35%</u> test time reduction (TTR) per device

- <u>30%</u> throughput increase

- No impact on ATE performance

- No impact on quality

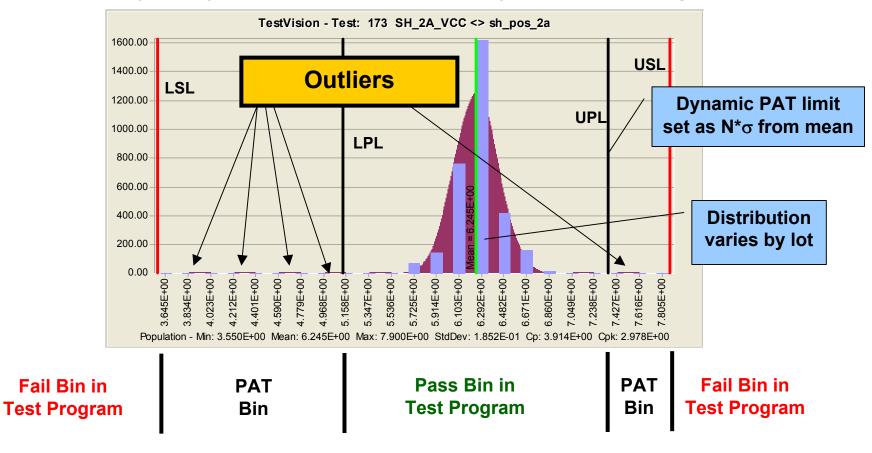

# **Real-Time PAT**

#### Real-time PAT works!

- Dynamic outlier detection and removal

- Parts Average Testing (PAT) is a technique endorsed by the Automotive Electronics Council (AEC) for reducing DPM

- Goal = zero Defects Per Million (DPM)

- Real-time PAT per AEC-Q001 at *both* wafer probe and final test

- Typical yield loss is 0.5% to 1.5%

# **Dynamic PAT Binning**

#### Reject any parts that behave differently than their siblings

Slide 11

# **Dynamic PAT Features**

- User configurable parameters

- Handles non-normal distributions

- Dynamic PAT limits calculated at baseline using mean +/-(n\*sigma) defined by user

- Simple test program binning preparation

- PAT binning applied in real-time

- Unique "outlier" software and hardware bin

- Works at probe or package test

- No test time overhead

- Outlier count trigger

- PAT outlier summary report

#### **Test Program Preparation**

#### SEQUENCER voltage tests() { seq MyTest B

\$20 "%.3f v" > (patLsl(20, 3.500)) < (patUsl(20, 7.500)) "Test 20" f(2); \$21 "%.3f v" > (patLsl(21, 3.500)) < (patUsl(21, 7.500)) "Test 21" f(2); \$22 "%.3f v" > (patLsl(22, 3.500)) < (patUsl(22, 7.500)) "Test\_22" f(2);

Simple PAT test limit and **binning entries**

No test flow changes

No correlation required

# Validation: Major IDM

- Major supplier of automotive devices

- Real-time PAT at package test

- <u>0.8%</u> average yield loss

- <u>1.0</u> DPM

- No impact on ATE performance

# Summary

- Real-time sampling can significantly lower the test time and increase throughput without sacrificing quality.

- Real-time PAT can remove outliers from the population and significantly lower the DPM with minimal yield loss.