#### **IEEE SW Test Workshop** Semiconductor Wafer Test Workshop

Jim Brandes Everett Charles Technologies

# High-Performance Contactors for Wafer-Scale Test (WST)

## Agenda

- Traditional Test Approach Probe and Final (Package) Test

- New Method Final Test on Wafer – Economic Advantages – Understanding Wafer-Scale Test

Wafer-Scale Test Vs. Wafer Probe – Mechanical Challenges

- -Electrical Challenges

## Agenda

- New-Generation Spring Probes for WST

Electrical and Mechanical Characteristics

- New Generation Probes Compared to Existing Probe Technologies for WST

- Traditional Spring Pin

- Cantilever Beam

- Buckling Beam

- Membrane

# **Traditional Test Approach**

## Wafer Probe / Final Test

- Wafer Probe

- Cannot be a complete and thorough test

- Confirms device functionality

- Final (Package) Test

- Performed at device specification limits

- Confirms performance with packaging effects included

June 8 to 11, 2008

## New Method – Final Test on Wafer Wafer-Scale Test (WST)

**IEEE SW T**

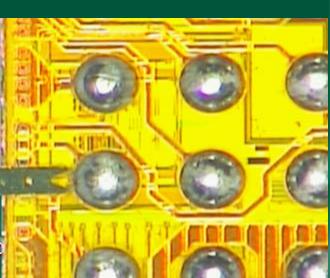

- Packaging at wafer level allows testing at wafer level

- Redistribution layer with ball or bump attach

- Ready to be diced, boxed and shipped after test

## New Method – Final Test on Wafer

#### **Economic Advantages**

- Testing traditionally >10% of cost of device manufacture

- Testing once rather than twice has potential to halve this

- Improved possibilities of parallelism

- Shorter time to market

June 8 to 11, 2008

#### **Understanding Wafer-Scale Test**

## Wafer-Scale Test is mechanically similar to probe test

## Wafer-Scale Test must be identical electrically to package test

June 8 to 11, 2008

WST vs. Wafer probe WST Mechanically Similar to Wafer Probe

• Devices still part of wafer

Wafer prober used to manipulate devices for test

June 8 to 11, 2008

### WST vs. Wafer probe

#### Wafer-Scale Test /S Final Test

- DC tests

- High current

- Accurate force, measure values

- Functional tests

- Drive inputs at thresholds

- Sense outputs at limits & under loads

- Power supplies at minimum / maximum

June 8 to 11, 2008

### WST vs. Wafer probe

#### Wafer-Scale Test /S Final Test

Timing / AC tests

Full clock speed

Worst-case input timing combinations

Confirming input-to-output timing

RF tests (gain, SNR, THD, etc.)

Requires clean power delivery

Low inductance

June 8 to 11, 2008

### WST vs. Wafer Probe

#### **WST Challenges - Mechanical**

- Fine-pitch requirements

- Currently at 0.4 and 0.3 mm pitch

- 0.25 mm and smaller soon

- Vertical Contact

- Support for area arrays

- Support for high parallelism

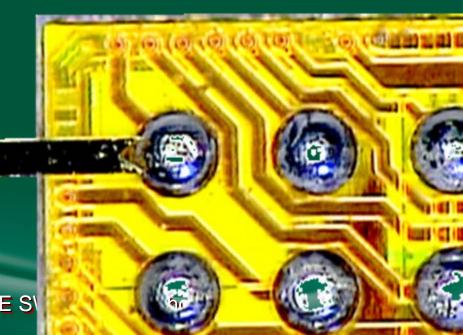

- Adequate force requirements

- More force required than wafer probe

- 20 g 30 g to pierce solder oxide and debris

June 8 to 11, 2008

## WST vs. Wafer Probe

## WST Challenges - Mechanical

- Compliance

- Bumped wafers not as coplanar as wafer pads

- Cleaning

- Abrasive scrub for cantilever probe not appropriate

- New cleaning techniques required

- Stack height

- Probers not capable of plunging to board

- Additional height diminishes performance

June 8 to 11, 2008

### WST vs. Wafer Probe

### **WST Challenges - Electrical**

- High current requirements

- Low, consistent resistance

- Low inductance requirements

- High bandwidth requirements

- Everything that is required for final test

June 8 to 11, 2008

**New-Generation Spring Pins Meet All the Requirements New Architecture Spring Probes** -Electrical performance -Mechanical performance -Cost-effective manufacturing method

June 8 to 11, 2008

**New Architecture**

-Single-ended

- Two flat pieces and spring

- No barrel

- All external surfaces allow excellent plating quality and consistency

- Scalable architecture suitable for 0.2 mm and below

**High Electrical Performance** -Short, wide signal paths -High bandwidth -Low, consistent resistance -High Conductance -Low inductance

High Mechanical Performance –Short probe length –Good force –High compliance –Long life

June 8 to 11, 2008

**IEEE SW Test Wo**

#### **Cost-Effective Probe**

- -Fewer probe parts

- -Lower cost than turned parts

- Better plating improves manufacturing yield

- Easier assembly

- Individually

Replaceable

#### Sample Specifications: RF / Electrical

|                                        | 0.4 mm             | 0.3 mm            |

|----------------------------------------|--------------------|-------------------|

| Bandwidth                              | 25.8 GHz @ -1 dB*  | 12.4 GHz @ -1 dB* |

| Loop Inductance                        | 0.91 nH*           | 1.12 nH*          |

| <b>Continuous Current</b>              | 1.2 A @ 20° C rise | TBD               |

|                                        | 1.7 A @ 40° C rise | TBD               |

| Current @ 1% duty cycle                | 7.7 A @ 20° C rise | TBD               |

| * Native pitch, GSG, Vespel dielectric |                    |                   |

June 8 to 11, 2008

**New-Architecture Probe Sample Specifications: Mechanical**

**Test Height** Compliance **DUT-Side Compliance Force @ Test Height Typical Life** Finish (Plating)

**0.4** mm 2.40 mm (0.094") 0.64 mm (0.025") 0.5 mm (0.020") **30 g** 500 k cycles\* Hard Gold, others pending

\* Lab tests

0.5 mm 2.73 mm (0.106") 0.64 mm (0.025") 0.5 mm (0.020") **25 g** 500 k cycles\*

June 8 to 11, 2008

Advantages over traditional spring probes for WST:

- Lower inductance

- Higher bandwidth

- Higher Force

Traditional spring probes for WST are about equal:

- Fine Pitch capability

- Vertical Architecture

- Conductance

- Compliance

- Repairable in the field

- Price

June 8 to 11, 2008

#### New-Architecture Probe Advantages over traditional cantilever-beam probes for WST:

- Vertical architecture for area arrays and higher parallelism

- Greater compliance

- Higher currents

- Lower inductance

- Higher bandwidth

- Higher force

- Field repairable / rebuildable without special tools

June 8 to 11, 2008

**New-Architecture Probe** Advantages of traditional cantilever-beam probes for WST: Fine pitch capability **About Equal:** • Price

June 8 to 11, 2008

### **New-Architecture Probe**

Advantages over buckling-beam probes for WST:

- Greater compliance

- Higher currents

- Lower inductance

- Higher bandwidth

- Higher force

- Lower price

- Field repairable / rebuildable without special tools

June 8 to 11, 2008

Equal:

IEEE SW Test Workshop

**New-Architecture Probe**

Advantages of buckling-beam

probes for WST:

Finer pitch capability

Vertical architecture

Advantages over membrane probes for WST:

- Greater compliance

- Higher currents

- Lower inductance

- Lower price / shorter leadtime

- Field repairable / rebuildable without special tools

June 8 to 11, 2008

Advantages of membrane probes for WST:

- Fine pitch capability

- Close position of decoupling

- About equal:

- Bandwidth

- Vertical architecture

June 8 to 11, 2008

#### **New-Architecture Probe Initiating Beta Sites** Primary considerations •First-pass yield Final yield •Probe life Overall cost of test Secondary considerations Cleaning frequency

•Ease of maintenance / use

#### **Future**

IEEE

Highly scalable architecture

Probes designed for:

0.2 mm pitch

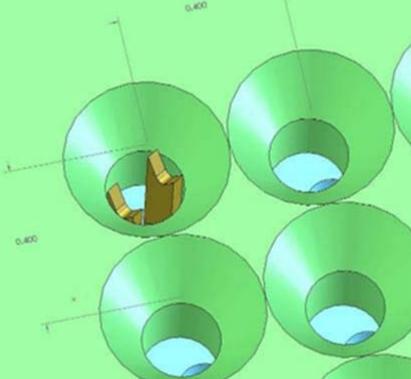

Kelvin for

0.4 mm Arrays

0.4 mm pitch Kelvin probe tips shown, viewed through floating alignment plate

June 8 to 11, 2008

### Summary

New-technology probes are designed to be used in contactors to address:

- Mechanical requirements of WST

- Electrical requirements of WST

- Demand for reduced cost of test

Thank You Questions?

June 8 to 11, 2008