**IEEE SW Test Workshop** Semiconductor Wafer Test Workshop

Chris Sellathamby, J. Hintzke, B. Moore, S. Slupsky Scanimetrics Inc.

#### Non-contact Test at Advanced Process Nodes

June 8-11, 2008 San Diego, CA USA

- Advanced CMOS nodes are a challenge for wafer testing

- Very fine pitch, ultra-low-k dielectrics, non-AI metallization

- Advanced package and interconnect technologies make traditional wafer testing impossible

- New package and interconnect technologies e.g. thru-Si vias

- Proximity chip-to-chip communications

- Optical interconnects do not have bond pads or bumps

- Non-contact testing techniques can be used to overcome these advanced node testing issues

- Data is presented confirming exceedingly low error rates and wide mechanical alignment tolerances for DC to GHz signals

## Outline

- Advanced node wafer testing challenges

- Non-contact communication technology

- Applications and update

- Results from 45nm test chip

- Summary

June 8 to 11, 2008

#### **Advanced Node Testing Issues**

- New materials

- Pad and dielectric damage

- Pad pitch

- New interconnect technologies w/o bond pads

- Thru-silicon vias

- Redistributed Chip Packaging (RCP)

- Proximity communication

- System-in-Package (SiP) has no BIST or DFT

- Test blindness since internal nodes are hidden

SiP and SoC

June 8 to 11, 2008

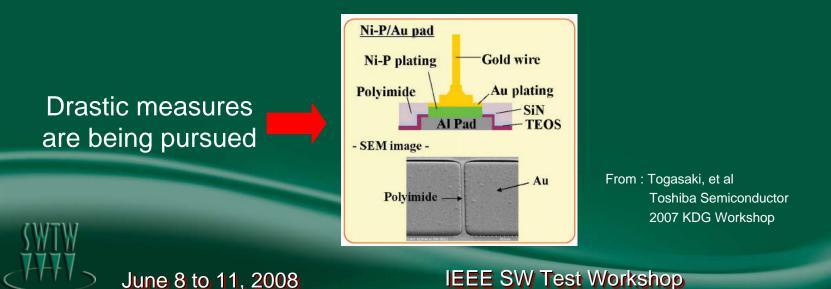

## **New Materials Issues**

- At advanced nodes, ultra-low-k dielectrics and very thin layers cause major issues with conventional wafer probing

- The metal stack is "spongy"

- The metal layers are thin

- Probe needles "tear" the bond pads

- Gate dielectrics are "ultra-thin" (~10Å)

- Stress on the die causes dielectric cracking

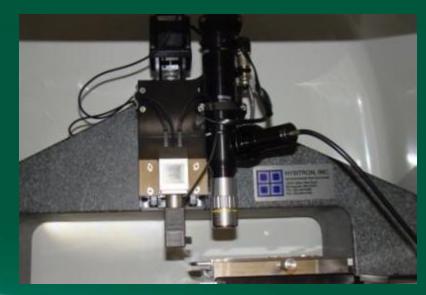

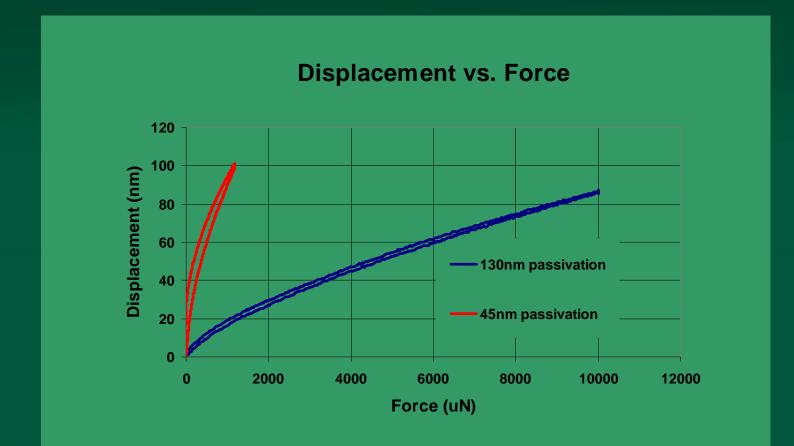

#### New Materials Issues Nano-indenter bond pad measurements

June 8 to 11, 2008

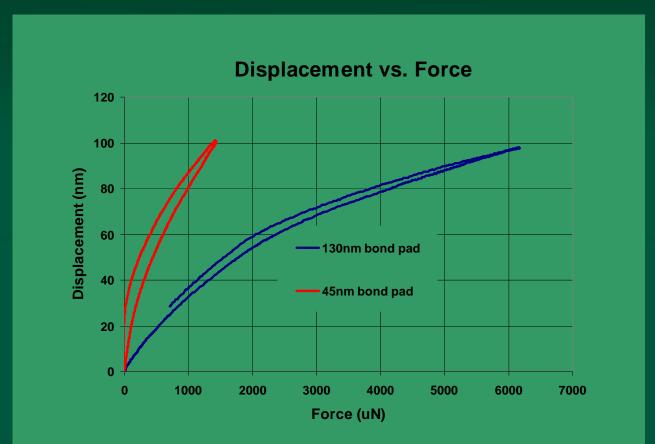

#### **New Materials Issues**

Force is 5x less for advanced process nodes

June 8 to 11, 2008

#### **New Materials Issues**

Force is 10x less for advanced process nodes

SWTW

June 8 to 11, 2008

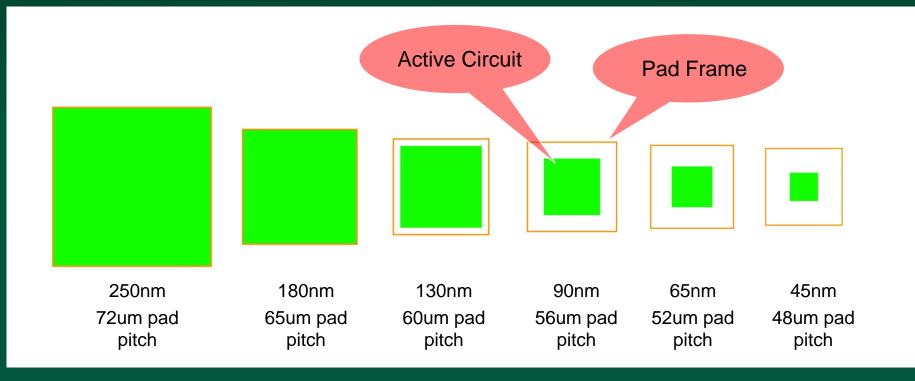

## **Pad Pitch Problem**

#### 2006 ITRS for Test

|                                  |      | Tab   | le 38a | ı Waj | fer Pro | obe Teo | chnolo | gy Req | uirem | ents—i | Near-t | erm Ye | ars <mark>U</mark> | PDATE | ED   |       |      |       |

|----------------------------------|------|-------|--------|-------|---------|---------|--------|--------|-------|--------|--------|--------|--------------------|-------|------|-------|------|-------|

| Year of<br>Production            | 2005 |       | 2005   |       | 2007    |         | 2008   |        | 2009  |        | 2010   |        | 2011               |       | 2012 |       | 2013 |       |

| DRAM ½ Pitch<br>(nm) (contacted) | 80   |       | 70     |       | ಪ       |         | 57     |        | 50    |        | 45     |        | 40                 |       | 36   |       | 32   |       |

| 1/O Pad Size<br>(µm)             | х    | Y     | х      | Y     | x       | Y       | ×      | т      | x     | Y      | х      | Ŷ      | х                  | Y     | x    | т     | ×    | Y     |

| Wirebond                         | 35   | 60    | 30     | 55    | 30      | 55      | 25     | 45     | 25    | 45     | 25     | 45     | 25                 | 45    | 20   | 35    | 20   | 35    |

| Bump                             | 75   | 75    | 75     | 75    | 60      | 60      | 60     | 60     | 50    | 50     | 50     | 50     | 50                 | 50    | 50   | 50    | 50   | 50    |

| Scrub (% of I/O)                 | AREA | DEPTH | AREA   | DEPTH | AREA    | DEPTH   | AREA   | DEPTH  | AREA  | DEPTH  | AREA   | DEPTH  | AREA               | DEPTH | AREA | DEPTH | AREA | DEPTH |

| Wirebond                         | 25   | 50    | 25     | 50    | 25      | 50      | 20     | 40     | 20    | 40     | 20     | 40     | 20                 | 40    | 20   | 40    | 20   | 40    |

| Bump                             | 30   | 30    | 30     | 30    | 30      | 30      | 30     | 30     | 30    | 30     | 30     | 30     | 30                 | 30    | 30   | 30    | 30   | 30    |

Bond / probe pads are not shrinking with circuit ightarrowdimensions

- Probes

- Pitch, tip size

- Pad Damage

- Maximum allowable damaged area

- ESD Structures

June 8 to 11, 2008

### White Space Dilemma

White space is often filled with "non-value added circuitry"

June 8 to 11, 2008

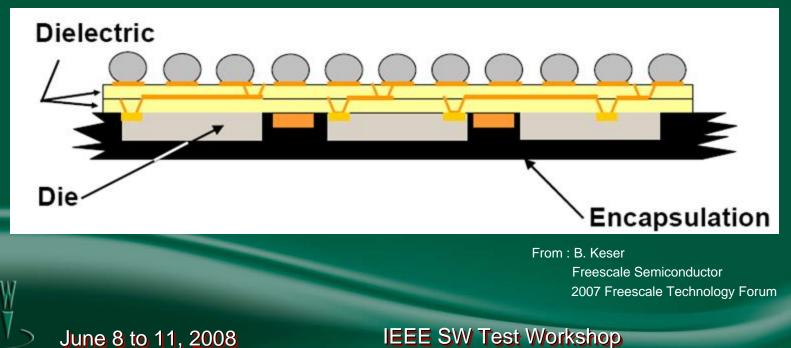

#### **New Interconnect Technologies**

- Redistributed Chip Packaging (RCP)

- Die connections are redistributed and brought to the outside as part of the package build

- No pads needed on the die

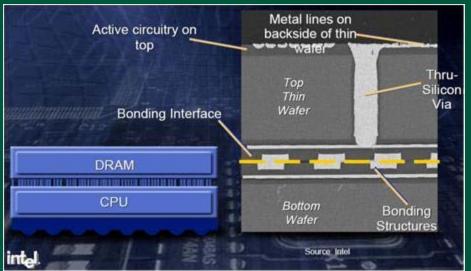

## **New Interconnect Technologies**

#### • Thru-Si vias

– No need for pads

#### - Stacked memories, Memory to processor

From : Fraunhofer Inst. 2005 RTI Conference

From : TM Mak Intel 2005 Ga Tech 3S Workshop

June 8 to 11, 2008

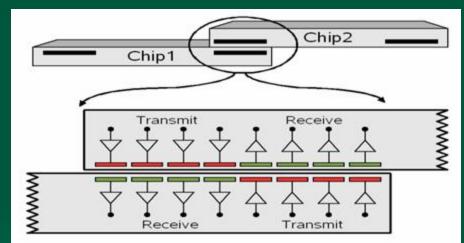

#### **New Interconnect Technologies**

- Proximity Chip-to-Chip communications

- No bond pads required

- Capacitive, inductive and optical

- Non-contact, very high speed chip-to-chip communications programs in development for I/O

- Sun Microsystems, Intel, STMicro, HP, many others

From : A. Fazzi; et.al. ST Microsystems 2007 ISSCC

From : D. Hopkins; et al Sun Microsystems 2007 ISSCC

June 8 to 11, 2008

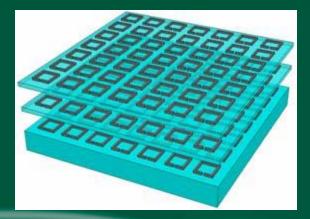

## Non-contact Communication Technology

- Wireless, chip-scale communications

- Distances < 100 µm</li>

- Pitch scales to < 20 μm</li>

- Micro Tx/Rx on chip

- One Tx/Rx per I/O

- Fully CMOS compatible

- No impact on real-estate for most applications

- Excellent data integrity with low power

- Power transfer also possible

June 8 to 11, 2008

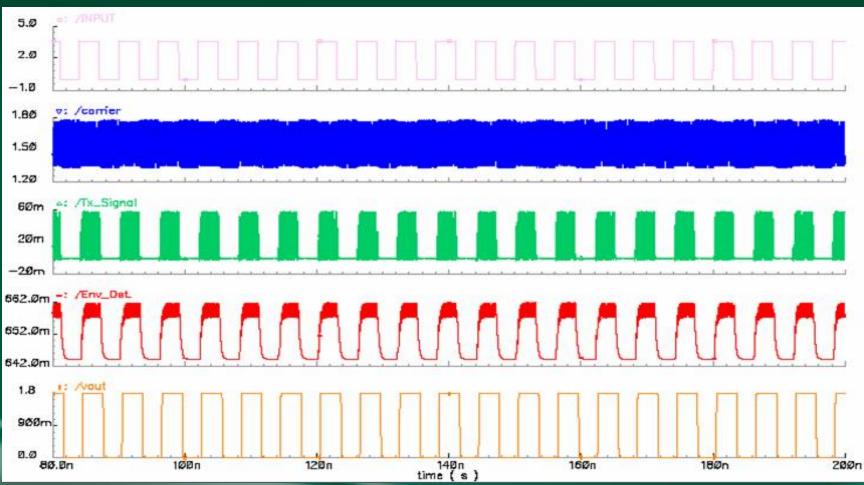

## **Signal Modeling**

June 8 to 11, 2008

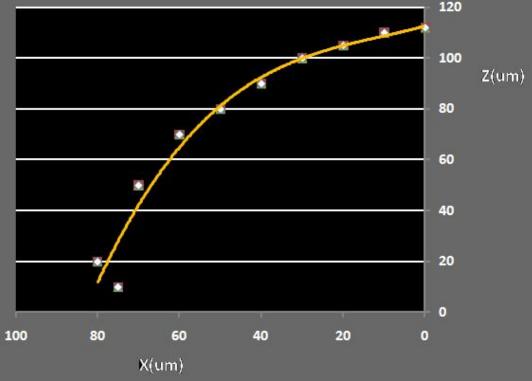

# **Alignment Tolerance**

- Wide alignment tolerance

- 120um antennas

- Envelope of <10<sup>-13</sup>

bit error rate

### System Spatial Response

June 8 to 11, 2008

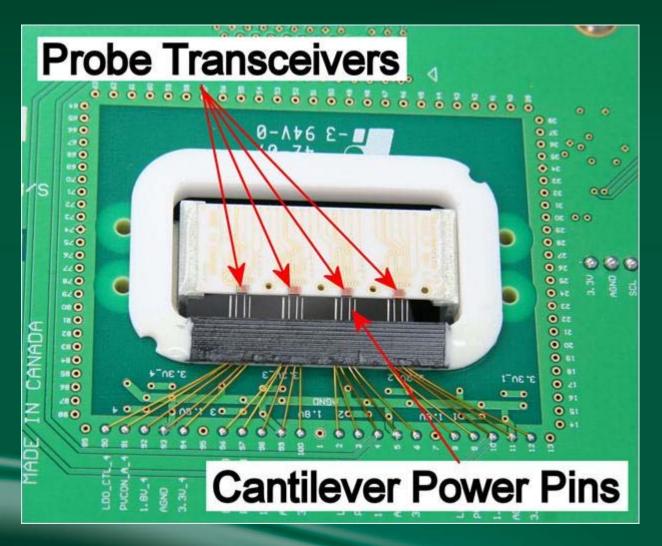

# **SiP Testing Application**

- Wireless Test Access Port (WiTAP<sup>™</sup>)

- A chip with Scanimetrics' wireless transceivers designed to be integrated into the SiP/MCM

- Allows testing of the SiP like a wafer during the assembly process

- On a prober, with a probecard

- Enables more complex SiP devices

- Lessens KGD requirements

June 8 to 11, 2008

# **SiP Testing Application**

Can be Implemented as an independent chip populated on the SiP substrate or as an IP block embedded in other chips

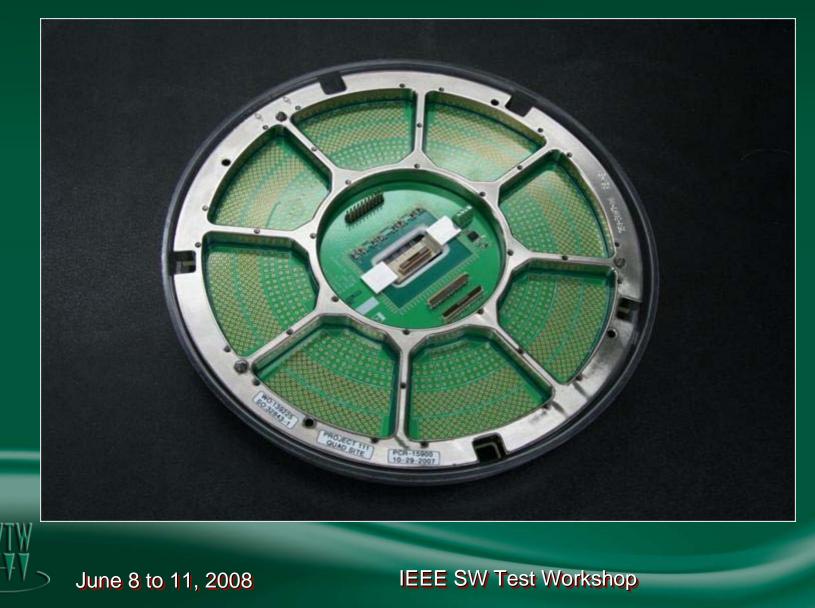

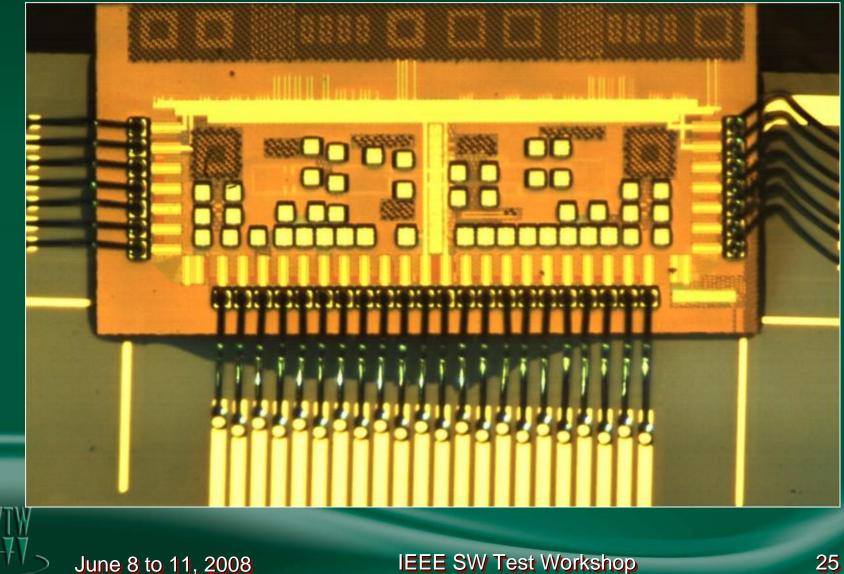

## **Probecard - Top View**

### **Probecard – Bottom View**

June 8 to 11, 2008

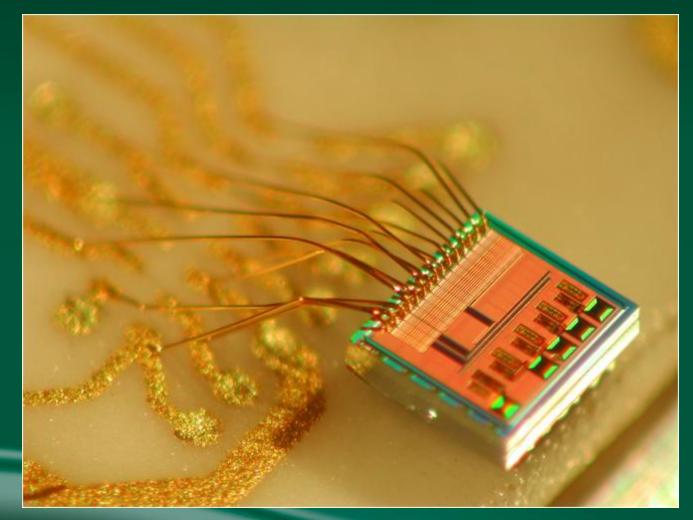

## Single probe

June 8 to 11, 2008

## **Actual SiP Implementation**

WITAPTM

# **SiP Testing Summary**

- Successfully run JTAG tests wirelessly on individual chips

- Verigy (Agilent) 93k tester

- EG4090 prober

- Built quad-site hybrid probe card

- Preparing for production qualification on customer's pilot line

- 16 chips in fabrication with enhancements and customer specific requirements

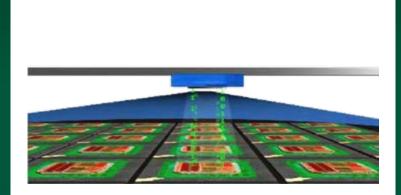

## **Wafer Probe Application**

- Reduces contact force and scrubbing issues

- Probe pitch scales with process node

- Capability to work with new materials (low-k dielectrics)

- Interfaces can be tested at full functional speed at the wafer level (SerDes, DDR2, DDR3)

- Simpler mechanical designs

- Automatic alignment capability with lower alignment accuracy requirements

- Supports internal test points with no ESD protection requirements

- Compatible with existing equipment and processes

June 8 to 11, 2008

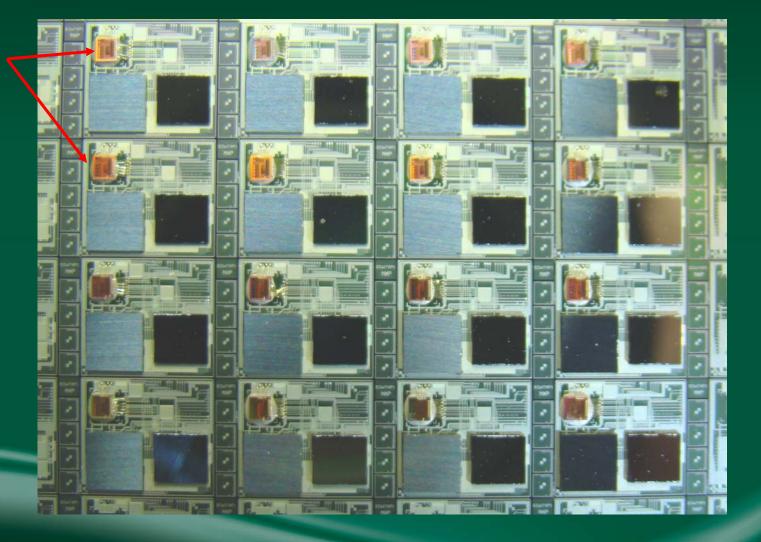

## **CMOS 45nm Test Chip**

June 8 to 11, 2008

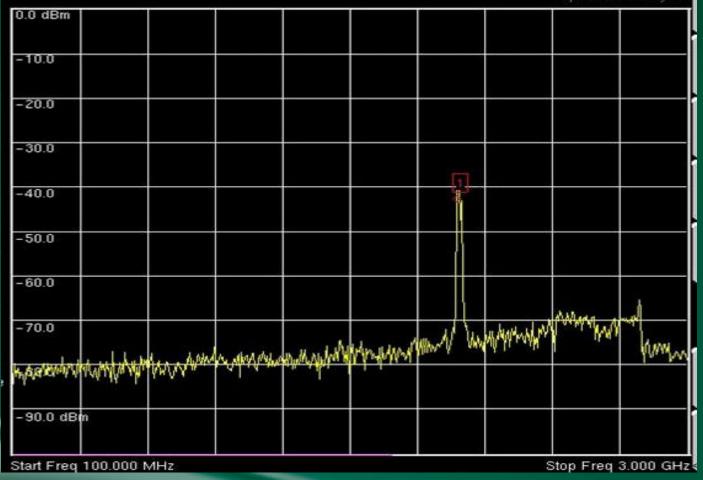

## **Micro-watt GHz Carriers**

Spectrum Analyzer

June 8 to 11, 2008

## **45nm Testing Summary**

- Migrated technology to customer's 45 nm process

- Increased non-contact data rate capabilities > 1 Gbps

- Reduced pitch to 30 µm

- Reduced power consumption of transceiver circuits by 10x

- Integrating circuits into customer's I/O

cells

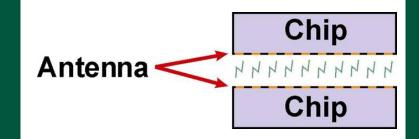

## **Interconnect Application**

- Test interface also used for chip-to-chip communication

- Transceiver IP block replaces bond pads, ESD structures and I/O drivers

- Capable of very high speed date rates (multi Gbps)

- Lower power consumption

June 8 to 11, 2008

IEEE SW Test Workshop

**Play Animation**

## Summary

- New testing techniques are required for advanced process nodes

- New testing techniques are required for new chip-to-chip interconnect methods

- Robust data transfer of wireless channels demonstrated at 45 nm node

- Non-contact wafer test products can be used in SiP and chip-to-chip interconnect applications as well

### Thanks

Contact the Scanimetrics team with any questions ...

Chris Sellathamby, Ph.D. VP Engineering csellathamby@scanimetrics.com

Steve Slupsky CEO sslupsky@scanimetrics.com Jeff Hintzke Dir. of Marketing jhintzke@scanimetrics.com

Brian Moore Director R&D bmoore@scanimetrics.com

June 8 to 11, 2008