IEEE SW Test Workshop Semiconductor Wafer Test Workshop

S.Dharmarajan Mike Goode Cadence Design Systems

## Accelerating CAD design of Probe Cards using Allegro System Architect

## June 8-11, 2008 San Diego, CA USA

# Topics

- About this paper

- Background

- Desired Goals

- How Allegro System Architect is different

- Results

- Strengths/ Weaknesses

- Summary / Conclusion

- Follow-up

## **About this Paper**

## Target Audience

Designers / Managers / Influencers associated with design of probe cards

## • What is in it for you

knowledge about a solution which can accelerate design of probe cards significantly

June 8 to 11, 2008

## Background

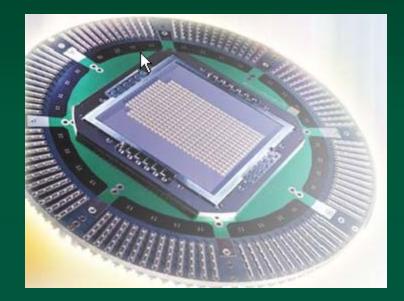

## • Probe cards

- Test multiple identical devices

- More constraints

- Larger sizes

- Handling component changes

June 8 to 11, 2008

# **Key Design Challenges**

## Symmetry

- The devices are identical

- But instances and nets need to be named uniquely – following a pattern

## Constraints

- Matched delays for groups/buses

- Total delay constraints

- Differential pairs

- Terminations

June 8 to 11, 2008

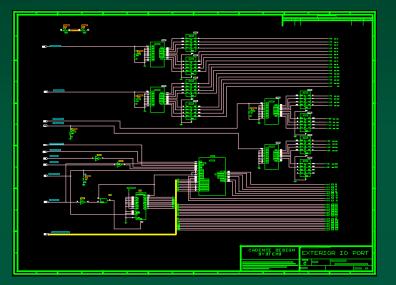

# **Current Solutions (1)**

- Schematic based solutions

- Easily understandable for small designs

- Problems

- Difficult to scale for size / number

- Time consuming top create

- Handling change is tedious

- Connectivity is "layout driven"; not just logic driven

June 8 to 11, 2008

# **Current Solutions (2)**

Custom Excel based solutions – Quick and Customized Problems Need maintenance - Typically handle only netlists – no constraints – can't handle change

| 98456   |           |                         |             |         |          |            |                          |

|---------|-----------|-------------------------|-------------|---------|----------|------------|--------------------------|

| 30430   | DIE (um)  | •                       | SCRIBE (um) | -       | STEP(um) |            | STEP(mils)               |

| ×       | 6284.0R   |                         | 146.00      | -       | 6430.0   |            | 253.15                   |

| Ŷ       | 5148.0    |                         | 92.00       | -       | 5240.0   |            | 206.30                   |

| 1 ·     | 0140.00   | 52.22 Kmil <sup>2</sup> |             |         |          |            |                          |

| PAD     | SIZE (um) |                         | PAD SIZE (m | ils)    |          | PITCH (um) |                          |

| 1112    |           | 2.99                    |             |         |          |            |                          |

|         | 76.00     | -                       |             | 1       |          | 121.60     |                          |

| 1       |           |                         | Pad         | HP      | Wire Pad |            |                          |

| Die Pad | X coord   | Y coord                 | Function    | Channel | Name     |            | uble Wide Bonding Pads ? |

| 1       | 116.210   | 96,190                  | VSS         | VSS     | VSS      | DUTA       |                          |

| 2       | 104.448   | 96,190                  | AESD(16)    | 18      | 18       | DUTA       |                          |

| 3       | 99,606    | 96,190                  | AESD(22)    | 24      | 24       | DUTA       |                          |

| 4       | 94.763    | 96,190                  | AESD(21)    | 23      | 23       | DUTA       |                          |

| 5       | 89.921    | 96,190                  | AESD(15)    | 17      | 17       | DUTA       |                          |

| 6       | 79.246    | 96,190                  | AESD(14)    | 15      | 15       | DUTA       |                          |

| 7       | 74.404    | 96,190                  | AESD(13)    | 14      | 14       | DUTA       |                          |

| 8       | 69.561    | 96,190                  | AESD(12)    | 13      | 13       | DUTA       |                          |

| 9       | 64.719    | 96,190                  | AESD(11)    | 12      | 12       | DUTA       |                          |

| 10      | 59.876    | 96,190                  | AESD(10)    | 11      | 11       | DUTA       |                          |

| 11      | 48.332    | 96,190                  | AESD(9)     | 10      | 10       | DUTA       |                          |

| 12      | 43.490    | 96,190                  | AESD(8)     | 9       | 9        | DUTA       |                          |

| 13      | 38.647    | 96,190                  | AESD(19)    | 21      | 21       | DUTA       |                          |

| 14      | 33.805    | 96,190                  | VPBESD      | 16      | 16       | DUTA       |                          |

| 15      | 28.962    | 96,190                  | AVDBESD     | 28      | 28       | DUTA       |                          |

| 16      | 23.736    | 96,190                  | VCC         | VCC1A   | VCC1A    | DUTA       |                          |

| 17      | 17.592    | 96,190                  | VSS         | VSS     | VSS      | DUTA       |                          |

| 18      | 5.998     | 96,190                  | CEBESD      | 27      | 27       | DUTA       |                          |

| 19      | -31.094   | 96,190                  | RSTBESD     | 29      | 29       | DUTA       |                          |

| 20      | -36.646   | 96,190                  | ACCESD      | VPP1    | VPP1     | DUTA       |                          |

| 21      | -47.680   | 96,190                  | VEBESD      | 30      | 30       | DUTA       |                          |

| 22      | -53,436   | 96,190                  | AESD(23)    | 25      | 25       | DUTA       |                          |

| 23      | -64.129   | 96,190                  | AESD(20)    | 22      | 22       | DUTA       |                          |

| 24      | -68.972   | 96,190                  | AESD(18)    | 20      | 20       | DUTA       |                          |

| 25      | -73.814   | 96,190                  | AESD(17)    | 19      | 19       | DUTA       |                          |

| 26      | -78.657   | 96,190                  | AESD(7)     | 8       | 8        | DUTA       |                          |

| 27      | -83,499   | 96,190                  | AESD(6)     | 7       | 7        | DUTA       |                          |

| 28      | -94.791   | 96,190                  | AESD(5)     | 6       | 6        | DUTA       |                          |

| 29      | -99.633   | 96,190                  | AESD(4)     | 5       | 5        | DUTA       |                          |

| 30      | -104.476  | 96,190                  | AESD(3)     | 4       | 4        | DUTA       |                          |

| 31      | -114.647  | 96,190                  | VCC         | VCC1A   | VCC1A    | DUTA       |                          |

| 32      | -108.207  | -94,439                 | RDY         | 26      | 26       | DUTA       |                          |

| 33      | -99.935   | -94.439                 | 10(0)       | 1       | 1        | DUTA       |                          |

| 24      | 91662     | 04.420                  | 10(9)       | ٩       | ٩        | ПИТА       |                          |

# The underlying problem

Why do current solutions break

- A large amount of data is being manipulated

- Can't handle patterns or replication natively

- Graphics based netlisters but graphics dont add value

- connectivity is driven back to front!

June 8 to 11, 2008

# Spreadsheet Editor for design creation

#### Spreadsheet Editor for connectivity

### Key Components

Component and Signals in tabular / spreadsheet like views

|        |        | Comp   | ionent List |            | 1                     |   |         |            | Signa   | al Connectiv | /ity Details |       |          |        |          |

|--------|--------|--------|-------------|------------|-----------------------|---|---------|------------|---------|--------------|--------------|-------|----------|--------|----------|

| Ð      | Ins    | Ref    | Cell        | i          |                       |   |         |            |         |              |              |       |          |        |          |

| *      | *      | *      | *           | *          |                       |   | 10_175  |            |         |              |              |       |          |        |          |

|        | AP     |        | apu         |            |                       |   |         | L          | In-(n   | Pin Name     | Die blueben  | D:- T | <b>T</b> | . 達 #. | A        |

|        | AP     |        | apu         |            | =                     |   | Cell    | Instance V | Ref Des |              | Pin Number   | J     |          |        | <u> </u> |

|        | но     |        | host        |            | _                     |   | *       | *          | *       | *            | *            | *     | *        | * *    |          |

|        | i1     | P12    | pwrlug_6    |            |                       |   | vhdm_f  | i30        | J4      | b16          | B16          | Inout |          |        |          |

| Sam.   | i2     | P16    | pwrlug_6    |            |                       |   | vhdm_f  | i30        | J4      | b17          | B17          | Inout |          |        |          |

|        | i3     | P17    | pwrlug_6    |            |                       |   | vhdm_f  | i30        | J4      | f1           | F1           | Inout |          |        |          |

| 5      | i4     | P19    | pwrlug_6    |            |                       |   | vhdm_f  | i29        | J3      | b16          | B16          | Inout | Series   |        |          |

| Ser.   | i5     | P11    | pwrlug_6    |            |                       |   | vhdm_f  | i29        | J3      | b17          | B17          | Inout |          |        |          |

|        | i6     | P15    | pwrlug_6    |            |                       |   | vhdm_f  | i26        | J1      | b16          | B16          | Inout |          |        |          |

| Ser.   | i7     | P18    | pwrlug_6    |            |                       |   | vhdm_f  | i26        | J1      | b17          | B17          | Inout |          |        |          |

| 5      | i8     | P20    | pwrlug_6    |            |                       |   | host    | HOST_BLADE |         | IO_1V5       |              | Inout |          |        |          |

| Ser.   | i9     | P14    | head3x9     |            |                       |   | apu     | APU2_BLADE |         | IO_1V5       |              | Inout |          |        |          |

| 11 M C | i10    | P13    | head3x9     |            |                       |   | apu     | APU1_BLADE |         | 10_175       |              | Inout |          |        |          |

| Cor.   | i11    | D1     | bss138lt1   |            | <b>~</b>              |   |         |            |         |              |              |       |          |        |          |

|        |        | Sig    | nal List    | ļ          | <b>_</b>              |   |         |            |         |              |              |       |          |        |          |

| т      | Phys I | Name   | Cor         | nn i       | ^                     |   |         |            |         |              |              |       |          |        |          |

| *      | *      |        | *           | *          |                       | • |         |            |         |              |              |       |          |        |          |

| ٩L     | PS2_P  | FAIL   |             | 2          | · 1                   |   |         |            |         |              |              |       |          |        |          |

| њĽ.    | PS2_P  | WRGD   |             | 2          |                       |   |         |            |         |              |              |       |          |        |          |

| ħĿ     | SIGNA  | L_2    |             | 2          |                       |   |         |            |         |              |              |       |          | -      |          |

| ħĹ     | ITP_R  | ESET   |             | 3          |                       |   |         |            |         |              |              |       |          |        |          |

| μĽ     | PS1_I  | NHBT   |             | 3 <b>i</b> |                       |   |         |            |         |              |              |       |          |        |          |

| ħĹ     | AP1_N  | IEMGNT |             | 5          |                       |   |         |            |         |              |              |       |          |        |          |

| ₽G     | +1.65  | W.     |             | 7          |                       |   |         |            |         |              |              |       |          |        |          |

| ₽G     | +5V    |        |             | 8          |                       |   |         |            |         |              |              |       |          |        |          |

| 빝      | IO_1V  | 5      | 1           | 10         |                       |   |         |            |         |              |              |       |          |        |          |

| μĿ     | NC_N1  | T3_RX  | 1           | 17         |                       |   |         |            |         |              |              |       |          |        |          |

| ΈĿ     | NC_N1  | тз_тх  | 1           | 17         |                       |   |         |            |         |              |              |       |          |        |          |

|        | NC_N1  |        |             | 17         |                       |   |         |            |         |              |              |       |          |        |          |

|        | NC_N1  | T4_TX  |             | 17         |                       |   |         |            |         | <u> </u>     |              |       |          |        | ×        |

| ₩G     | +12∀   |        | 2           | 22         | $\mathbf{\mathbf{v}}$ |   | In Sign | nal IO_1V5 |         |              | •            |       |          |        | ►        |

June 8 to 11, 2008

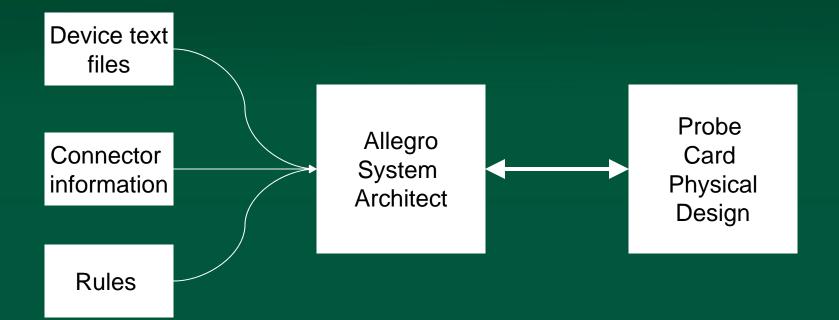

## Technical aspects of Allegro System Architect

- A spreadsheet based editor for design connectivity

- Patterns, copy-paste, sort, filter, find-replace over large amounts of data

- Understands CAD data natively

- Spreadsheet formats allows connectivity to be driven from layout

- Clean access to text imports, exports, differences

June 8 to 11, 2008

# How does a spreadsheet solution help

| Problem                       | Solution                                                   |

|-------------------------------|------------------------------------------------------------|

| Large data sets               | Spreadsheet Editor                                         |

|                               | <ul> <li>No need for symbols</li> </ul>                    |

|                               | <ul> <li>Handle thousands of nets/pins</li> </ul>          |

| Patterns and replication      | Use copy paste, sort, filter find replace                  |

| Layout Driven<br>Connectivity | Can drive connectivity in either direction with equal ease |

| Constraint Management         | Understands CAD data natively                              |

## **Design Flow**

June 8 to 11, 2008

## **Strengths / Weaknesses**

### Strengths

- Spread Editing of Connectivity

- Eco management / speed

- Constraint handling

- Layout driven connectivity

### Weakness's

Documentation schematics are not aesthetic

June 8 to 11, 2008

## **Typical Results**

- Significant Reduction in time especially if using schematic based methods

- Better productivity if constraints need to be managed (for large digital devices)

- Work required to substitute home-grown solutions with this solution

- Gains increase with Volume & design size

Not worth effort for very small / very infrequent designs spins

June 8 to 11, 2008

## **Follow-on**

- Talk to the authors

Mike Goode , mgoode@cadence.com

- Avoid graphics the next time you build a probe card

- Send us questions and comments

June 8 to 11, 2008