**IEEE SW Test Workshop** Semiconductor Wafer Test Workshop

> June 8, 2009 San Diego, CA

### A Challenge of 150k Probes on 300mm

Satoshi Sasaki <sasaki@aset.tokyoinfo.or.jp>

### Yoshiro Nakata

<nakata@aset.tokyoinfo.or.jp>

Chip Test Technology Research Lab.

Association of Super-Advanced Electronics Technologies (ASET)

This work is under NEDO entrustment project.

NEDO [The New Energy and Industrial Technology Development Organization] is Japan's largest public R&D management organization.

## Outline

1. What is ASET 2. Background 3. Target & issue 4. Probe detail 5. Countermeasure 6. Results & field data 7. Summary

## about ASET?

- Association of Super-Advanced Electronics Technologies (ASET) is a consortium making up with Japanese electronics companies.

- Established :1996

- Purpose:

Contribute to the enhancement of the competitiveness of Japanese industry and the establishment of an advanced information society.

• Activities:

Research and develop on industry-wide fundamental technologies in the semiconductor and other advanced electronics technology fields as well as practical applications of research results.

http://www.aset.or.jp/english/e-index.html

**ADVANTEST Corporation DAI NIPPON PRINTING Co., Ltd** Elpida Memory, Inc. FUJITSU Ltd. Hitachi, Ltd. Hitachi High-Technologies Corporation Hitachi Kokusai Electric Inc. **HOYA** Corporation **IBIDEN Co., Ltd. IBM** Japan **Intel Corporation** JEOL Ltd. nac Image Technology Inc. **NEC Corporation NEC Electronics Corporation NIKON Corporation**

### Member Companies

**NIPPON CONTROL SYSTEM Corporation** NuFlare Technology, Inc. **Panasonic Corporation Renesas Technology Corp. ROHM Co., Ltd** SAMSUNG ELECTRONICS Co., Ltd **SHARP** Corporation SHINKO ELECTRIC INDUSTRIES Co., Ltd SII Nano Technology Inc. **TOKYO ELECTRON Ltd. TOPPAN PRINTING Co., Ltd TOSHIBA** Corporation **TOYOTA MOTOR Corporation** ULVAC, Inc. YAMAICHI ELECTRONICS Co., Ltd ZyCube Co., Ltd.

#### **Companies**

Total 32

### Organization

**3D-Integration Technology Research Dept.**

Design Environment Technology Lab. (Tokyo)

6 Companies

Chip Test Technology Lab. (Kawasaki, JAPAN)

ADVANTEST Panasonic SHARP TOKYO ELECTRON YAMAICHI ELECTRONICS

The Univ. of Tokyo Toyama Prefectural Univ.

> 5 Companies/ 2 University

3D-Integration Basic Technology Lab. (Hachioji)

**11** Companies

June 8, 2009

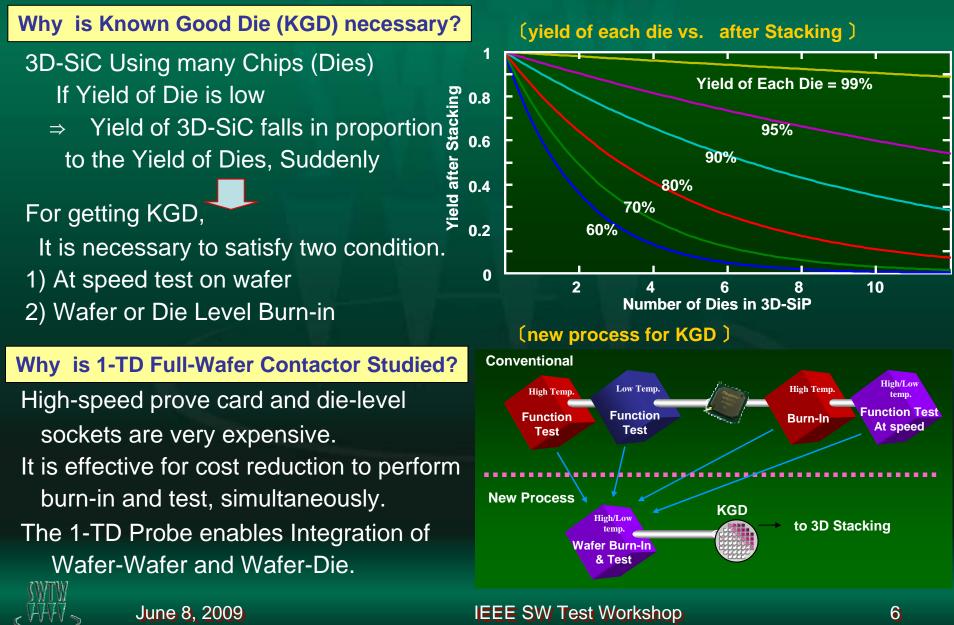

### Background

### **Study about Target Device**

#### The number of pads and Power per one wafer

| Device Type         | Number of   | P/S and grand number/wafer           | Signal numbers/wafer               | Power           |  |

|---------------------|-------------|--------------------------------------|------------------------------------|-----------------|--|

| SoC high end        | 500         | VDD 256 ~ / chip<br>GND 256 ~ / chip | I/O 512 ~ / chip                   | ~ 10kA          |  |

|                     |             | Total 250,000 / wafer                | Total 250,000 / wafer              | ~ 30kW          |  |

| SoC middle<br>class | 1000 ~ 2000 | VDD 100 ~ / chip<br>GND 100 ~ / chip | I/O 256 ~ 512 / chip               | ~ 5kA           |  |

|                     |             | Total 400,000 / wafer                | Total 500,000 / wafer              | ~ 15kW          |  |

| SoC low end         | 3000 ~ 5000 | VDD 50 ~ / chip<br>GND 50 ~ / chip   | I/O 256~ /<br>chip                 | ~ 5kA<br>~ 10kW |  |

|                     |             | Total 500,000 / wafer                | Total 750,000 / wafer              |                 |  |

| DRAM                | 500 ~ 1500  | VDD 25 ~ / chip<br>GND 25 ~ / chip   | Dr. 30 ~ / chip<br>I/O 15 ~ / chip | ~ 300A          |  |

| 1                   |             | Total 75,000 / wafer                 | Total 68,000 /wafer                | ~ 400W          |  |

| Flash memory        | 500 ~ 1500  | VDD 10~ / chip<br>GND 10~ / chip     | Dr. 10 ~ / chip<br>I/O 10~ / chip  | ~ 100A          |  |

|                     |             | Total 30,000 / wafer                 | Total 60,000 /wafer                | ~ 200W          |  |

Source : Prepared by Chip Test Research Laboratory using ITRS's roadmap, etc

It was decided the object device as a memory and SoC less than middle class. And it is clear that number of contact pads have to be reduced.

## **Target of the probe Card**

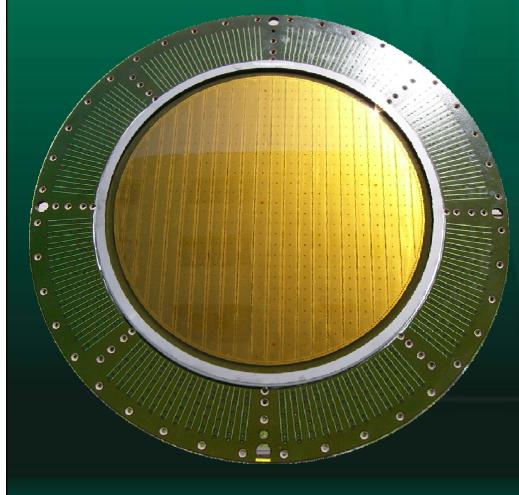

- Wafer Size : 300mm

- Probe Quantity : 150k

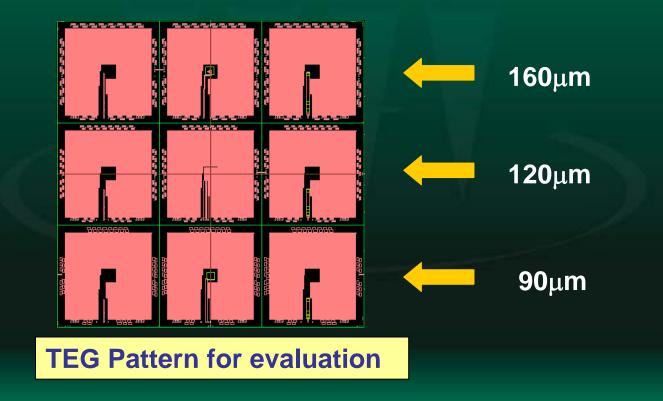

- Pad Size : 60µm

- Pad Pitch :  $min 90\mu m$

- Current : 5kA / wafer

- Power : 15kw / wafer

- Temperature : -40 125 deg. C

### The Issue for 150k contact on 300mm

The total load on 300mm wafer is 7,000N (700 kg) or more

Uniform pressure in the 300mm area

Stable contacts without scrub

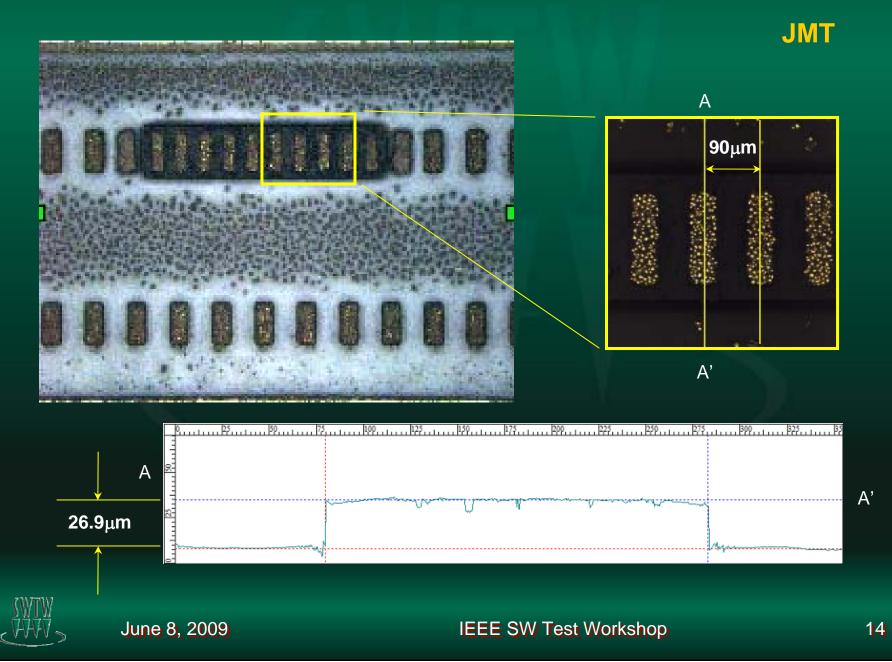

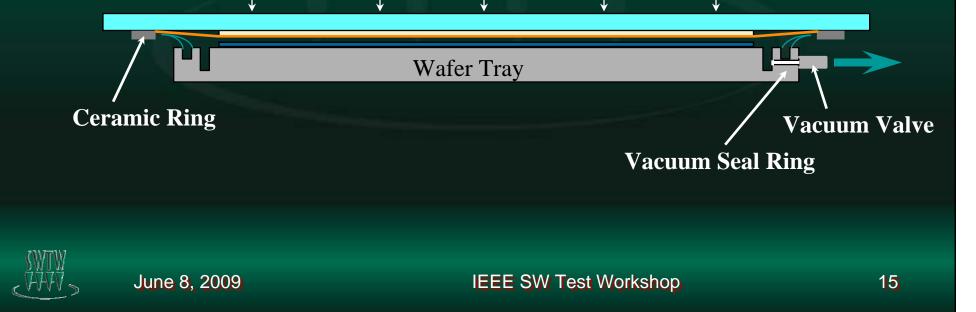

### **150k Probe Card Over View**

For Memory & Logic 150k Bumps Min. Pitch 90µm Membrane with Bumps Pressurization using atmosphere

## **150k Probe Card Detail**

| Pad Pitch | 160µm  | <b>120</b> µm | 90µm   | Total   |

|-----------|--------|---------------|--------|---------|

| Bumps     | 49,147 | 51,322        | 50,114 | 150,583 |

June 8, 2009

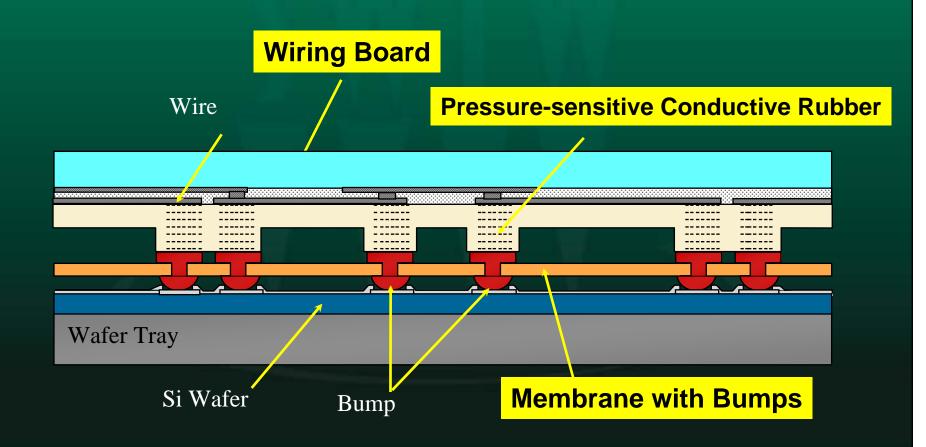

## **Detailed Structure of Probe**

June 8, 2009

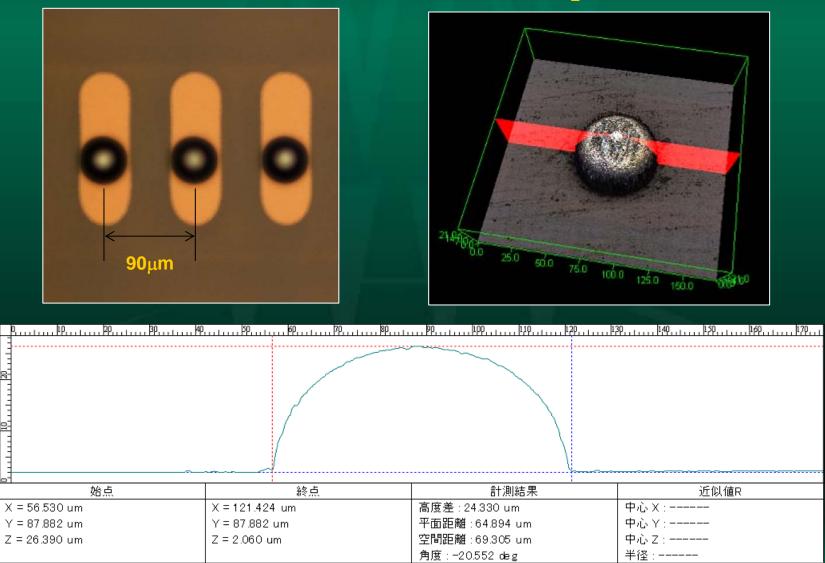

### **Contact Bump**

### **Pressure-sensitive Conductive Rubber**

### **Atmospheric Pressure**

### Total load : 15.3[cm] <sup>2</sup> x $\pi$ x 97[kPa] = 7,129 [N]

### **Alignment Station**

Base Machine : TSK UF300 Max. z-load : 100kg

### **Alignment Station by TSK**

June 8, 2009

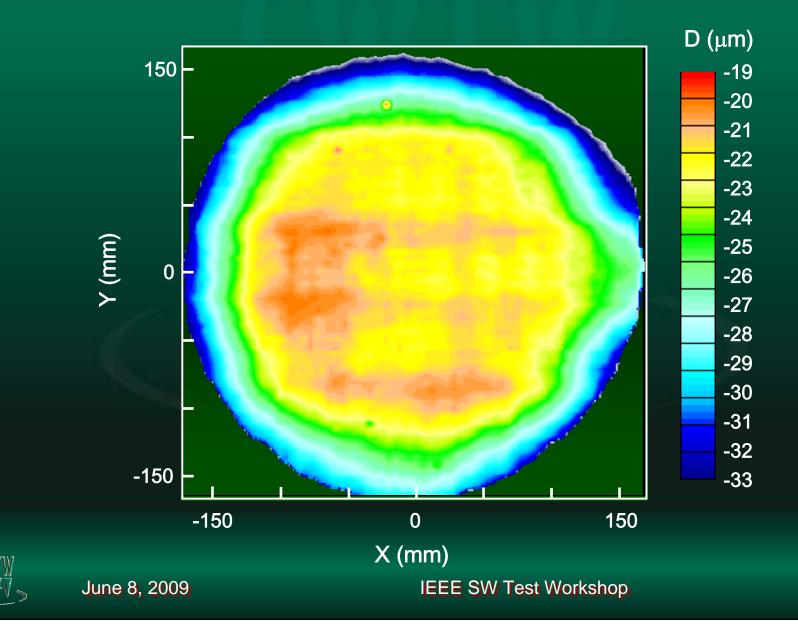

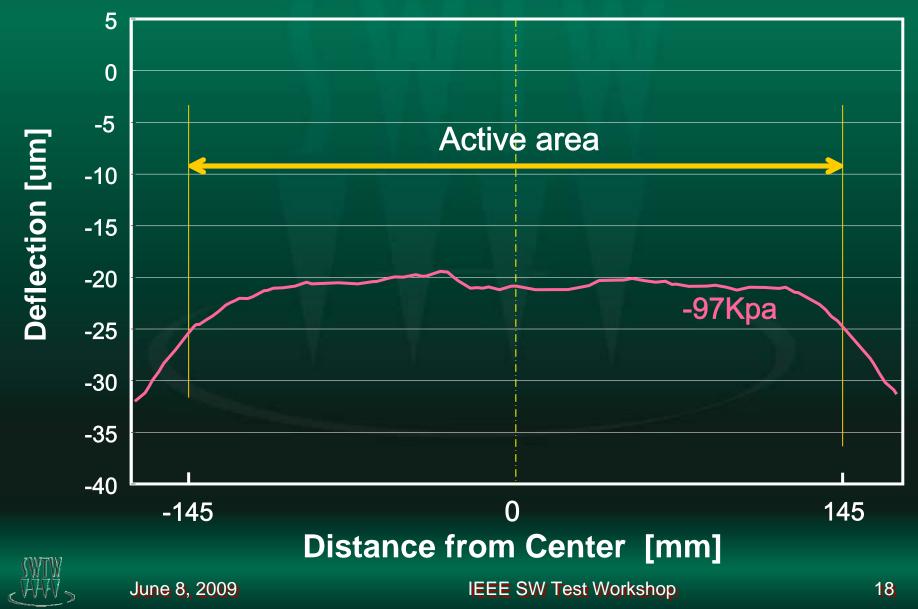

### **PCB Bend Characteristic**

### **PCB Deflection**

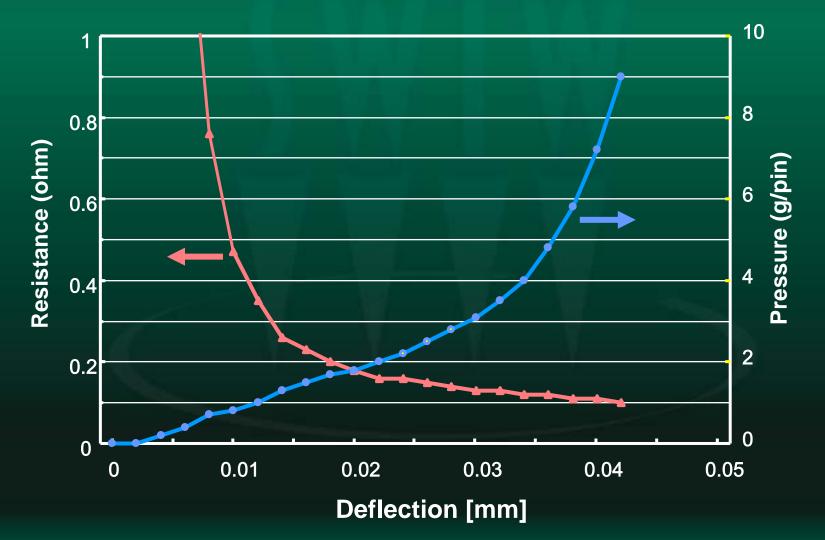

### **PCR Characteristic**

June 8, 2009

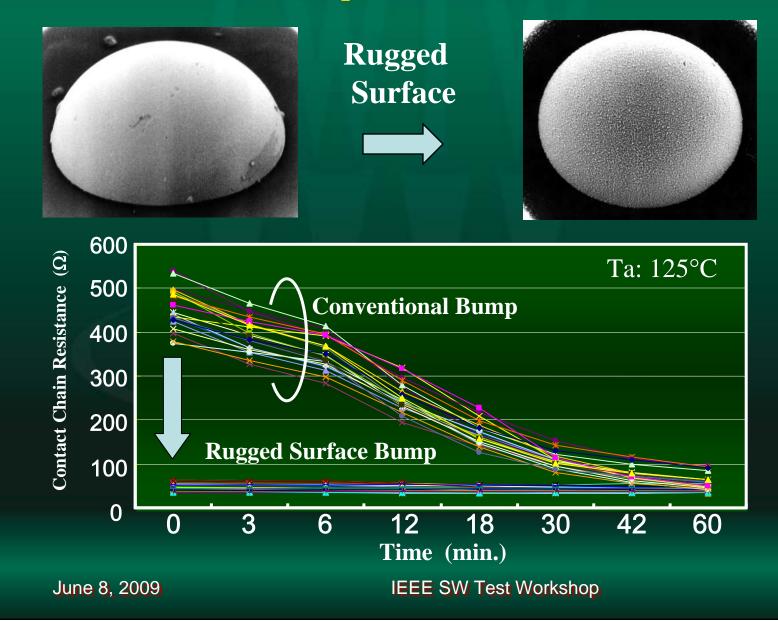

### **Bump surface**

20

## **150k Contact Results**

| Pad Pitch              | <b>160</b> μ <b>m</b>                                | <b>120</b> μm | 90µm   | Total<br>w/o dummy |

|------------------------|------------------------------------------------------|---------------|--------|--------------------|

| Bumps*                 | 49,147                                               | 51,322        | 50,114 | 150,583            |

| Load [ mN ]<br>/ Bumps | 39                                                   | 39            | 39     |                    |

| Load [ N ]<br>/ Wafer  |                                                      |               |        | 5,850              |

| Result                 | Bump contact + PCR +Circuit<br>= 100 ~ 200 [mΩ]/ pin |               |        | 0                  |

\* Count out Dummy Bumps of out side

June 8, 2009

# Summary

- Stable contacts have been achieved by 150k bumps.

- The total load on 300mm wafer is 7,000N or more, which is achieved by using a uniform atmospheric pressure method.

- Probe card does not need special structure (e.g. stiffener) nor special alignment system.

This leads to a realization of a cost effective and new concept test system.

## **Acknowledgements**

### Special Thanks to :

HOYA : Mr. Sugihara, Mr. Tsukino, Mr. Sawada

JSR : Mr. Harada, Mr. Satoh, Mr. Mayumi

TSK : Mr. Ishimoto, Mr. Watanabe

Panasonic : Mr. Miyake

ASET : Mr. Inagaki, Mr. Kada, and All of Chip Test Technology Lab.

members

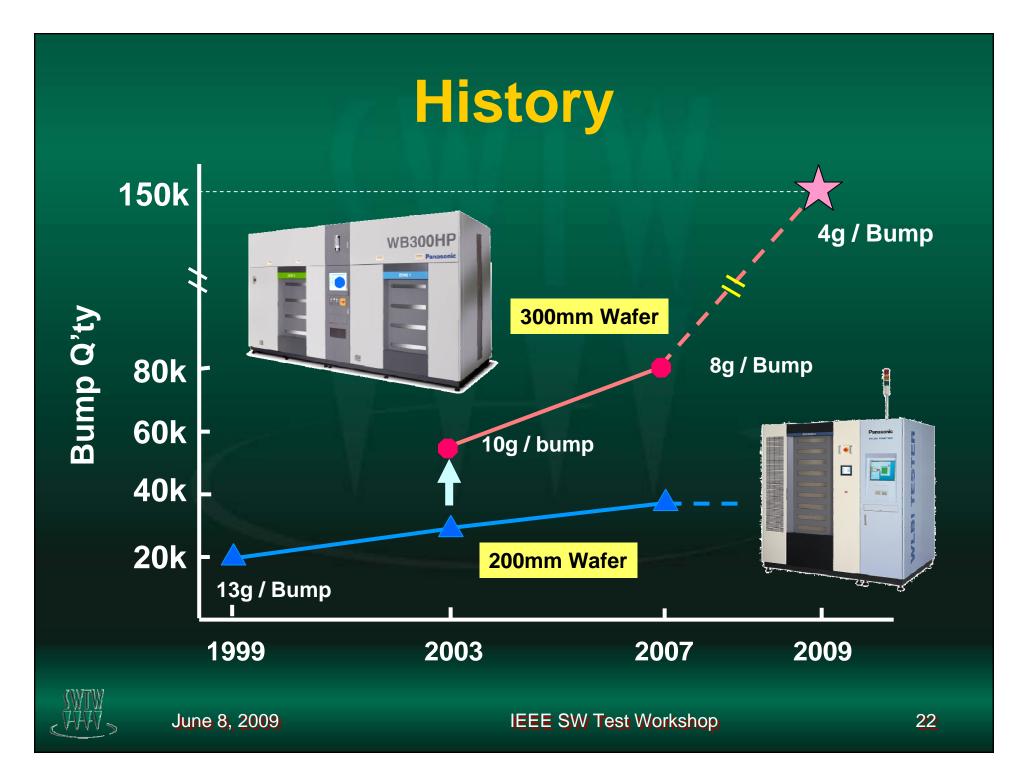

This work was developed based on the WLBI technology of Panasonic.

June 8, 2009