**IEEE SW Test Workshop** Semiconductor Wafer Test Workshop

> June 7-10, 2009 San Diego, CA

### Issues in Power Delivery System Performance Verification

Gert Hohenwarter GateWave Northern, Inc.

- Review power and ground path integrity

- Examine model and measurement approaches

- Show some limitations and workarounds

## Approach

- Examine power path in a probe card

- Illuminate power delivery system integrity requirements (aka power delivery network)

- Use models and measurements to evaluate performance

- Provide a workable verification approach

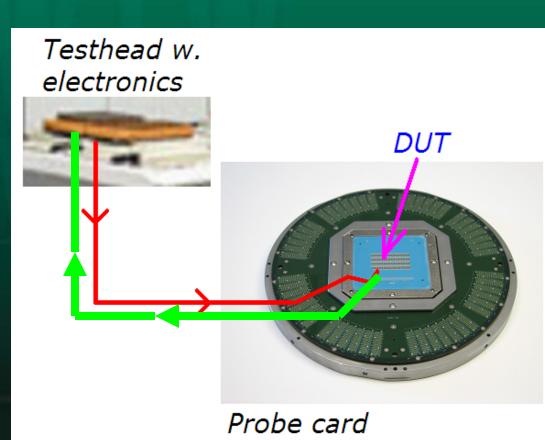

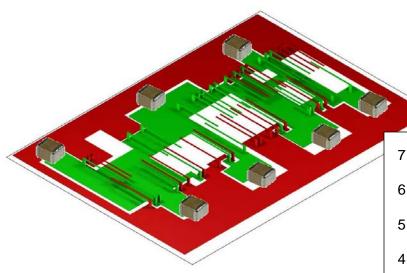

## **Physical environment**

Typical test system

Power travels from tester to DUT over a considerable distances compared to switching times of the devices under test, thus.....

June 7 to 10, 2009

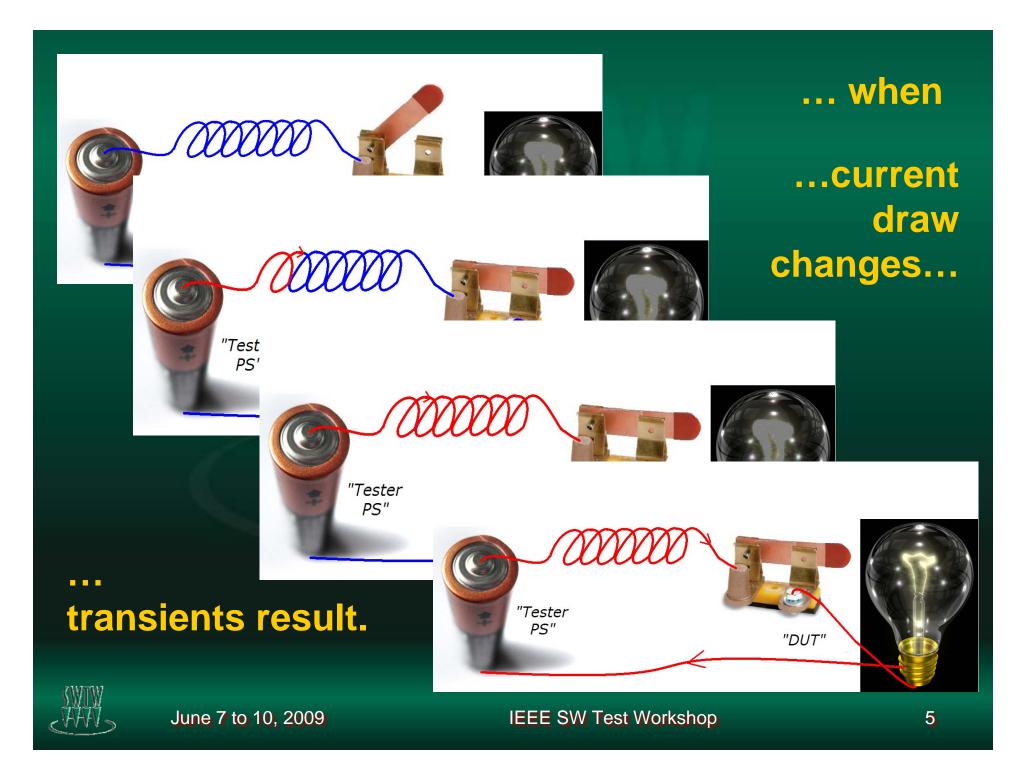

## Noise and impedance example

Sudden current draw results in a voltage according to V=L\*di/dt

| di/dt=   | 0.25  | A/ns |

|----------|-------|------|

| L=       | 0.200 | nH   |

| Vripple= | 50    | mV   |

Impedance at a particular frequency is an alternate way of expressing noise voltage: V=Z\*i

| <b> </b> = | 0.25 | Α   |

|------------|------|-----|

| <b>Z</b> = | 0.2  | Ohm |

| <b>V</b> = | 50   | mV  |

$$Z_{PDS} = R + jX$$

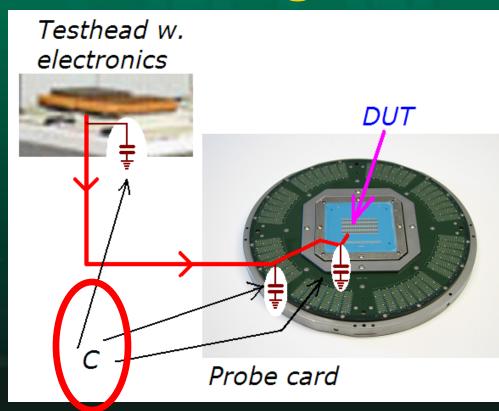

# Remedy: Additional energy storage

# Bypass capacitors (C) provide additional energy during times of sudden high demand

June 7 to 10, 2009

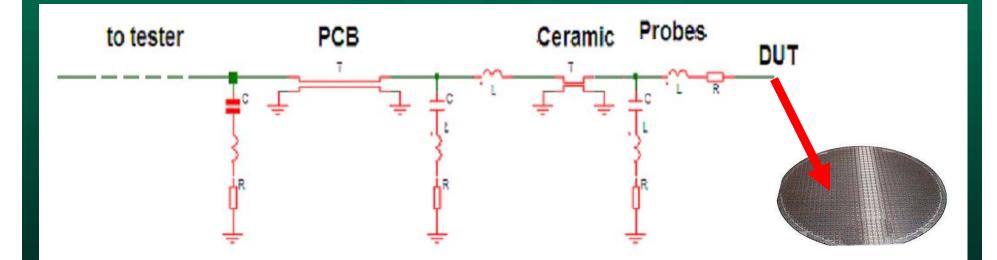

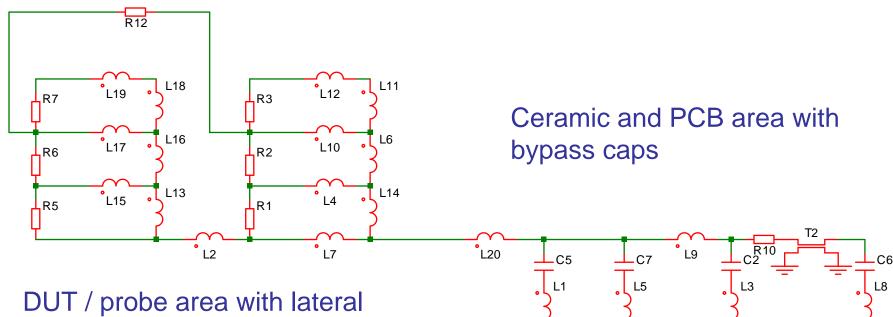

## **Tester to die path model**

# Components of the power delivery system (PDS) { P/G planes act as low Z transmission lines 'T' }

June 7 to 10, 2009

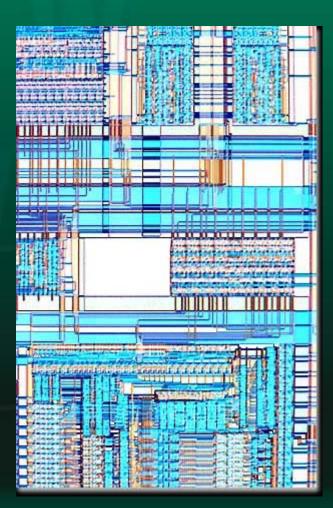

## **Power distribution inside DUT ?**

Problem – probe card manufacturer often doesn't know precisely what's in the DUT

# Design

PDS impedance specification provided by IC manufacturer

•

$$Z_{PDS} = R + jX$$

Power delivery system performance depends on path and position

- Both delivery and return paths are important

- Disruptions/detours add inductance

- FEA and CAE tools must be set up to take paths into account

#### • Verification

June 7 to 10, 2009

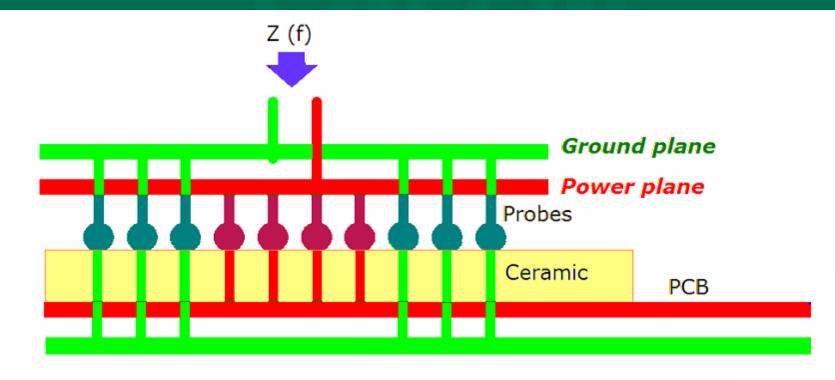

## **Typical model setup**

# Planes are established at the DUT level - the impedance Z(f) is then determined from the DUT side

June 7 to 10, 2009

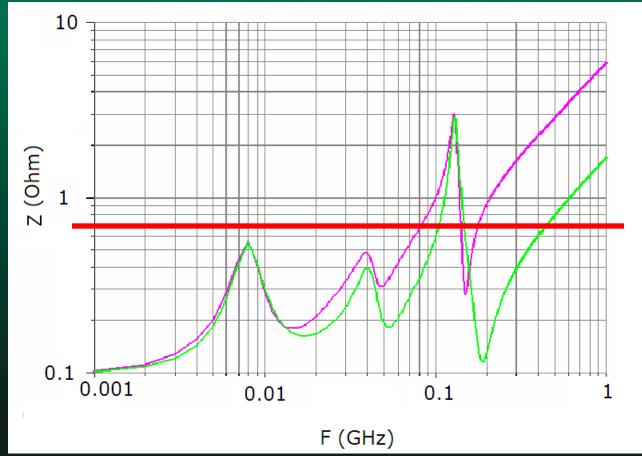

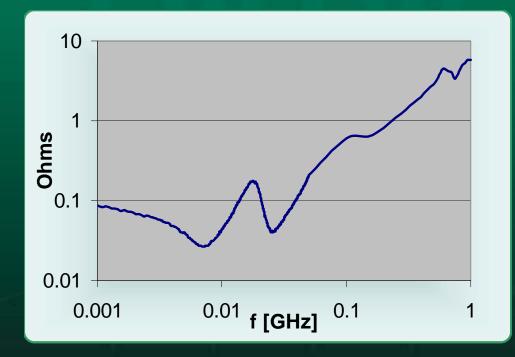

## **Modeled** impedance

Resonances are due to multiple transmission line sections between bypass capacitors

June 7 to 10, 2009

## But does the PDS really work?

- Instruments

- DMM / Impedance meter

- -<u>Time</u> Domain <u>R</u>eflectometer (TDR)

- -<u>Vector</u> Network Analyzer (VNA)

- Probes

- Individual

- Whole die (surrogate DUT)

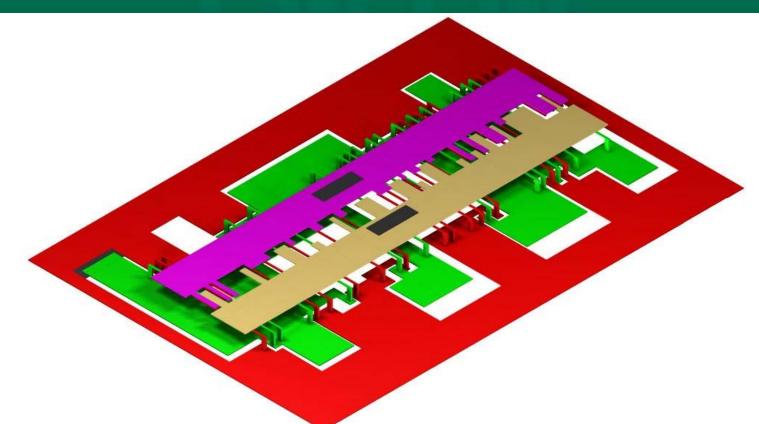

## **Probing – surrogate DUT**

#### **Probe card site**

#### Surrogate DUT

Develop thin film based surrogate DUT circuit, touch down on a probe card die site and measure impedance at relevant locations on surrogate DUT

June 7 to 10, 2009

# Surrogate DUT in contact with probes

# Z can be measured/modeled at various locations of die and represents the Z experienced by a circuit under test

June 7 to 10, 2009

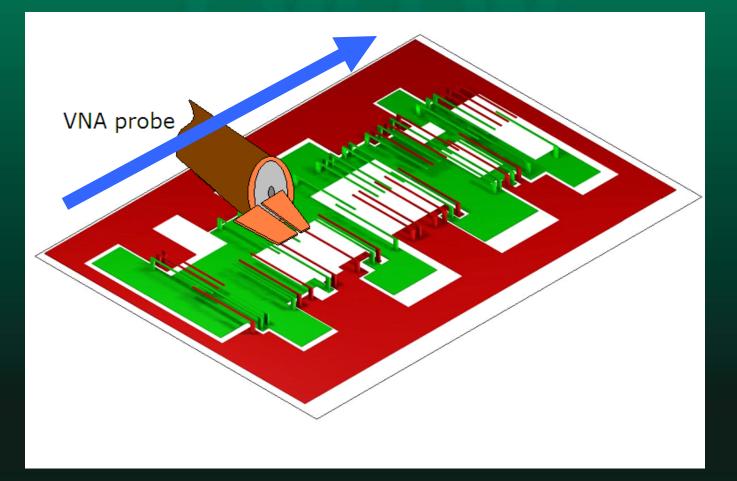

## **Alternative: Discrete probe test**

#### Measure returned signal for each accessible pad

June 7 to 10, 2009

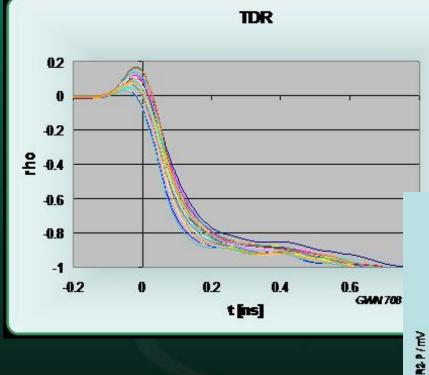

## **TDR measurement**

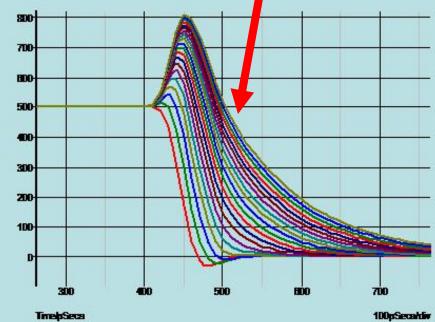

#### Model plot for inductance values from 200 pH to 5 nH

#### TDR does allow for extraction of some info about PDS performance

June 7 to 10, 2009

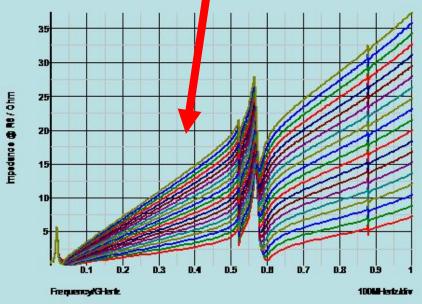

## VNA measurement (Z)

#### Model plot for inductance values from 200 pH to 5 nH

#### VNA shows whether there are frequencies that are "off limits"

June 7 to 10, 2009

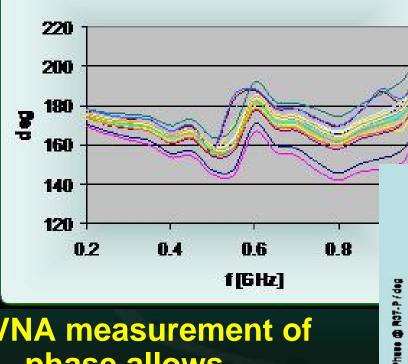

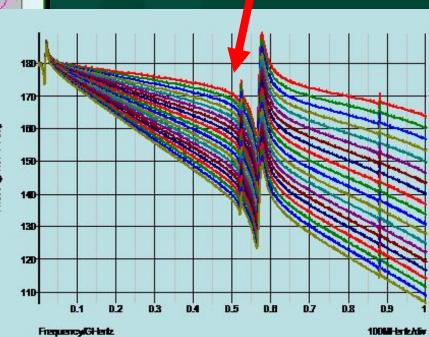

## **VNA measurement (Phase)**

Phase (f)

VNA measurement of phase allows determination of complex impedance e.g. inductance

Model plot for

inductance values

from 200 pH to 5 nH

June 7 to 10, 2009

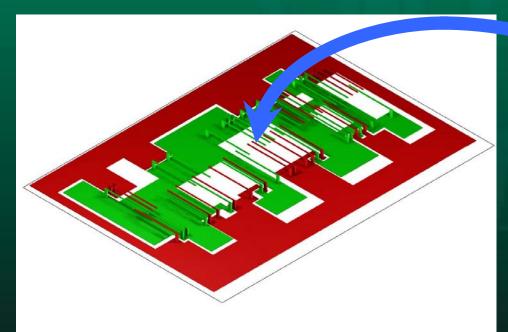

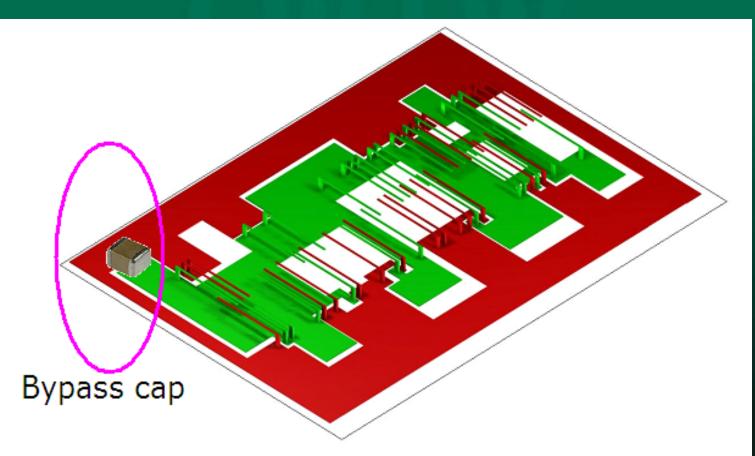

## **Example configuration**

#### Hypothetical die layout with bypass capacitor placed at one end

June 7 to 10, 2009

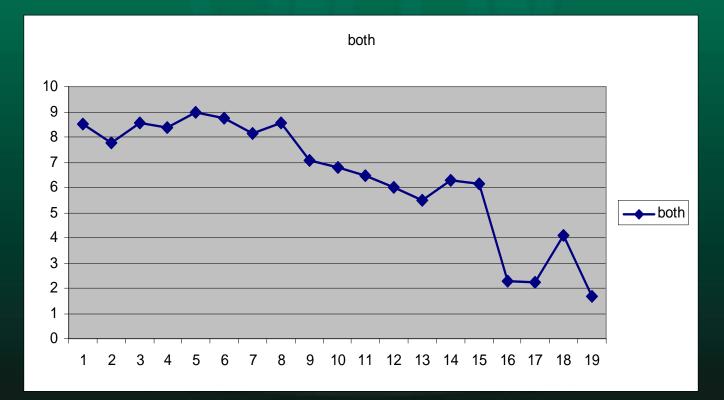

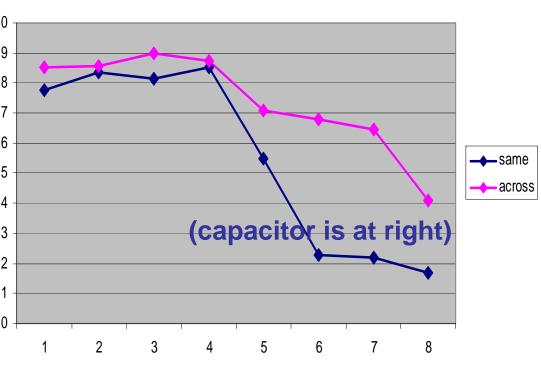

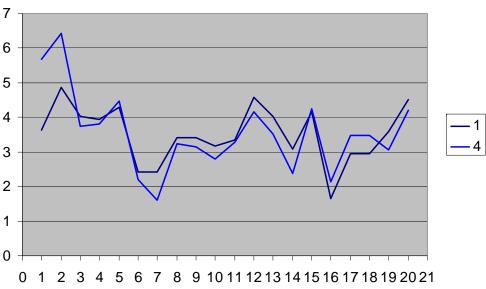

#### Inductance as a function of pad location

Inductance L (nH) along the die (capacitor location is at right)

June 7 to 10, 2009

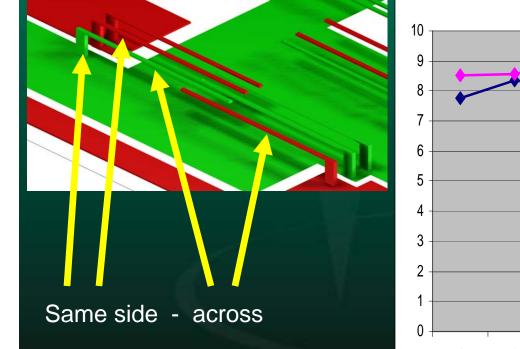

## Inductance L (nH) along the die

Measurement taken with probe ground on the same side as signal contact (pink) or across to opposite ground area (blue)

June 7 to 10, 2009

#### **DUT area with multiple bypass caps**

#### Impedance Z (Ω) at 250 MHz as a function of position across die (2 nearly identical die)

June 7 to 10, 2009

# Still don't know overall Z...

• Solution: Combine measurements with simulated results for interconnect inductance

interconnect inductance plus inductance of contacts

June 7 to 10, 2009

**IEEE SW Test Workshop**

R8

R11

R4

R9

## **Z** combined

# Individual Z measurements combined into an overall performance assessment

## Summary

- Power delivery system performance depends on path and position

- Grounding during measurement as well as model development must be carefully planned

- The overall performance is NOT the result of assuming that all measurements effectively form a parallel circuit of the individual Z measurements

- A combination of measurements and models allows for assessment of overall performance

- Local performance should be verified against specifications