**IEEE SW Test Workshop** Semiconductor Wafer Test Workshop

> June 7-10, 2009 San Diego, CA

## Overcoming challenges of high multi-site, high multi-port RF wafer sort testing

Daniel Watson Mechanical Engineer Teradyne, Inc.

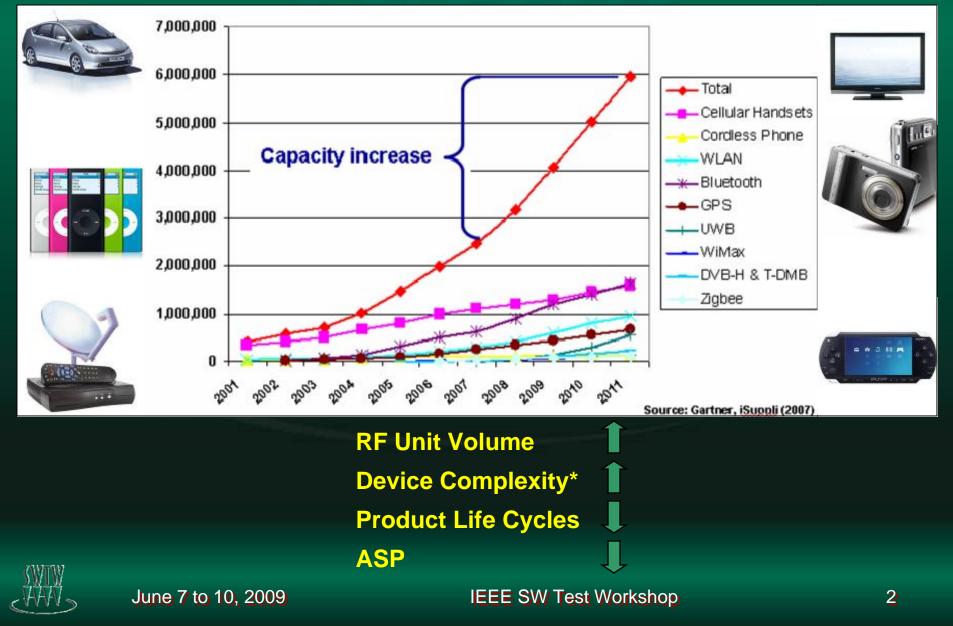

## Worldwide RF Semiconductor Market Trends: Strong Growth and integration into almost everything

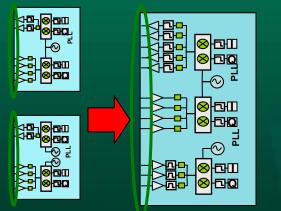

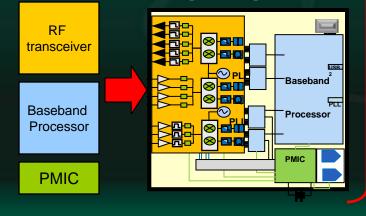

## Increasing Device Integration in RF and Digital impose design constraints

## Multi-mode Transceivers, MIMO

#### RFSOC – Single Chip Radio & Analog Integration

#### **Complexity Impacts**

- RF Port Count

- Parallelism

- Package Size

- Digital Baseband

- High Speed Serial

- Test Time

- ASP 📙

#### Interface Design Challenges

- Increased Applications Space

- Higher RF mating forces

- High Digital Pin Force

- Signal Integrity

- Current Prober Capabilities

- COT Leverage existing interface technology

- COT Minimize interface circuit board cost

June 7 to 10, 2009

# What do we mean by high multi-site, high multi-port RF wafer sort testing?

High Multi- Site:

Above x2

Up to X8 (and to X16 future)

Digital Pins

Greater than 2000 signal pins

Multi-Port RF:

Up to 16 RF Ports per device

Low density = 24 RF Ports total

Medium Density = 64 RF Ports total

High Density = 96 RF Ports total

# Essentially, get 10 pounds of Wafer S#!T test into a 5 pound test interface bag...

June 7 to 10, 2009

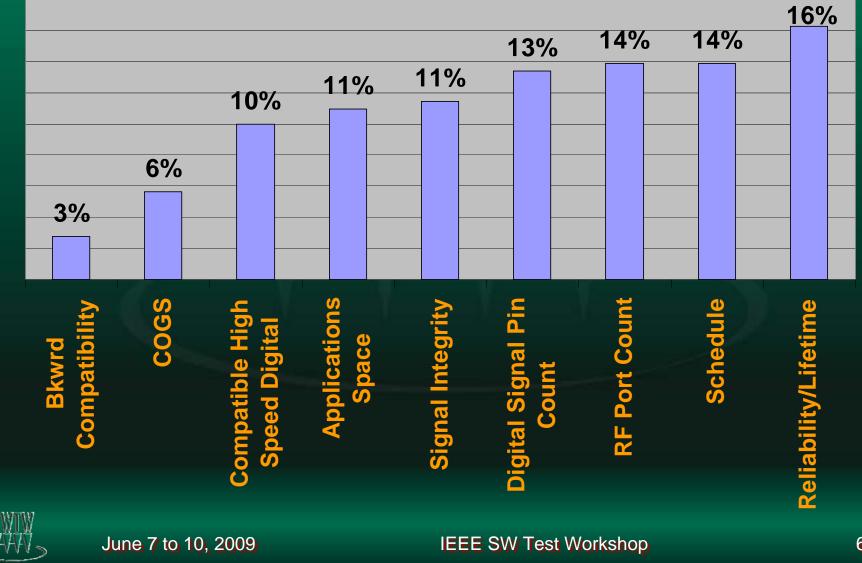

# Look at the entire RF interface as a system – define what is important so Intelligent Tradeoffs can be made...

#### **RF Probe: Criteria Weighting**

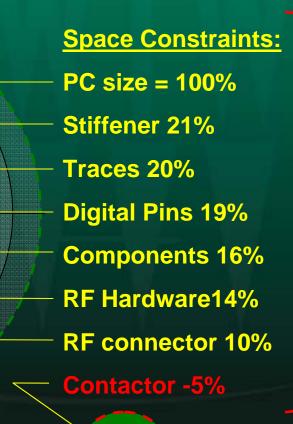

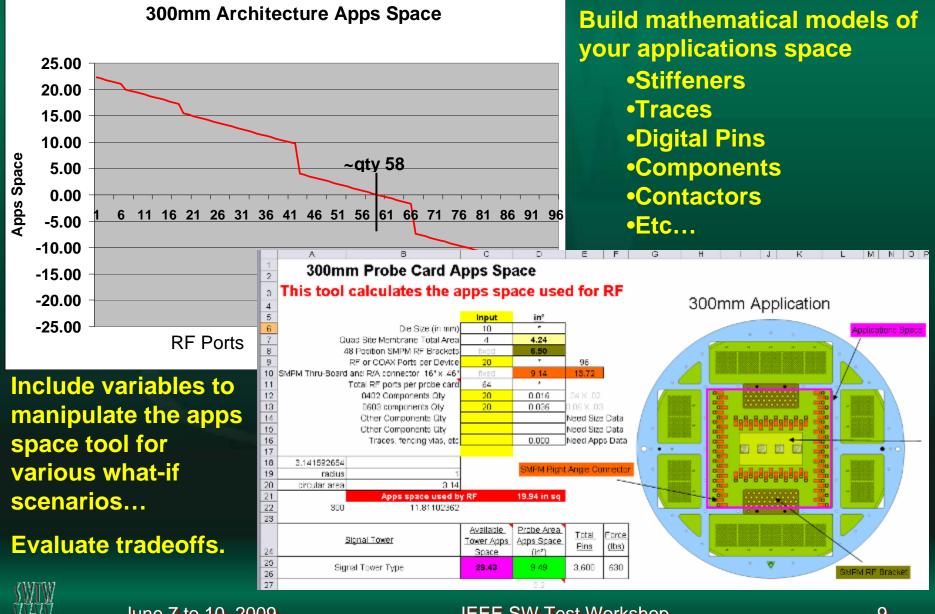

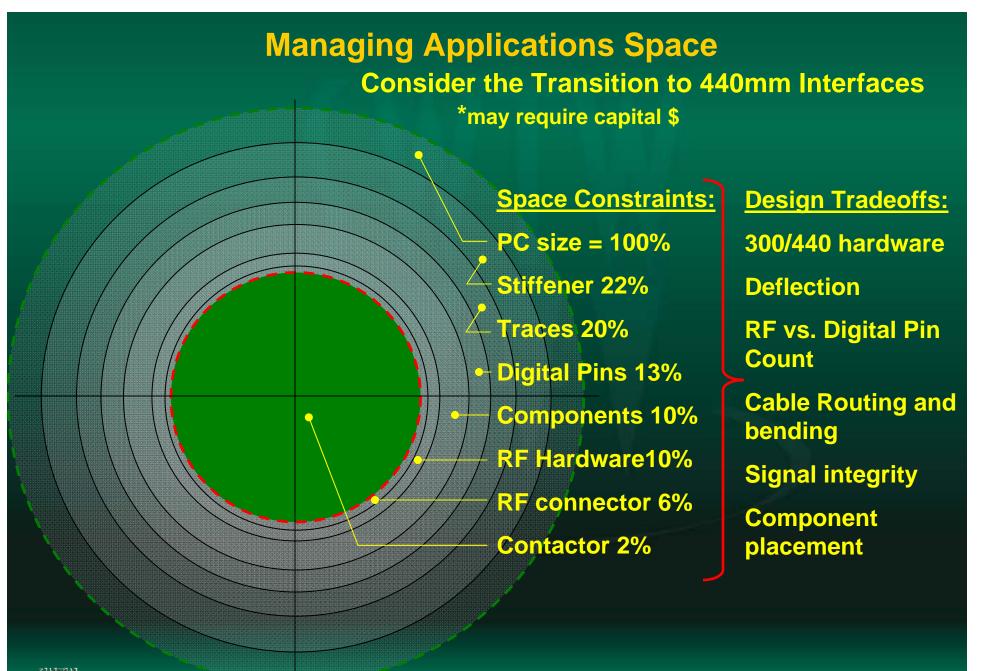

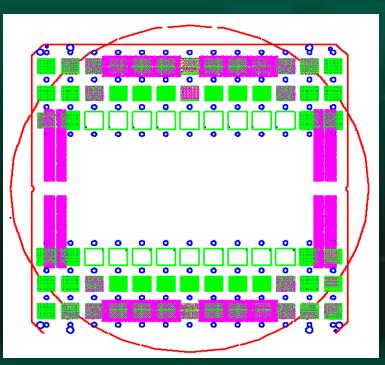

## Applications Space – Some Applications can require more space than is available with 300mm hardware

Design Tradeoffs: 300/440 hardware Deflection RF vs. Digital Pin Count Cable Routing and bending Signal integrity Component placement

June 7 to 10, 2009

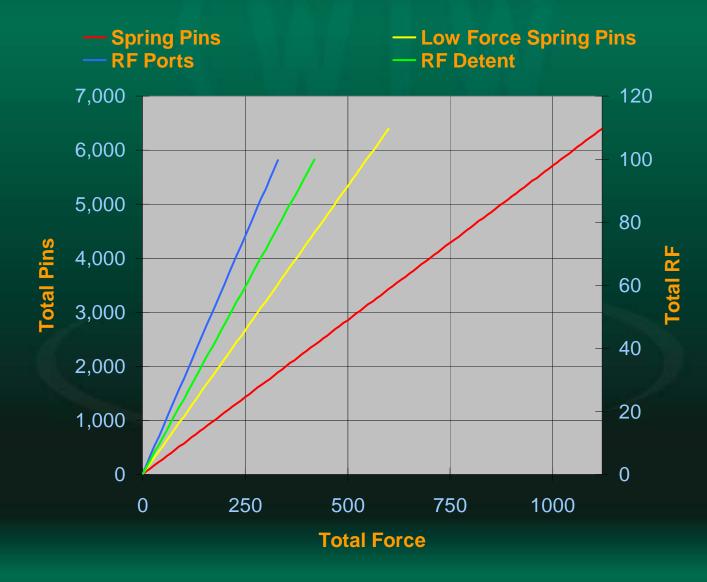

# RF Interface Forces Can overload interface components

June 7 to 10, 2009

### **Managing Applications Space**

June 7 to 10, 2009

#### IEEE SW Test Workshop

9

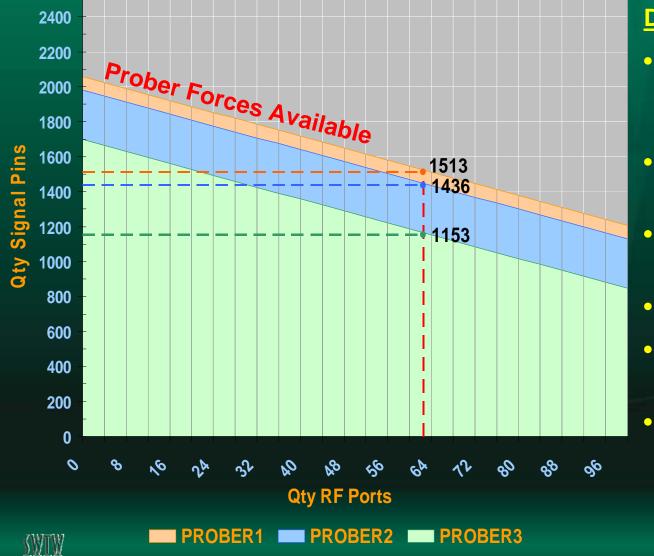

### **Managing RF Interface Forces**

Model and Understand the tradeoffs required to meet force constraints 300mm Prober Forces - RF Ports vs Signal Pins Tradeoff

June 7 to 10, 2009

#### **Design Tradeoffs:**

- Top Load vs. Bottom Load Interface Systems

- Bottom Probe Card Changer capacity

- Tester docking capacity

- Deflections

**IEEE SW Test Workshop**

- RF vs. Digital Pin Count

- Don't forget un-mate forces...

11

## **Managing RF Interface Forces**

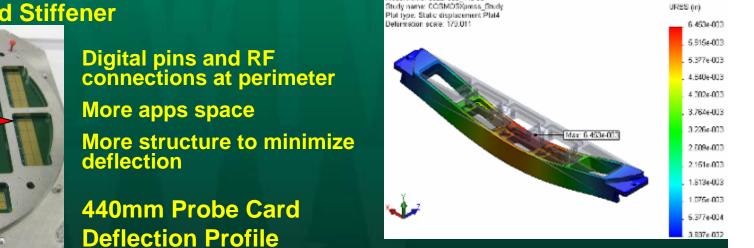

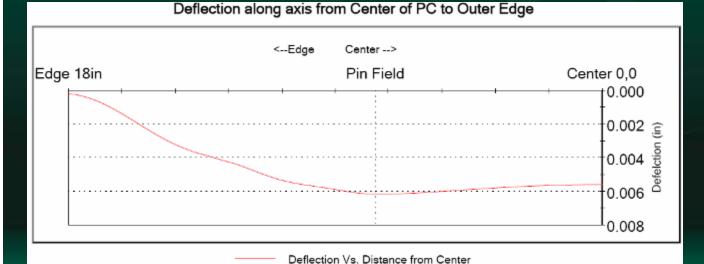

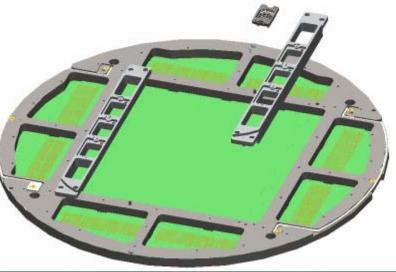

#### Maximizing applications space and minimizing probe card deflections

#### 440mm Probe Card Stiffener

Model name: 60227600\_440-96

### 440mm 96 Port RF hardware Deflection Study

June 7 to 10, 2009

## Maintaining RF Signal Integrity/Reliability

#### Leverage existing technologies:

- Integrate with cable vendors to maximize performance while supporting required bend radii, cable diameter, connector options, etc...

- RF connector types (custom SMPM) have Proven signal Integrity, reliability

- Multiple connector styles allow application flexibility

- Support muxing, splitting, attenuation, etc.

- Allow active/passive component placement as close to DUT as possible

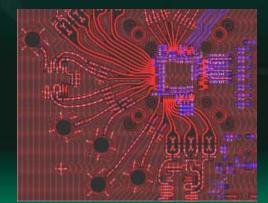

### **COT – Managing Interface Circuit Board Design**

Plan the board design with signal tower, apps space, and board routing integrated early.

Careful design and routing can facilitate pass through connections.

Avoid Blind Vias Avoid Multi-layer Construction

**Potential \$30% Savings**

June 7 to 10, 2009

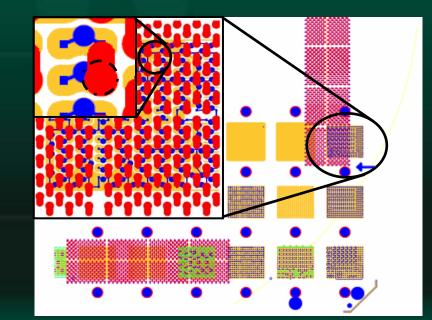

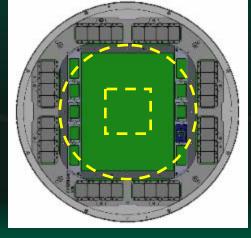

## **Real 300mm RF Hardware**

#### 300mm with 64 RF Ports 900 digital pins

## You can still pack a lot of punch into a 300mm interface with careful planning

June 7 to 10, 2009

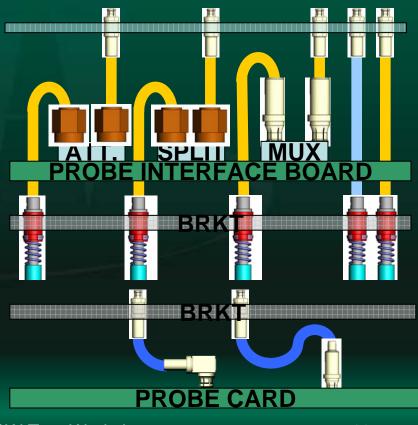

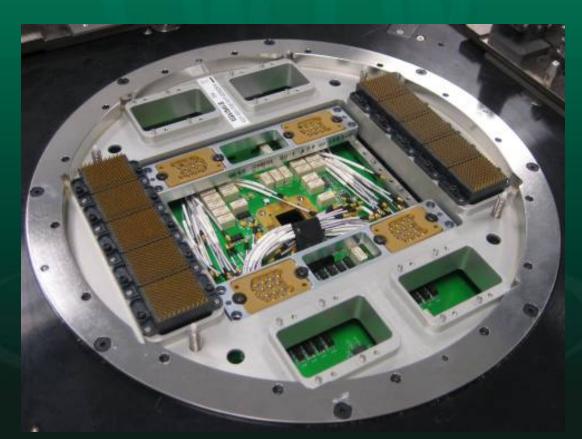

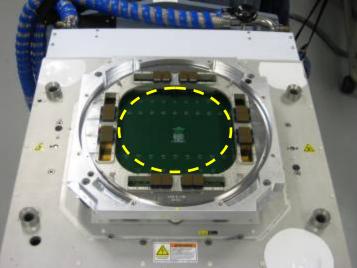

## **Real 440mm Solutions**

440mm Probe Tower and Probe Card with up to 96 RF Ports and 2880 digital pins

20 inch chrome June 7 to 10, 2009

## In Conclusion...

- High density RF interface solutions pose some significant challenges, but are very manageable.

- Teradyne has done quite a bit of work to understand and define these challenges, and managed them to develop solutions that work.

- The key is to think big picture, act as a general contractor or system integrator.

- Learn the capabilities of the existing equipment technologies.

- Build tools that let you evaluate tradeoffs and investigate the variables of what-if scenarios.

- These challenges can be overcome with proper planning and careful implementation!