# IEEE SW Test Workshop Semiconductor Wafer Test Workshop

June 7-10, 2009 San Diego, CA

### Rapid Diagnostics Using a Prober Based PCA

Tools for Verifying Connections

Sammy Mok VeraConnex, LLC

### **Motivation**

- Experienced the challenges of building advanced memory probe cards

- How do you ensure your probe card works in production?

- Cards in production deflect differently than PCAs

- Testing at multiple temperatures is required

- Intermittent connections can not be detected

- Life testing with relays does not work

- Test solutions get expensive

- Probe counts 60K+, embedded ICs, card sizes >480 mm

- Need convoluted test flow with custom developed tools

- Need real time and comprehensive diagnostic tools

- There has to be a simpler solution

# Challenges

- Probe cards can generate >200Kg force & every test cell can deflect differently

- Deflection contributors

- Prober chuck and head plate

- Probe cards and their attachment to head plates

- ATE test head weight

- Temperature distortion (-45 to +200°C)

- Significantly reduce the cost of test

- How do you test for Cres and electrical planarity with ICs in the way?

# **Objectives / Implementation**

#### Minimize deflection differences of test cells

- Mount switch electronics on probe card in target prober

- Use ATE suppliers interface kits to attach to head plate

- Use manipulator to support electronics & replicate load

- Perform tests at all required temperatures

- Measure tip positions using scrub marks on blank wafer

#### Reduce cost of test

- Faster parallel bussed pin testing

- Streamline the test flow keep on one tool

- Minimal cabling and connectors

- Scrub mark damage to replace force measurement

#### Test through embedded ICS

Any channel can be a logic control channel

# Approach

- First target: ATE with large installed base

- Advantest T5375: 96 ZIF connectors, 440 mm

- Criteria

- True 4 point measurements

- Control digital ICs

June 7 to 10, 2009

- High performance: intermittent & life time testing

- Hot switching & stable ⇒ solid state switches

- Measure passives and relays

- Scalable architecture: start at 65,536 channels

- Thorough self-test: configuration and communication

- Confocal microscope: location & damage = force

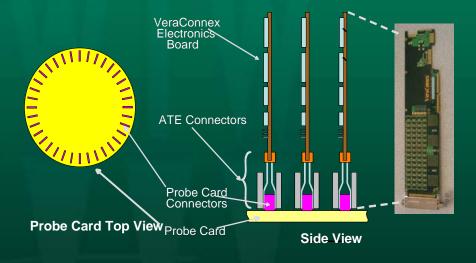

### **Electronics Hardware**

Manipulator to support pin electronics and match load

Prototype:

Shown directly mounted on head plate of EG prober

**Prototype on EG Prober**

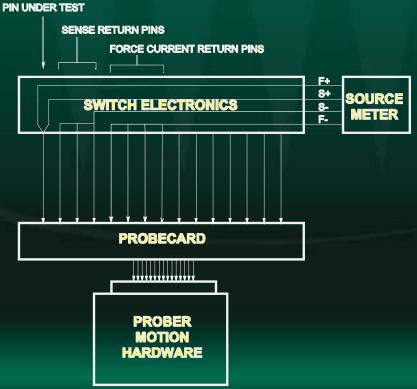

# Cres Testing: Signal Probes

- 4-wire resistance measurement of each probe using probe card

- Use prober to raise blank metalized wafer in contact with all probes

- Connect force F+ and sense S+ rails from measurement unit to selected probe

- Connect force F- and sense S- from measurement unit to several near by probes

- Voltage across F+ to F- limited to < 50mv to not burn through interface layers</li>

#### **Performance Verification**

- Use system to analyze a 64 site LM4 probe card to evaluate tool effectiveness in diagnosing problems

- Electrical Planarity (on Au and Al wafers)

- Cres on 100 touchdowns to Au and Al wafer

- Leakage

- Verify measurement speed

- More than 300 Cres tests per second

(Data+Reports for presentation in minutes)

- Immediate data analysis and capture of images from electrical results

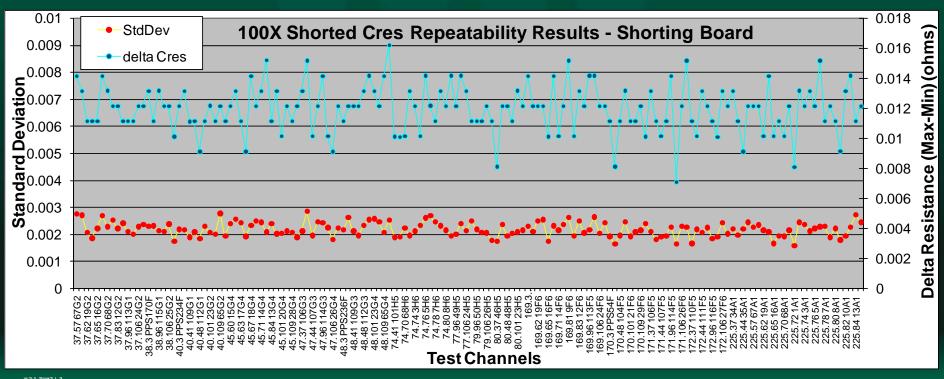

# Resistance Repeatability

- Pin Card Measurements with shorting board

- 100 Measurements are consistent to within 16 mohms

- Values include: Shorting resistance +Traces + Connector

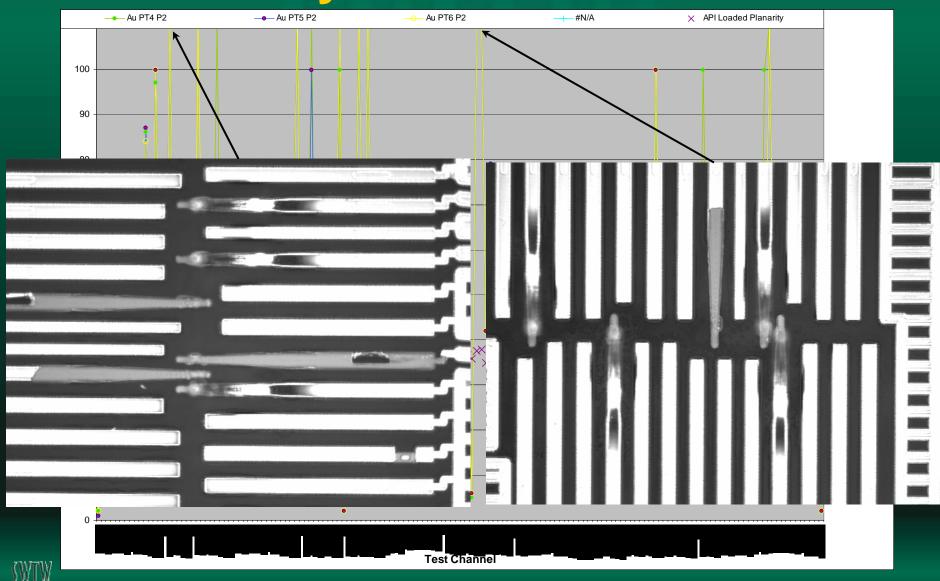

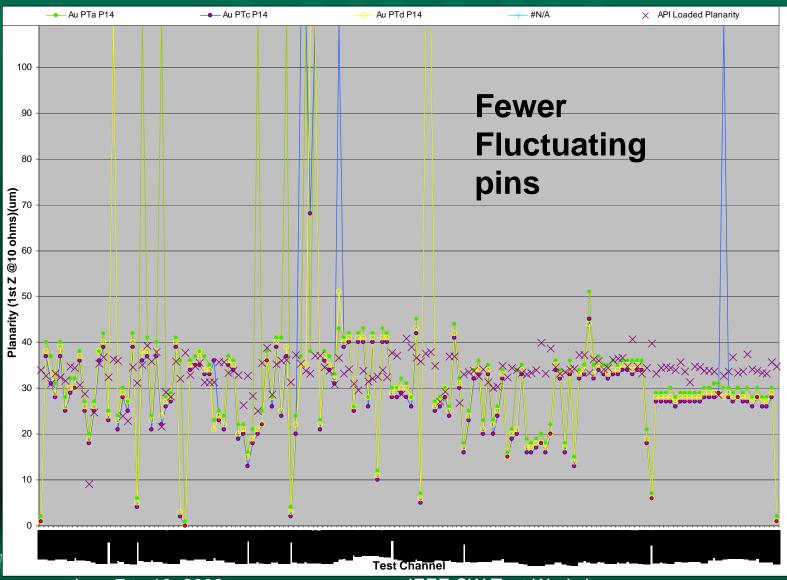

## 3X Planarity Results on Au Wafer

### 3X Planarity on Au Wafer after clean

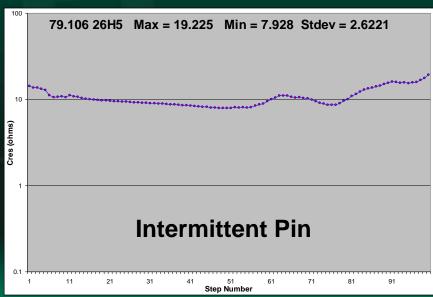

#### **Animation of Contact Resistance During Planarity Test**

Before Cleaning

**After Cleaning**

154 Test Channels

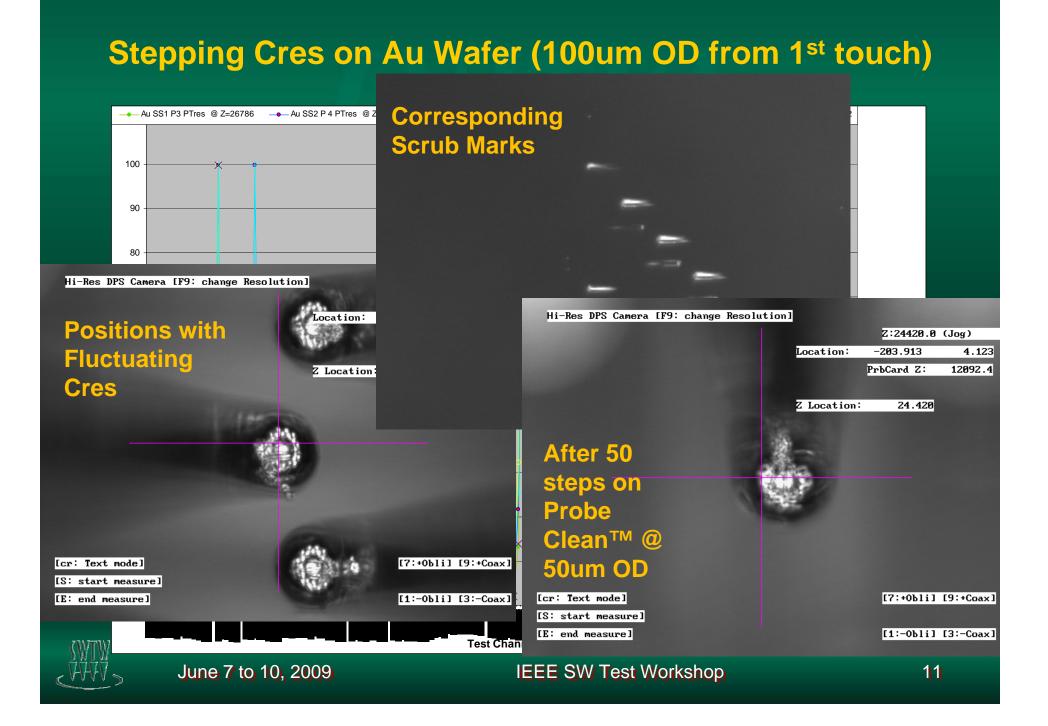

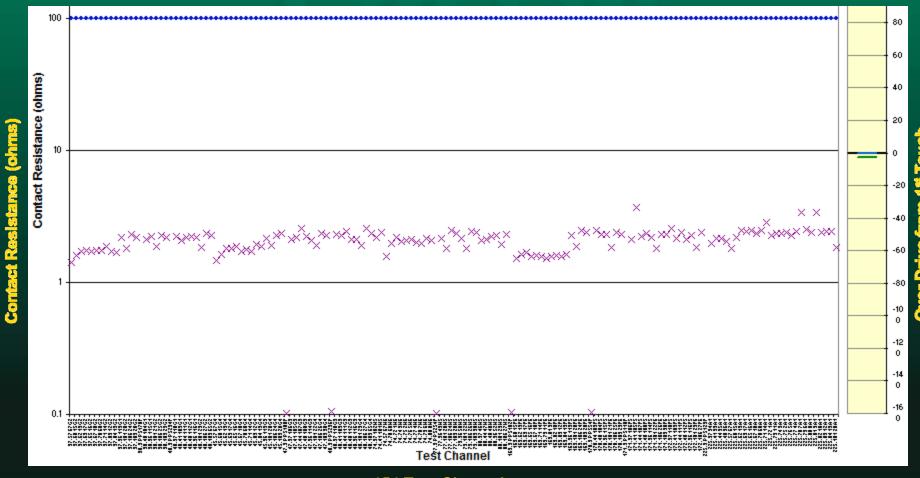

# Individual Pin Cres During Planarity Test (Au Wafer @ 75um OD after 1st touch) (Post clean)

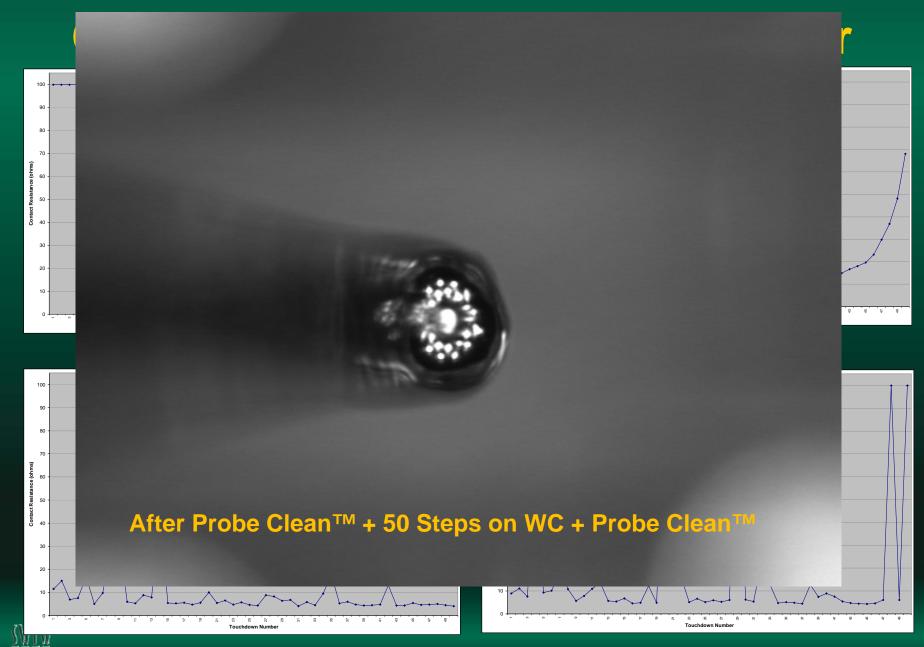

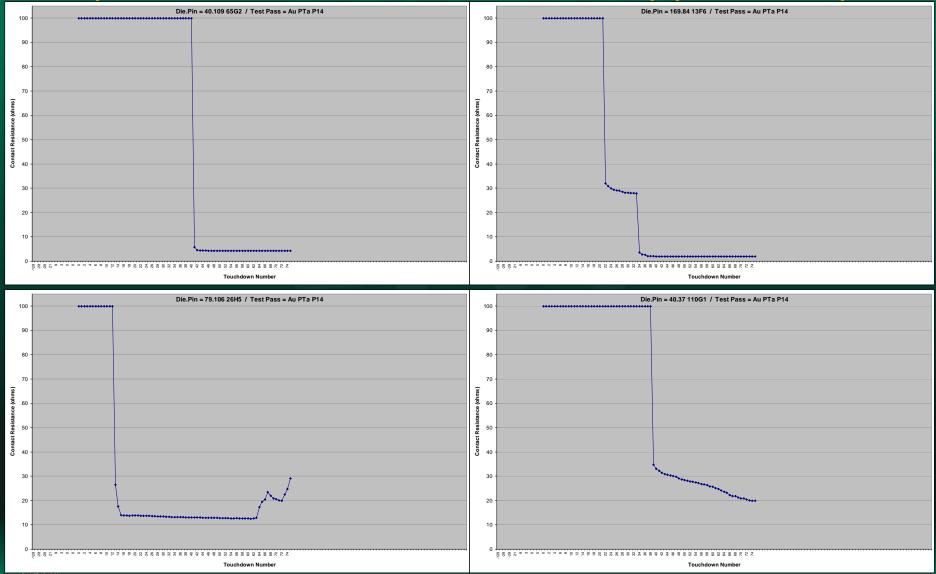

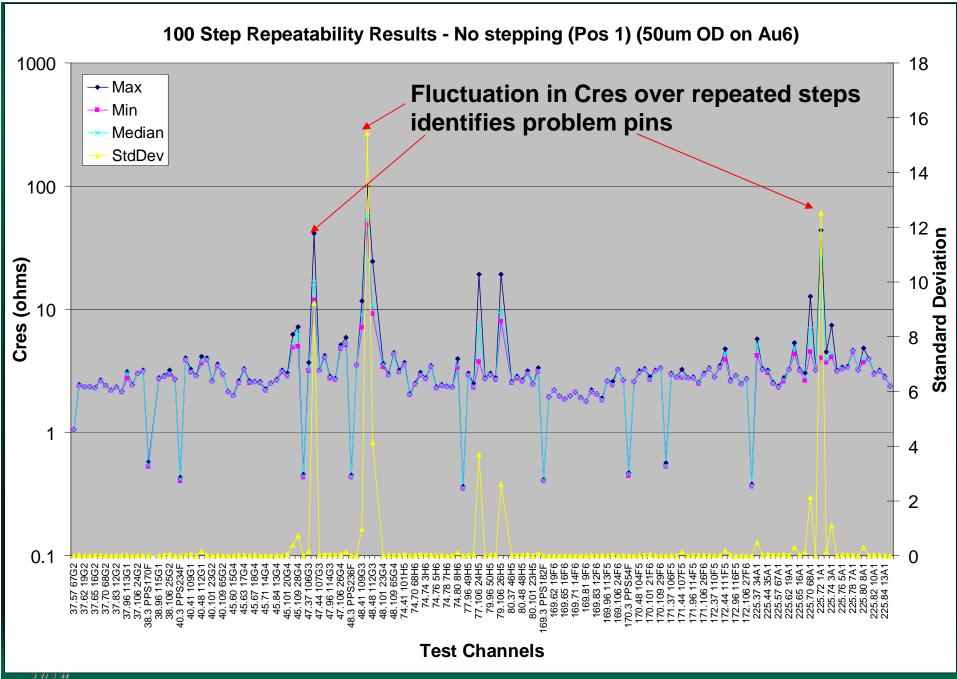

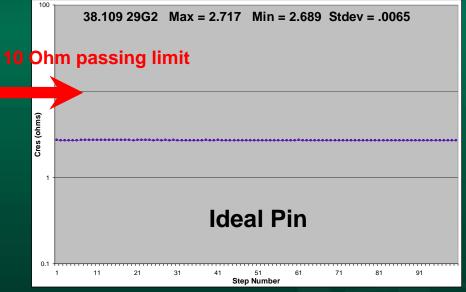

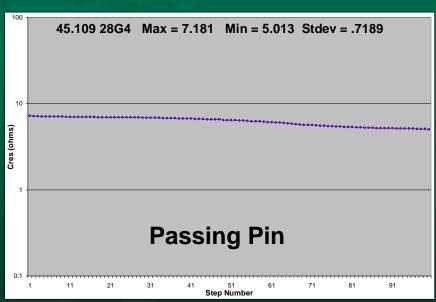

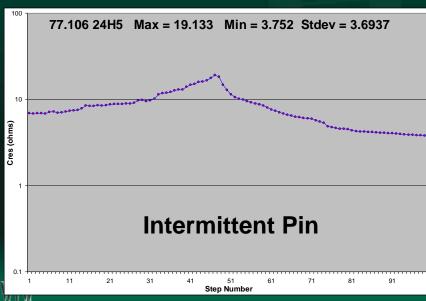

#### Per Pin Cres Signature over 100 Steps on Au

#### Per Pin Cres signature over 100 Steps on Al

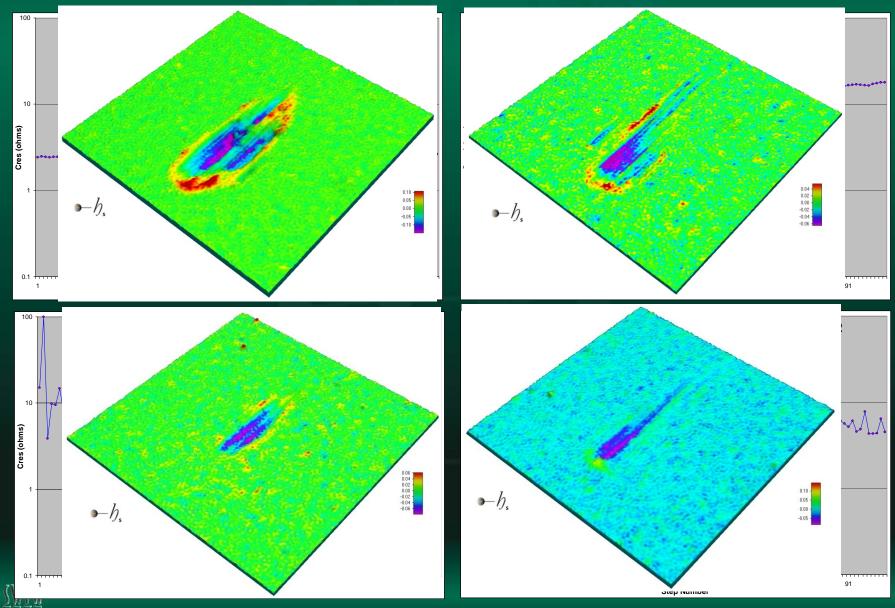

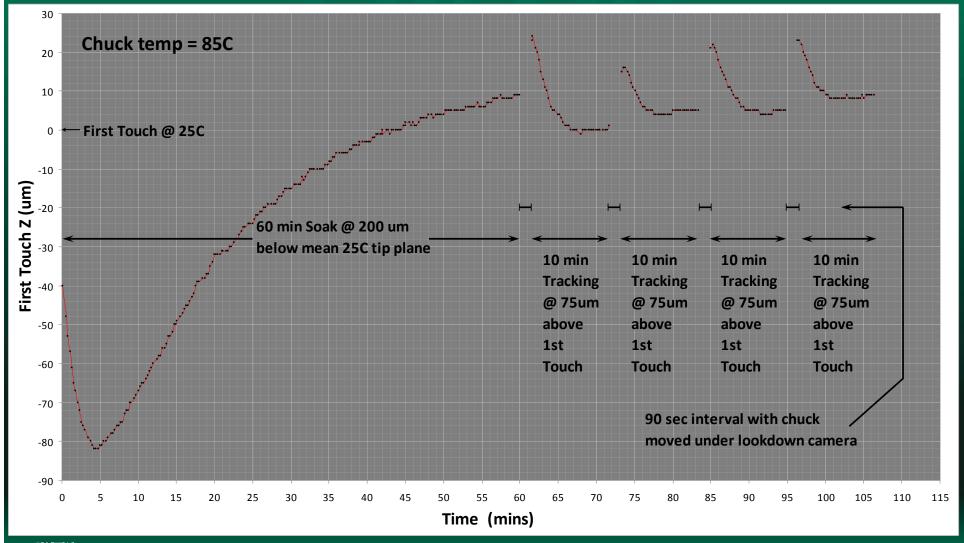

#### First Touch Z Sampled During 1 hr Soak

## **Dynamic First-Touch Z Profiling**

#### Results

- Demonstrated that the system can collect data in minutes and provide immediate analysis

- Fast electronics integrated into prober opens up new methods in diagnosing problems

- Fast Cres measurements enable collection of individual pin signatures

- Can identify unique problems despite passing Cres

- Intermittent Cres can be identified

- Dynamic planarity behavior of probe card can be observed

- Integrated real time data analysis help correlate measurements to problem pins

### Follow-On Work

- Investigate other signatures

- Scrub

- Correlation of pin signature to

- Probe card life

- Product die test yield

# Acknowledgements

- Co-Authors: VeraConnex, LLC

- Frank Swiatowiec

- Fariborz Agahdel

- Bruce Pettyjohn

- Hyphenated Systems, LLC

- Edward Robinson

- Electroglas, Inc.

- Steve Martinez

- Jonathan Halderman

- Aehr Test

- Chris Buckholtz