# Backend to the Front Line

Semiconductor Wafer Test Workshop San Diego June 12, 2011

William Chen ASE Fellow Senior Technical Advisor ASE Group

CPMT Distinguished Lecturer

#### Greetings from the IEEE Components Packaging & Manufacturing Technology Society (CPMT) We wish you great success in the SWTW Workshop

#### Very best wishes from engineers and scientists at the ASE Group worldwide

## Outline

- History

- Market Landscape

- Game Changing in the Backend

- SIP & 3D

- Food for Thought

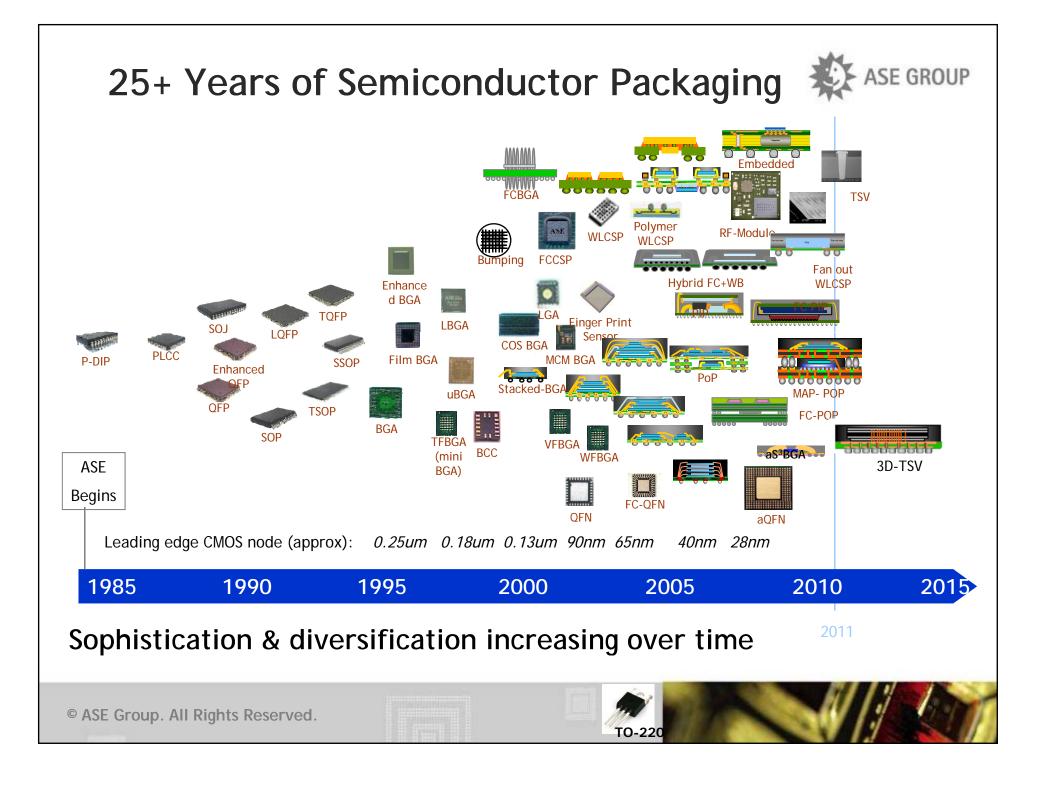

## The Early History of the Industry

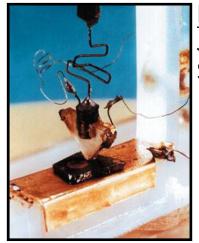

<u>First Transistor</u> John Bardeen, Walter Brattain, William Shockley 1947

First Integrated Circuit

Jack Kilby 1958

First Planar Integrated Circuit

> Robert Noyce 1959

#### Workhorses for Back End Industry

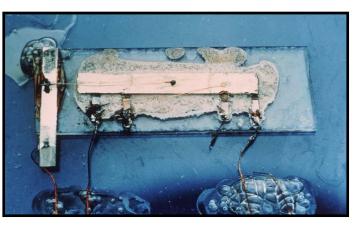

Au Wirebond – 1967 Source: George Harman

C4 Solder Bump 95/5 Assembly 1970 Paul Totta

Au wirebond and Solder flip chip have been the work horses of the IC packaging industry, since the dawn of integrated circuits.

© ASE Group. All Rights Reserved.

Source: Texas Instrume

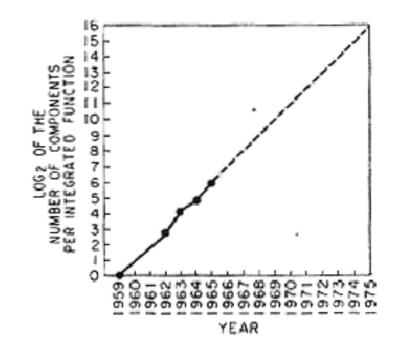

#### Moore's Paper "Cramming more components onto integrated circuits"

Gordon Moore Electronics, Volume 38, Number 8 April 19, 1965

"The future of integrated circuits is the future of electronics itself. The advantages of integration will bring about a proliferation of electronics, pushing this science into many new areas. "

"Reduced cost is one of the big attractions of integrated electronics, and the cost advantage continues to increase as the technology evolves towards the production of larger and larger circuit functions on a single semiconductor substrate."

# Moore's Law

Moore's Law is NOT a Law of Nature It is an Expectation of Continuity of Innovation & Invention

It is a Promise of the Innovation and creativity of our profession & our industry.

7

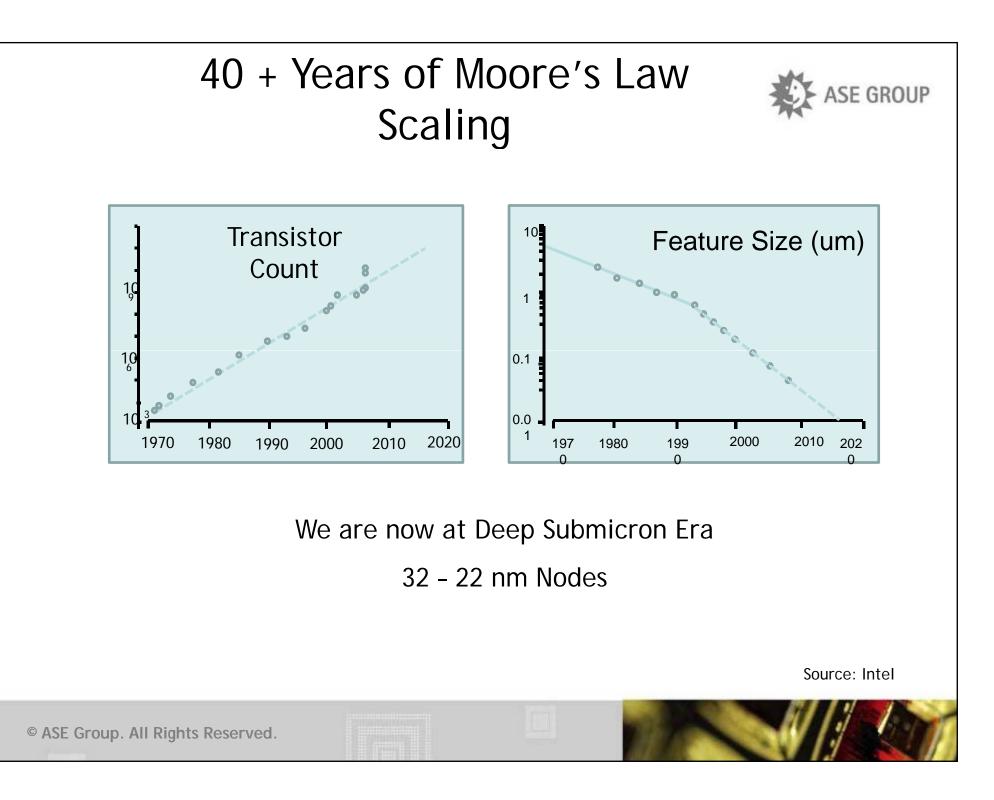

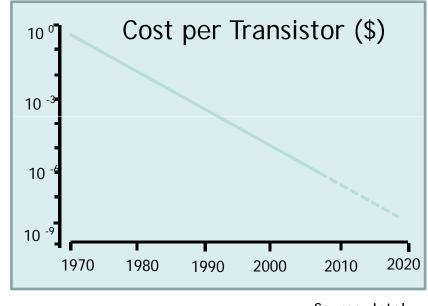

#### 40 + Years of Moore's Law More than 1,000,000 times of cost improvement

Source: Intel

#### "100,000 transistors now cost less than a grain of rice"

**Geoff Colvin**

Fortune magazine Sept 6, 2010 page 64

#### For 40 years Progress was in Predicted Directions

ASE GROUP

- Moore's Law Scaling we knew what was coming next and the path to progress understood

- IC Devices: focus on Fab and Design

- Shrink geometries

- Improve designs for higher density

- Increase wafer size

- Packaging Interconnect: Au Wirebond & FC Solder Bumps

- Follow die shrink

- Signal Integrity

- Power in Energy out Thermal Management ,

- Mechanical Integrity Stress Analysis

- Cost

And together Assembly, Packaging & Test have becomes true Disciplines, recognized Professions and integral parts of the Semiconductor supply chain.

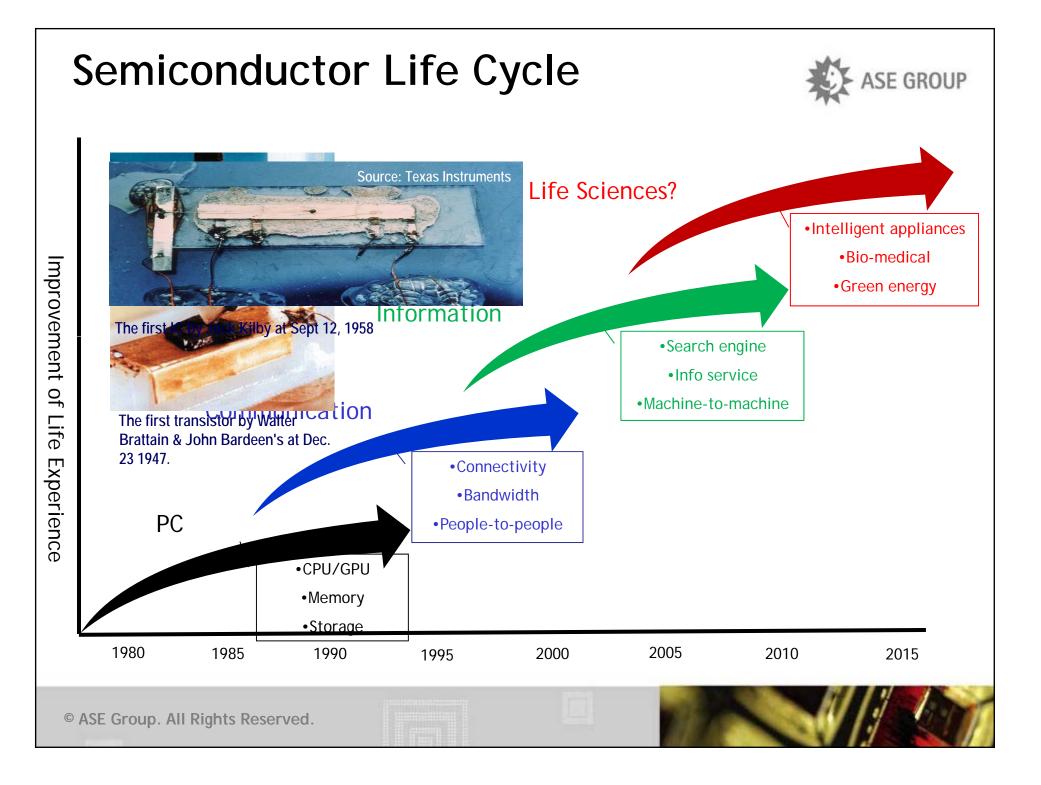

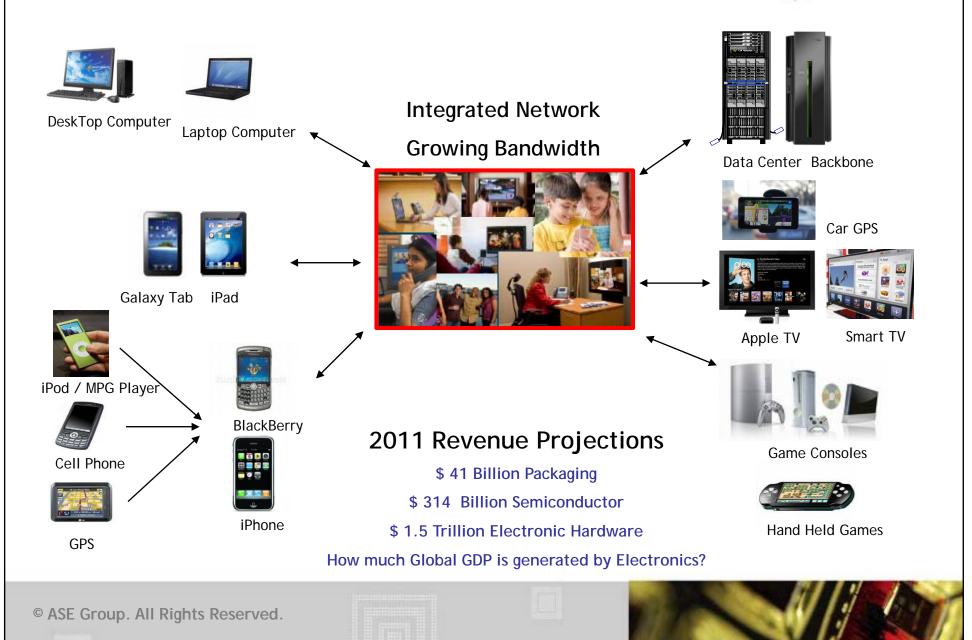

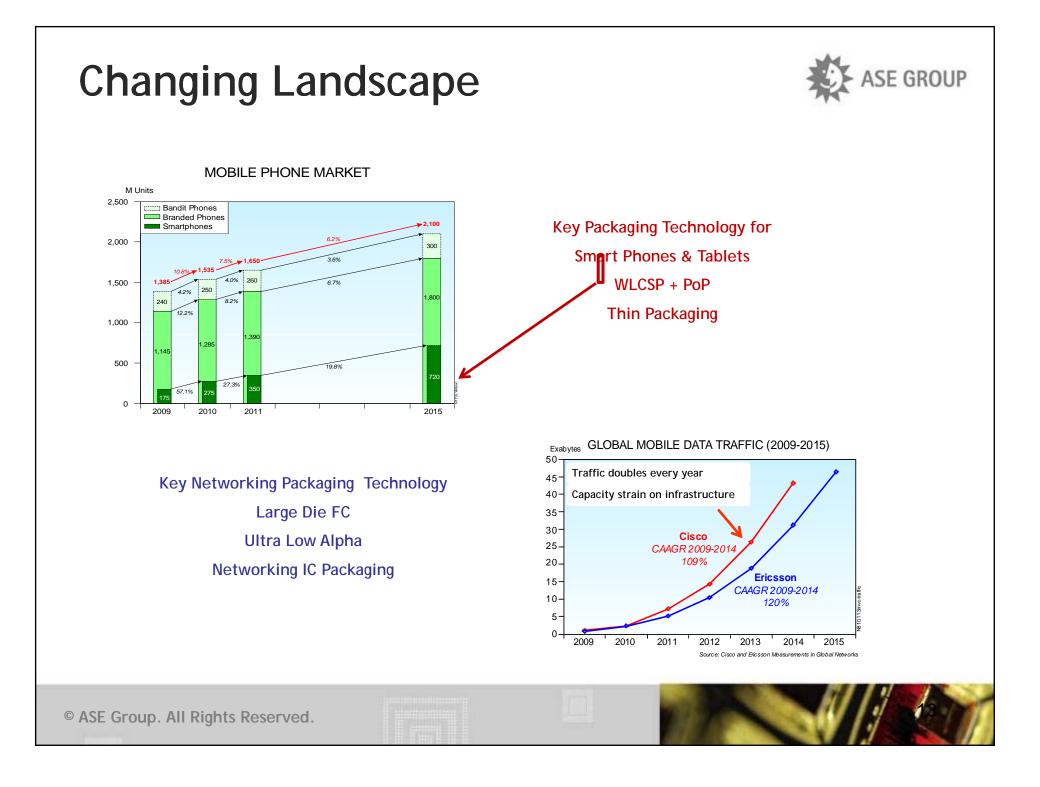

# Global Interconnection - 2010~12

SE GROUP

What Comes Next?

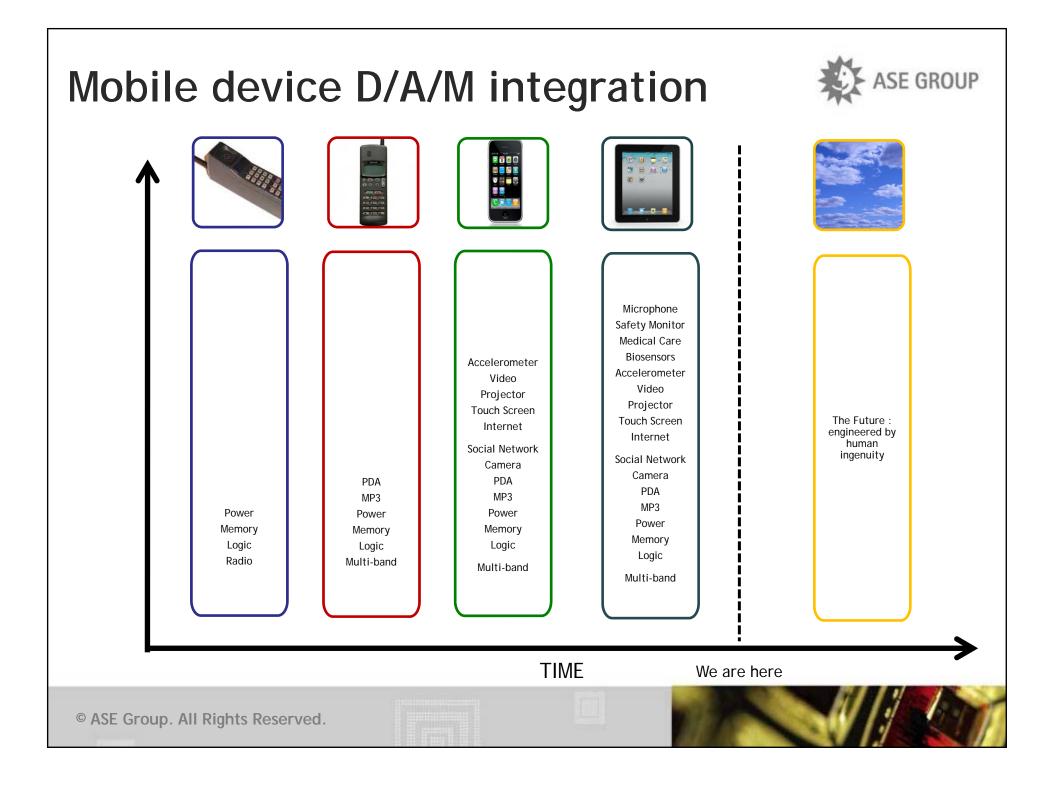

- What are the Electronic Market and Semiconductor Landscapes in the coming Decade? What type of applications will be thriving?

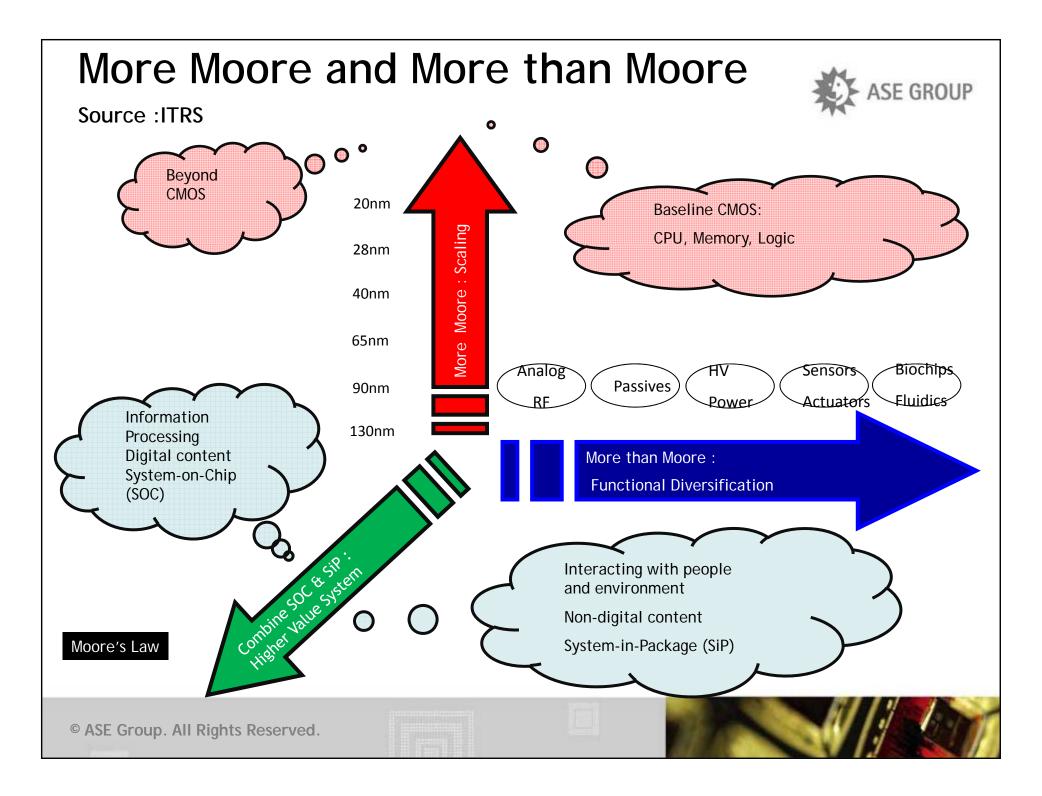

- What technologies from "More Moore and More than Moore" will come forth to meet the market drivers?

- What are the Difficult Challenges for the Back End Industry ? What are the potential Solutions?

- Important questions for us to consider and to debate.

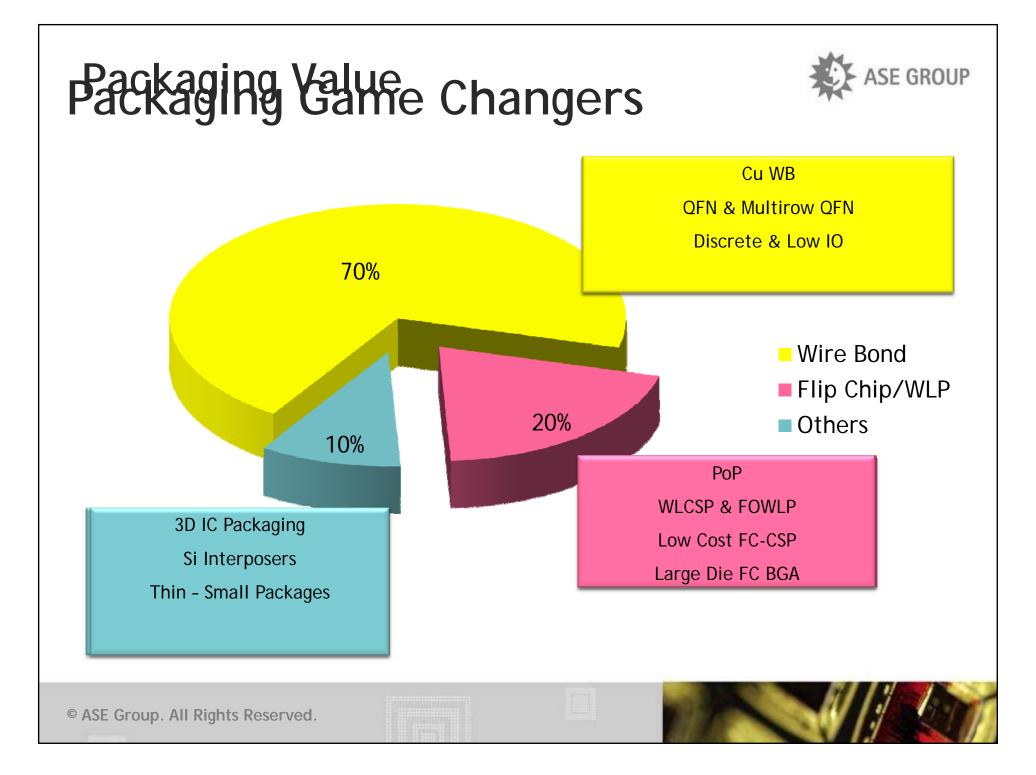

# Game Changing in Packaging

## Wirebond

- Au to Cu Migration driven by sky high Au price

- "last frontier" for cost reduction

- 4 + billion fine pitch wire bond units shipped

- -18 micron wire diameter for fine pitch pad designs

- Conversion gaining momentum

- Difficult Challenges

- High reliability for automotive & networking markets

- Materials & Process Cu-PdCu

- Molding Compound lowering corrosion risk

- Deep Submicron Technology Nodes 28 nm 22 nm ......

- Pad pitch design & constructions

- Equipment and Processes for ultra Low k stress compatibility

# Flip Chip

- From FC BGA to FC CSP & low cost Performance Package

- PoP package

- Bump materials conversion from high lead/eutectic to leadfree solder to Cu Pillar

- -ROHS legislation

- -Pad Pitch reduction for deep submicron

#### Difficult Challenges

- -From lead free to Cu Pillar UBM structure

- -Underfill materials designed for Cu Pillar

- -Interfacial adhesion

- -Low cost bond trace (MUF)materials & process system (including substrate)

- -Thin thin Package

# Packaging Materials Changes

After 40 years or more with only limited changes in materials used, we are now seeing unprecedented changes.

- -In this decade, 100% of packaging materials will change

- -In the next decade, more than half of materials will change again

Assembly & Packaging 2008 ITRS Winter Conference

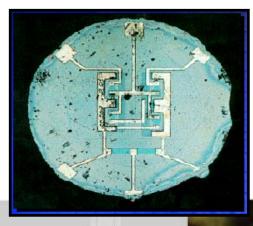

# Growth of Wafer Level Chip Scale Packages (WLCSP)

Year 2000 – WLCSPs were small, low I/O, expensive, and with limited manufacturing infrastructures

Vishay's Power MOSFET - TechSearch

TI Nanostar Digital - ASE

Infineon BAW filters- TechSearch

• <u>Year 2011</u> - Billions shipped, >300 I/Os, Established infrastructure, cost competitive, with high volume manufacturing

Qualcomm 169L WLCSP - ASE

Broadcom 182L 6.5x6.5 WLCSP - ASE

Fujitsu Power Management WLCSP 308 L 7.7x7.7mm -TechSearch - TPSS

361 L WLCSP- ASE

# WLCSP - Fan Out

Multiple approaches to Fanout WLCSP

Infineon's eWLB is first in high volume production: Millions per month

#### • Next Steps

-Multi die & large size

-3D with thru vias - stacked POP

-Panel Process

-Thin package

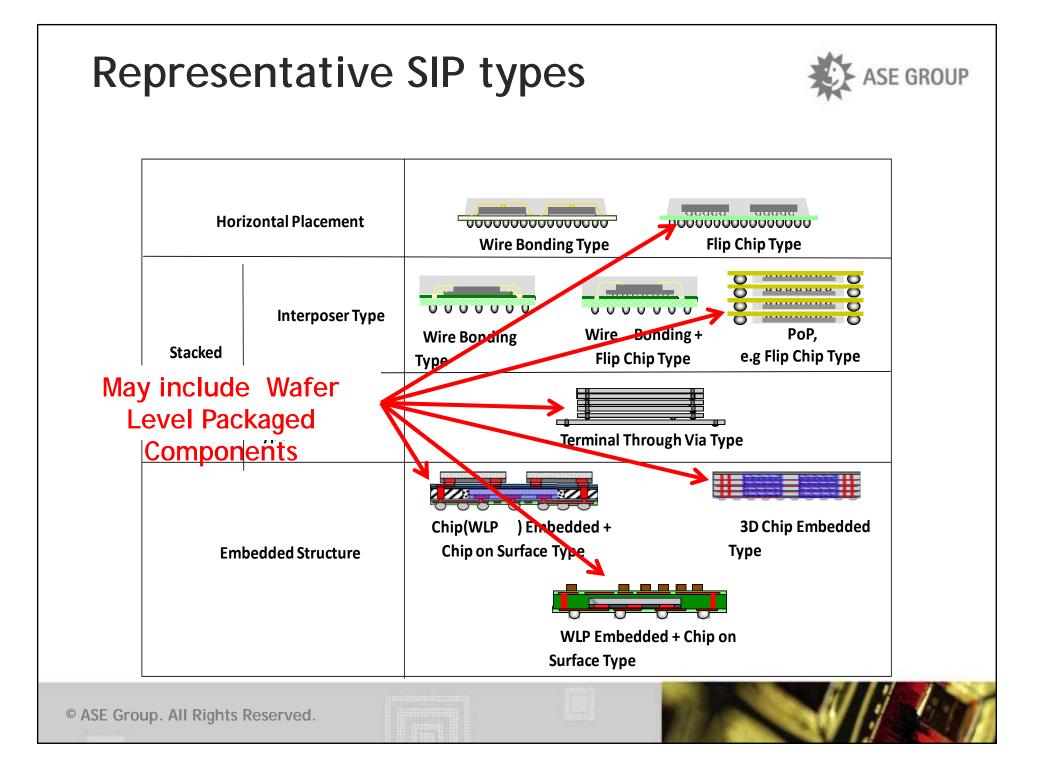

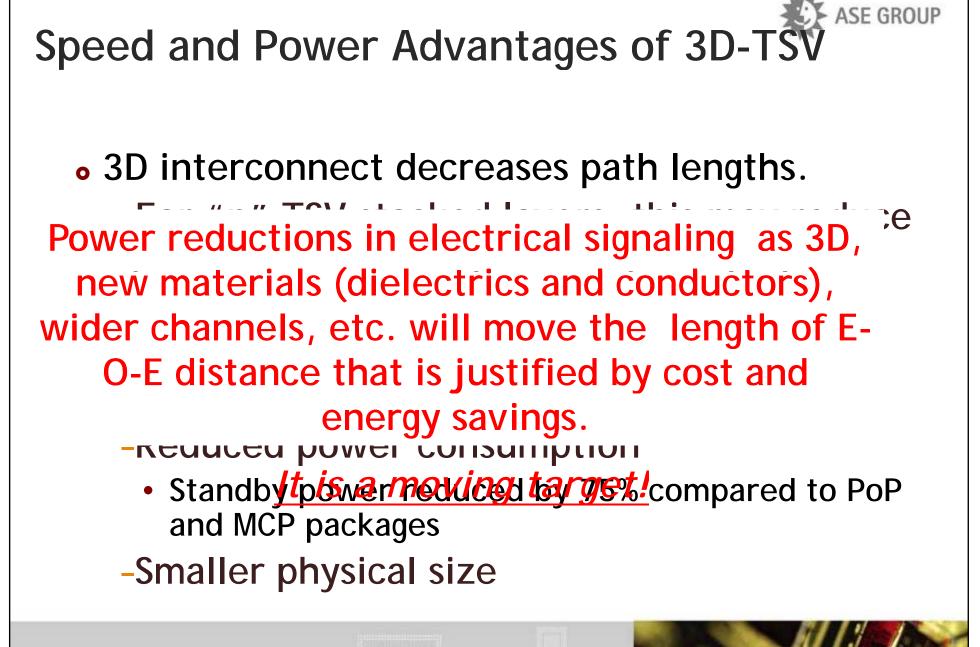

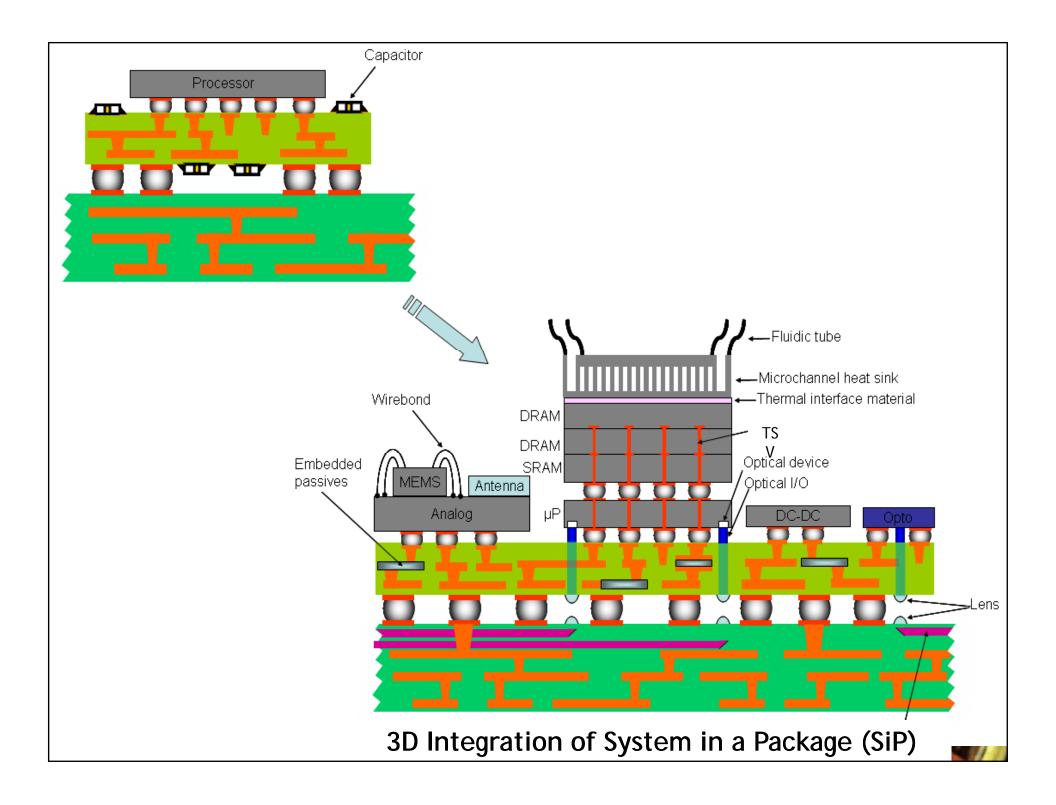

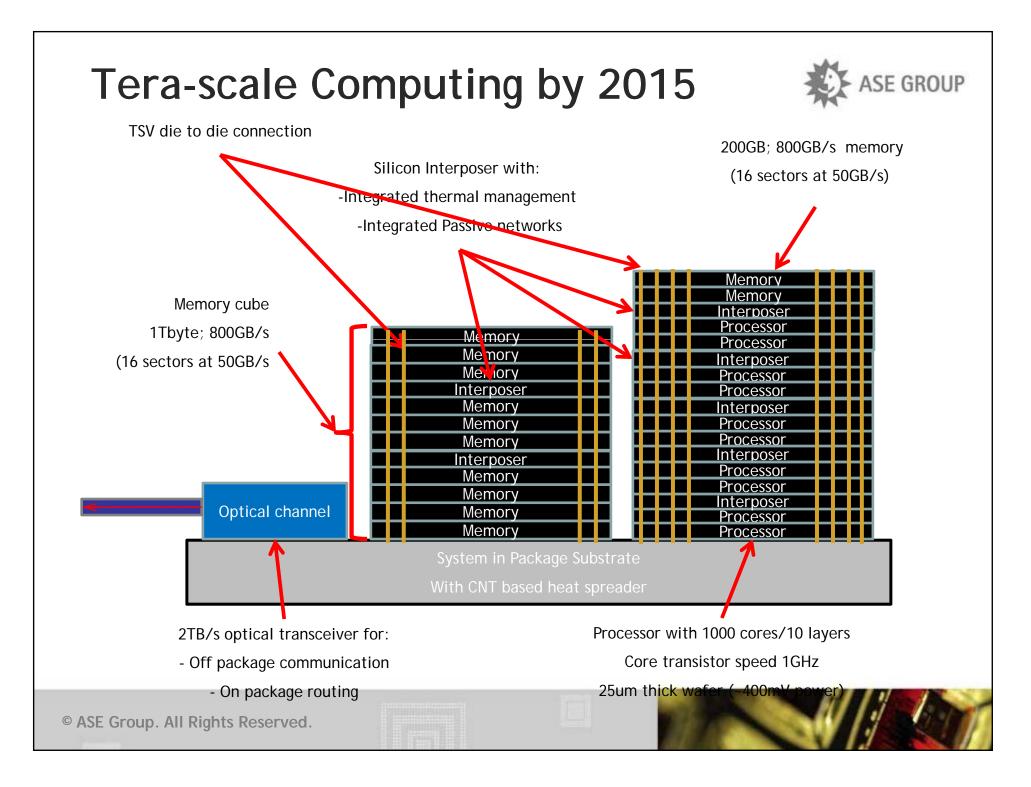

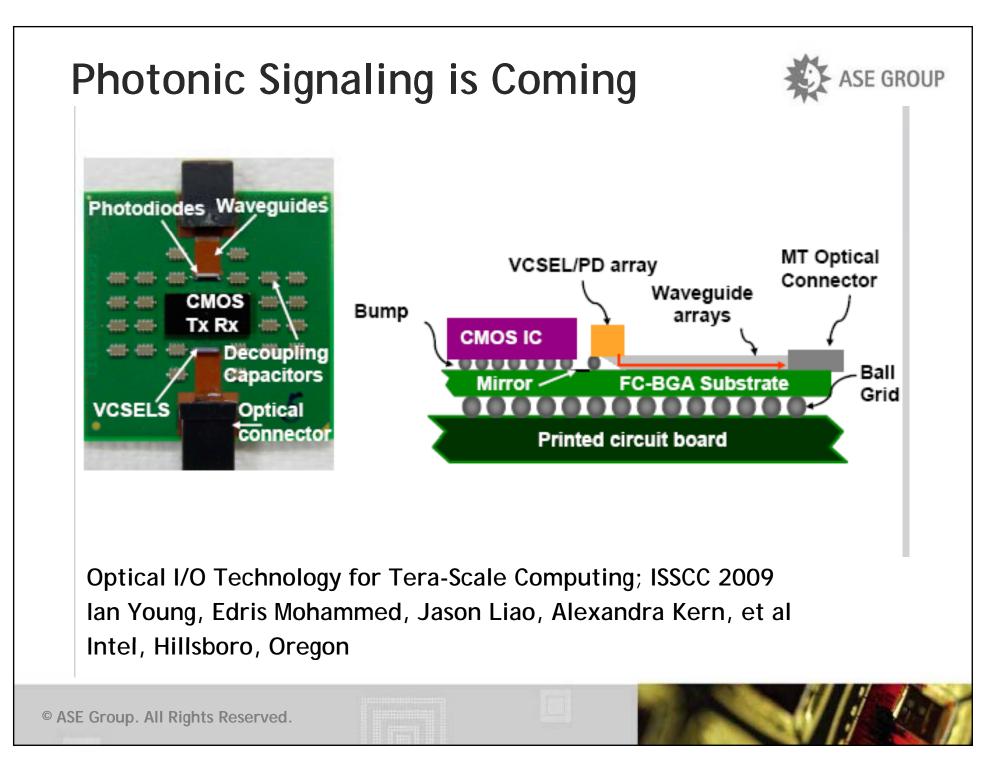

# M&M & MtM Architecture in the Package

One of the most important trends in packaging is the incorporation of system level integration through System in Package (SiP)

This technology enables equivalent scaling through functional diversification

# This added complexity requires change in architecture, materials and processes and equipments

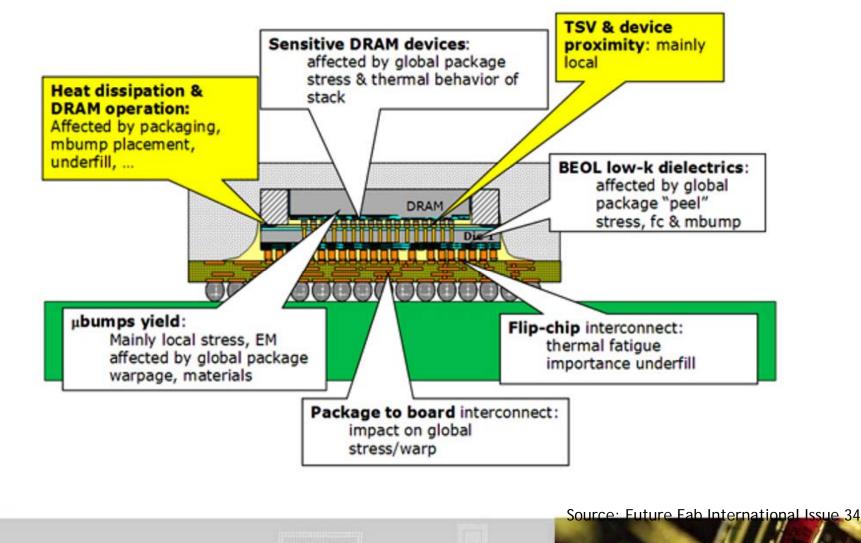

## The 3D Packaging A major Paradigm Change

#### Based upon tool boxes of technologies & infrastructure from Flip Chip and Wafer Level Packaging and Test

#### Packaging Issues impacting Yield and Reliability for Deep Submicron

# Some Examples

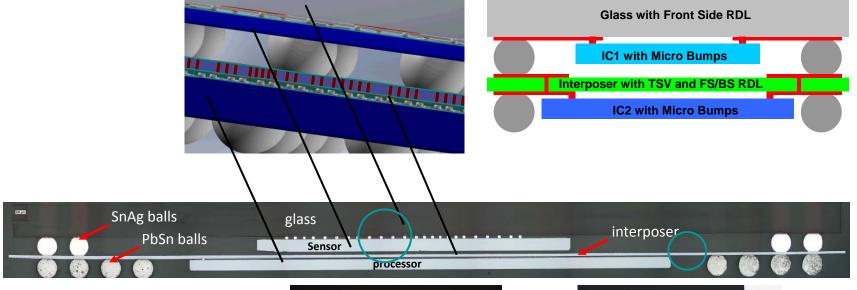

# Some are in Production today Stacked 3D Camera Module

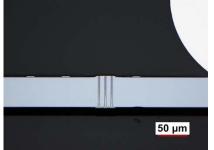

Cross section of the 3D camera stack with 3D stacking, functional diversification using TSV interconnect

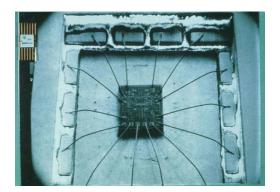

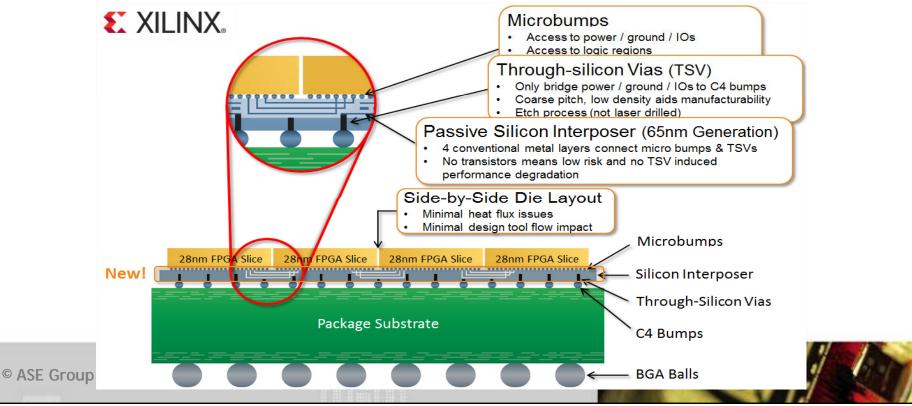

# Xilinx Stacked Si Interposer FPGA

- Interposer substrate has more than 10,000 routing connections

- Compared with standard I/O connections it provides:

- > 100X die-to-die bandwidth per watt

- -one-fifth the latency

## The Best Thing Since Sliced Bread

- Everyone says 3D is the "best thing since sliced bread"

- •We must close the distance between the bread maker, the deli counter, and the sandwich served on the dining table.

- •Whether it is BLT, Roast beef, or peanut butter & jelly, we must deliver our best sandwich to the customer.

- When TSV wafers roll out from the foundries in the not too distant future, the back end of the supply chain must be ready to assembly and test them cost effectively with good yield and cycle time.

# **Special Applications**

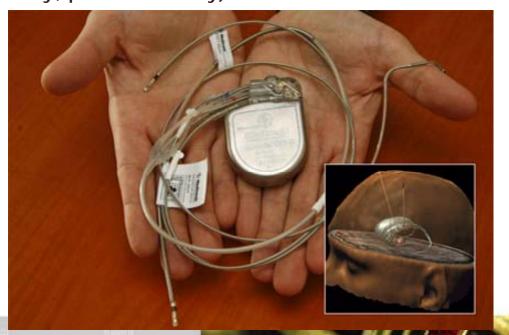

#### Expanded Coverage of Emerging Requirements for 2011: Medical Electronics

- Medical electronics Categories to be addressed:

- -Portable/wearable medical electronics

- -Implantable medical electronics (Parkinson's disease symptom control)

- Selected technical Issues for Medical electronics

- -Power requirements: energy scavenging; wireless radiated power; batteries -Safety issues (voltage, biocompatibility, power delivery)

- -FDA certification

- -Reliability requirements

- -Environmental issues

- -Connectivity (wireless)

- -Optical components (cameras)

- -Microfluidics

- -Implantable micro-robotics

- -Sensors

- -MEMS

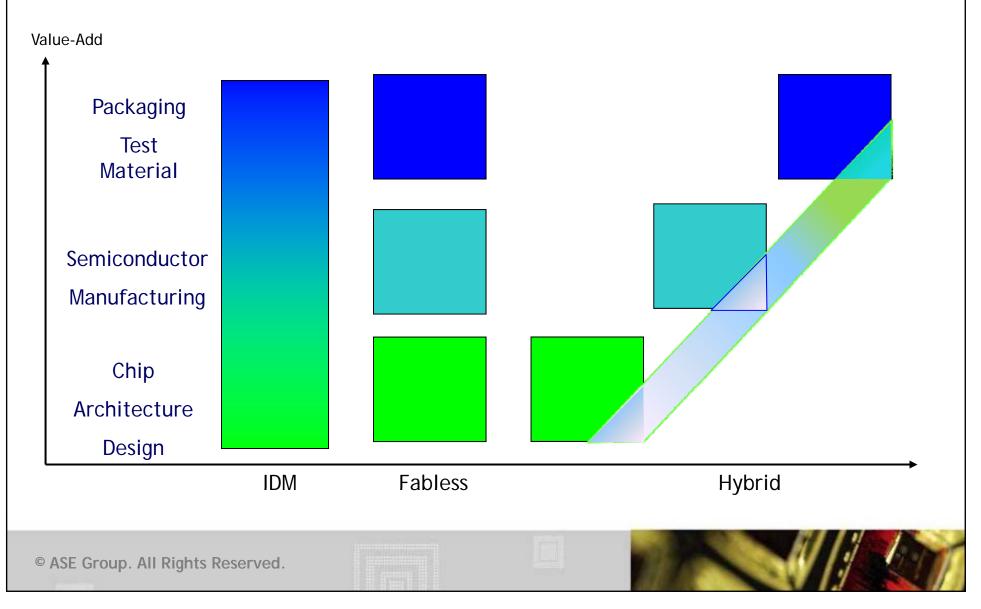

## **Business Models & Infrastructure**

#### Food for Thought

- In our industry the backend is coming to the forefront of the technology supply chain

- Let us not forget that Market is still the deciding factor in what technologies will become mainstream.

- Technology, infrastructure, and business model and profit must come together for the industry and profession to prosper.

# Thank you for your kind attention

Any Questions

© ASE Group. All Rights Reserved.

41

**Aknowledgments**

I would like to thank my colleagues and friends for their generous advice and help in this presentation. I am especially indebted to Patricia Macleod for her excellent editing and support.