#### Test & Reliability Challenges in Advance Semiconductor Geometries

#### **Rancho Bernardo Inn**

Yervant Zorian Fellow & Chief Architect 6/9/13

#### Contents

- Industry Transformational Trends

- More than Moore Challenges

- Impact on Test, Yield and Reliability

- Multi-Die stacks

- Innovation Forward Challenges

- Conclusions

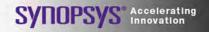

#### Industry Transformational Trends

CLOUD COMPUTING SOFTWARE APPLICATIONS USER EXPERIENCE SHORTENED TIME-TO-VOLUME PRESSURE ON R&D PRODUCTIVITY

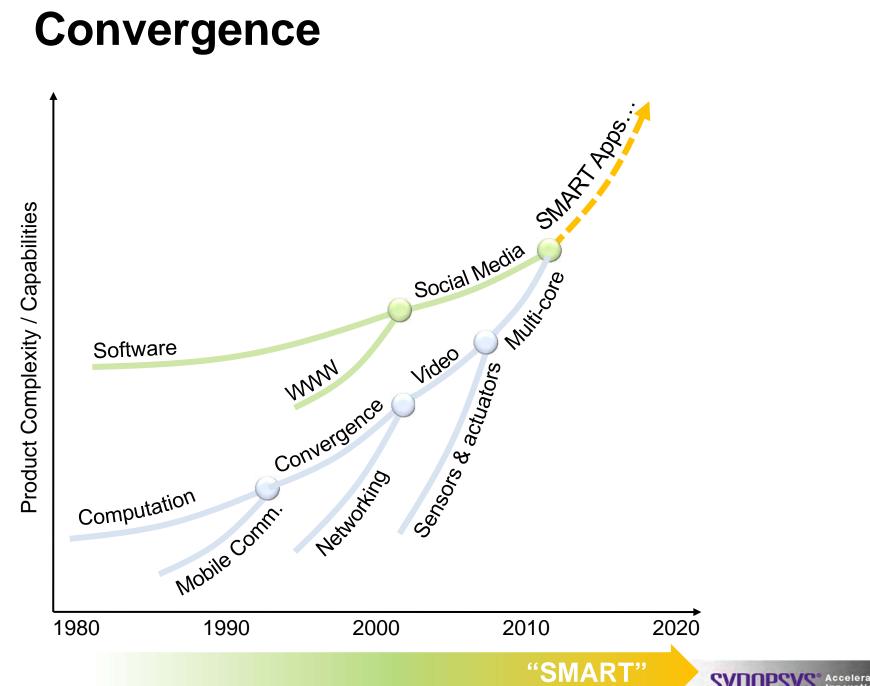

#### **Consumers Driving "Smart" Electronics**

SYNOPSYS<sup>®</sup> Accelerating Innovation

#### **Data Center / Cloud Computing Trends**

## What Happens in an Internet Minute?

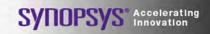

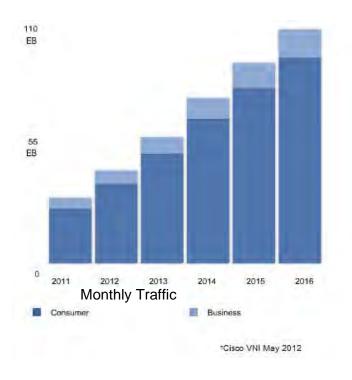

#### **Data Traffic by Forecasts**

- By 2016, total data traffic will be 4x 2011

- By 2016, global IP traffic will reach 1.3 zettabytes annually (110 exabytes per month)

- By 2016, there will be nearly 19 billion global network connections (fixed and mobile); the equivalent of two and a half connections for every person on earth.

- By 2016, there will be about 3.4 billion Internet users, which is more than 45% of the world's projected population.

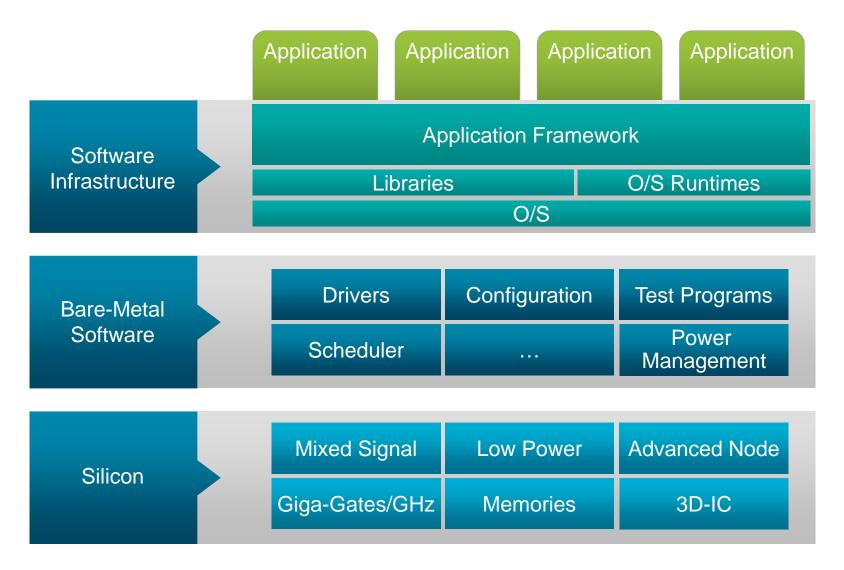

## System

### Integration

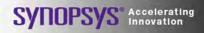

- Before 32nm, new process was introduced every other year

- Since then, a new process every year

#### Silicon Complexity

#### IC Design Expensive and Difficult

|                   | 32/28nm node  | 22/10nm node  |

|-------------------|---------------|---------------|

| Fab costs         | \$3B          | \$4B – 7B     |

| Process R&D costs | \$1.2B        | \$2.1B – 3B   |

| Design costs      | \$50M – 90M   | \$120M – 500M |

| Mask costs        | \$2M – 3M     | \$5M – 8M     |

| EDA costs         | \$400M - 500M | \$1.2 – 1.5B  |

Source: IBS, May 2011

• Intensive customer/partner collaborative developments

#### **Top Semiconductor IP Vendors**

| Rank             | Company        | 2010  | 2011  | Growth | 2011 Share |

|------------------|----------------|-------|-------|--------|------------|

| 1                | ARM Holdings   | 575.8 | 732.5 | 27.2%  | 38.3%      |

| 2                | Synopsys       | 191.8 | 236.2 | 23.2%  | 12.4%      |

| 3                | Imagination Te | 91.5  | 126.4 | 38.1%  | 6.6%       |

| 4                | MIPS Technolog | 85.3  | 72.1  | -15.5% | 3.8%       |

| 5                | Ceva           | 44.9  | 60.2  | 34.1%  | 3.2%       |

| 6                | Silicon Image  | 38.5  | 42.8  | 11.2%  | 2.2%       |

| 7                | Rambus         | 41.4  | 38.9  | -6.0%  | 2.0%       |

| 8                | Tensilica      | 31.5  | 36.3  | 15.2%  | 1.9%       |

| 9                | Mentor Graphic | 27.3  | 23.6  | -13.8% | 1.2%       |

| 10               | AuthenTec      | 19.6  | 22.8  | 16.3%  | 1.2%       |

| Source: Gartner, | March 2012     |       |       |        |            |

#### **Test & Yield**

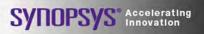

- Increasing design complexity

- Many AMS and Interface IP cores

- Many existing third-party IPs

- Large number of memory instances

- Exploding digital logic size

- Greater than 100M gate designs

- Global design teams

- Increasing test & yield impact

- Quality DPPM

- Total memory bit count

- Yield Optimization

- Designer productivity

- Time-to-market and time-to-volume

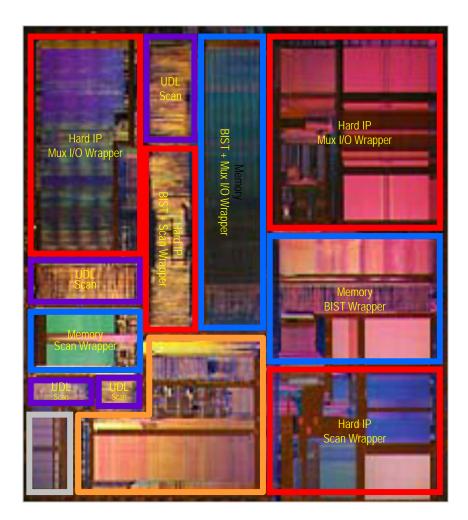

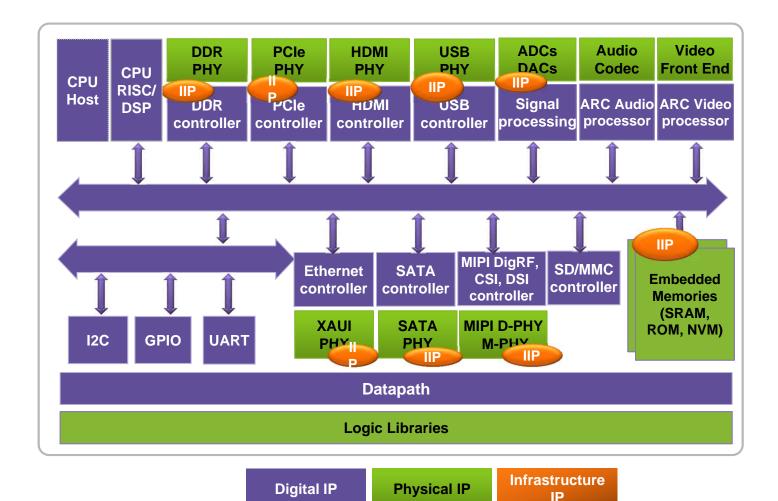

### SoC Test Challenges

on functional performance, area

efficient solution

- hard to detect defects • Need: advanced fault models,

- efficient volume diagnostics & yield analyses

#### **New Defects**

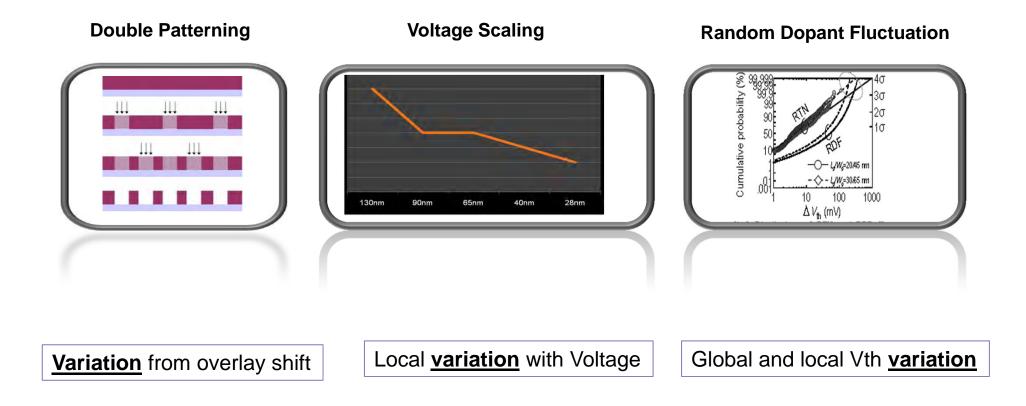

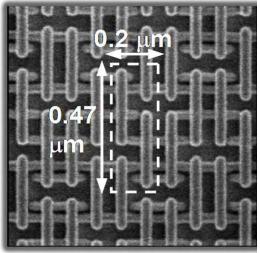

Process variation at 20nm is significant, causing bit failures

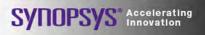

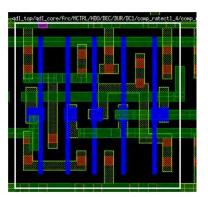

#### Sample SOC: DesignWare<sup>®</sup> IP based

SYNOPSYS<sup>®</sup> Accelerating Innovation

#### **SOC Test Solution**

Accelerate Higher Quality, Lower Cost Test

#### **Hierarchical Design & Verification**

Block B

SoC

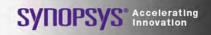

#### **Embedded Memory Is Growing** Key Driver Of Design Success

Need an efficient solution to test, repair and diagnose thousands of on-chip memories

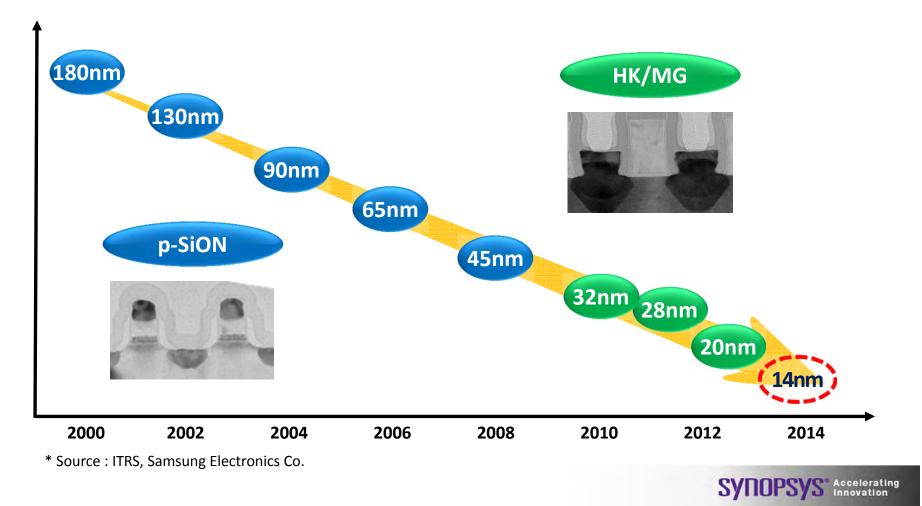

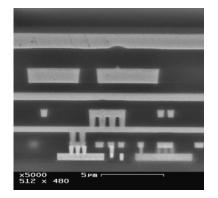

#### **Process Miniaturization Challenges**

- Higher susceptibility and new and speed related fault types

- Requires expanded test to detect new fault types

- Requires high speed test capability

- Higher level of miniaturization

- Needs fault classification and localization

- Needs on-the-fly monitoring and analysis of volume diagnosis data

- Requires better support for yield learning and production ramp up

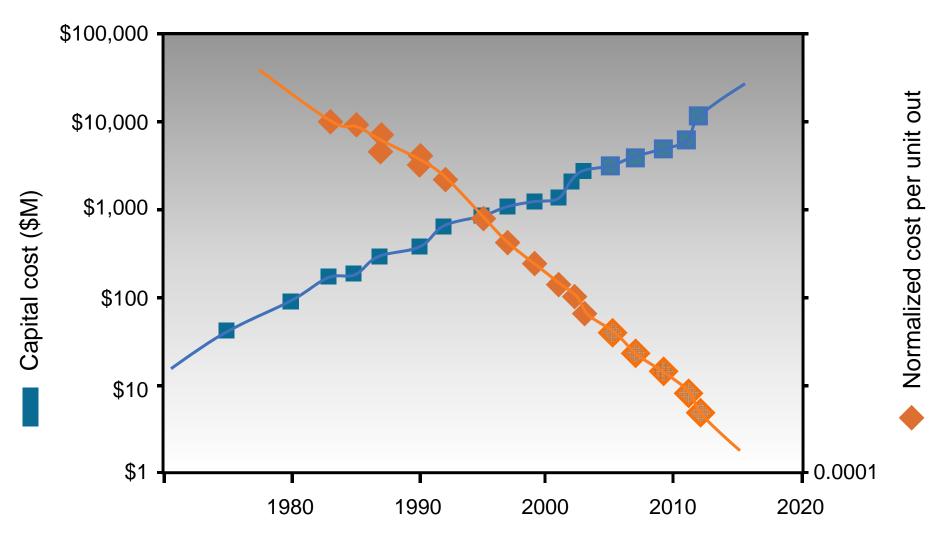

#### **Cost of Unit Out**

Source: IC Knowledge, 2005 & IBS 2008

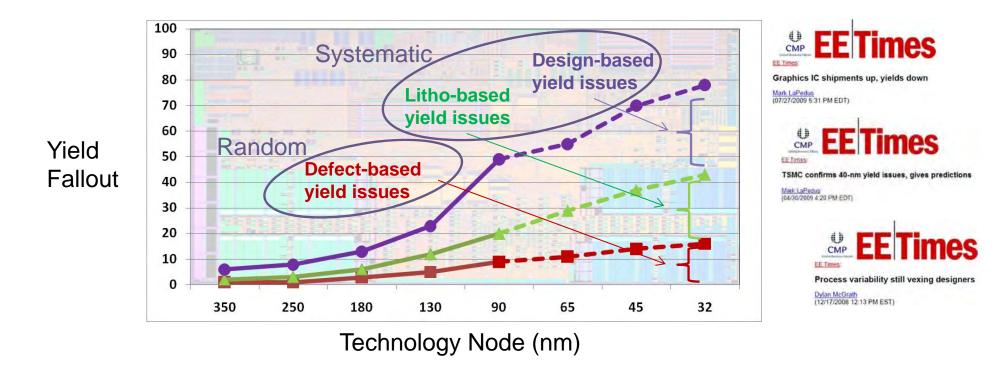

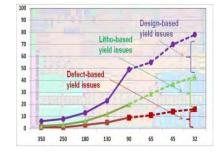

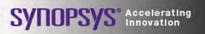

#### **Dramatic Rise in Systematic Yield Issues**

- Cheating with physics induces more process variability at each nanometer node

- Some layout features react strongly to variability causing systematic yield issues

- Each successive nanometer node faces more systematic yield loss

\*\*Chart data source - IBS

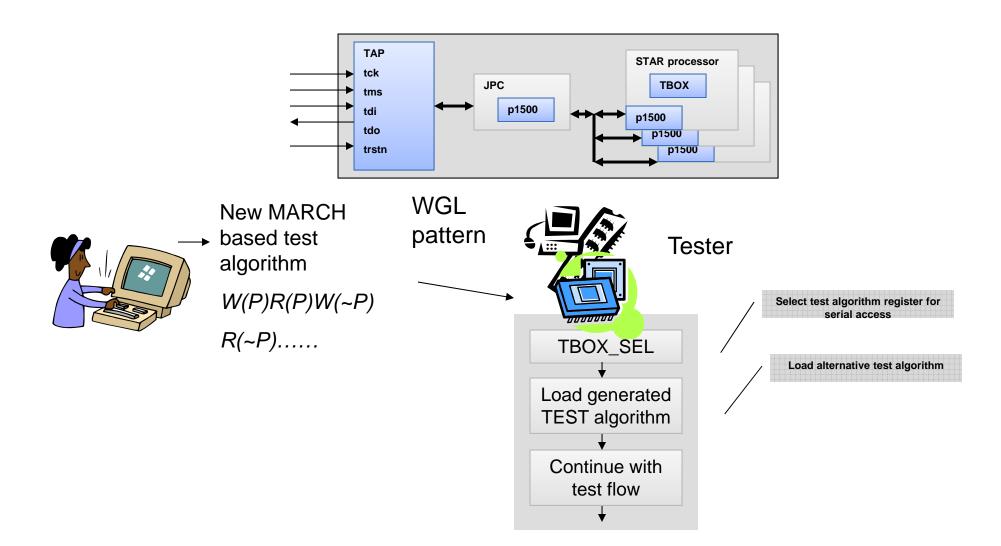

### **Embedded Test & Diagnosis**

High Manufacturing Test Quality

- Out-of-box enhanced test algorithms

- Fully characterized for each advanced node

- Provides 100% fault coverage

- New fault types appear at advanced nodes

- Resistive faults

- Performance faults

- Bridging faults

- Parametric variation

- Generic algorithms are not as granular, resulting in test escapes

- Fault injection based analysis

| Fault Types        |

|--------------------|

| Static/dynamic     |

| Write mask         |

| Weak               |

| Address decoder    |

| Bit-line leakage   |

| Intra & Inter-port |

| Delay coupling     |

| Data setup/hold    |

|                    |

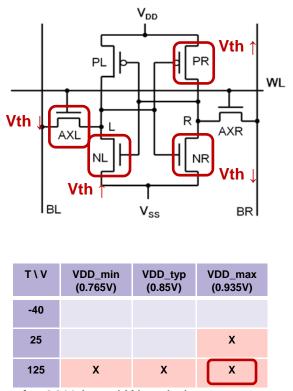

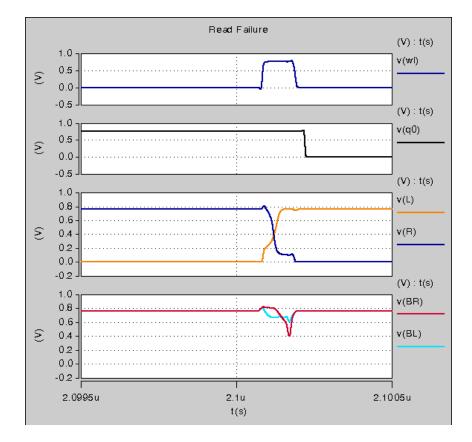

#### **Process Variation- Read Failures in SRAM**

Read Failures should be tested in (VDD\_max,T\_max) corner

- More than 22% variation of Vth brings to a failure

for 30% L and W variation

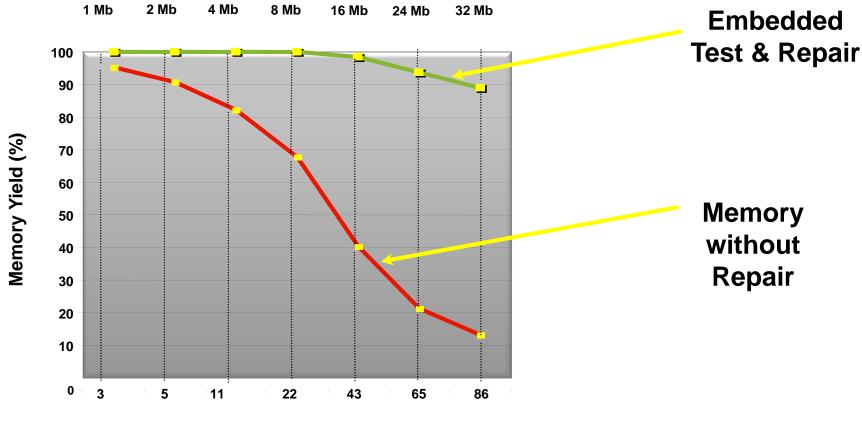

#### **Repair Solution Impacts Memory Yields**

Amount of Memory on the die (Mb)

#### **Repair Efficiency**

- Redundancy allocation algorithm maximizes available repair resources

- Numerous types and amount of redundancies

- Repair methodologies to maximize repair

- Multi-corner cumulative repair

- Multi-zone fuse containers

- In-system periodic repair capability

- Fastest system recovery with multi-power island chips

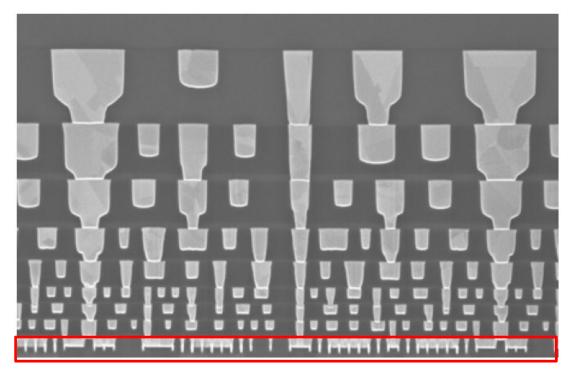

#### Why FinFETs

As predicted for many years, but often postponed, the device level of the chip is finally changing

- "Conventional" planar transistors are reaching the limits of scaling and have become "leaky": They use too much power

- FinFETs enable products with higher performance and lower power consumption

- There are alternatives, but FinFETs promise better continuation of Moore's Law

#### **How FinFETs Work**

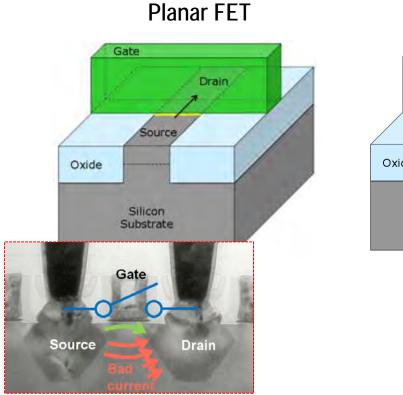

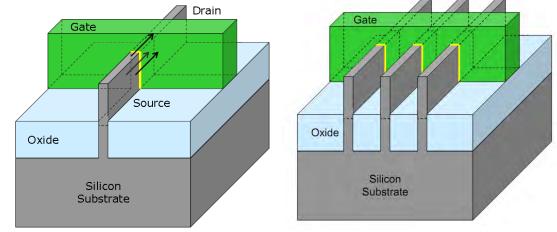

Field effect transistors: The field from the gate controls the channel

FinFET

**Single gate** channel control is limited at 20nm and below

"**Multiple" gate** surrounds a thin channel and can "fully deplete" it of carriers. This results in much better electrical characteristics.

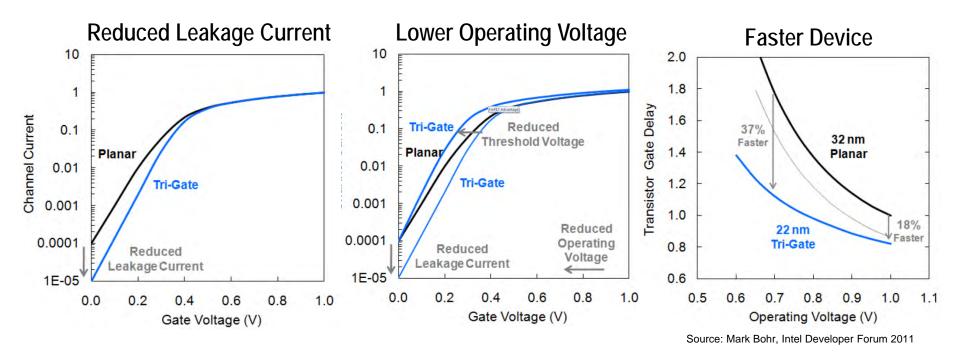

#### **FinFET Advantage: Intel's Perspective**

- Benefit of Intel's FinFET with respect to Intel's 32nm planar technology

- Tri-Gate transistors provide an unprecedented 37% delay improvement at low voltage.

- Tri-Gate transistors can operate at lower voltage, providing ~50% active power reduction

#### **FinFET Impact on Design for Test**

#### **SoC Designers**

Libraries and tools will minimize the impact on digital design.

#### The impact of FinFETs is largest below Metal 1

Double patterning and restricted design rules, while often associated with FinFETs, are not unique to them and also necessary for planar technologies

**IP Designers** Standard cells, memory compilers and custom design are impacted.

**Foundries** Significantly impacted.

#### **FinFETs in SRAMs**

- Special focus on low voltage operation

- Read assist and write assist circuitry to improve robustness

- Compile time options to maximize

- Large SRAM macros provide alternatives to embedded DRAMs

- Enhancing Memory Test & Repair to handle FinFET related failures

- Fault models for planar FETs need to be extended to cover FinFETs

- Further enhancements in compression of test and repair algorithms

**Source**: IBM Research, 2010 Symposium on VLSI Technology

## **Realistic Faults in FinFET SRAMs**

- Traditional faults

- stuck-at fault, stuck-open fault, transition fault, address decoder fault, coupling fault, etc.

- Process variation faults

- Transistor threshold voltage is affected by gate length (L) and fin thickness (Tfin).

- FinFET specific faults

- Opens in FinFET transistor back gate cause delay and leakage faults (transistor threshold voltage is affected by back gate voltage)

#### **Detection Programmable**

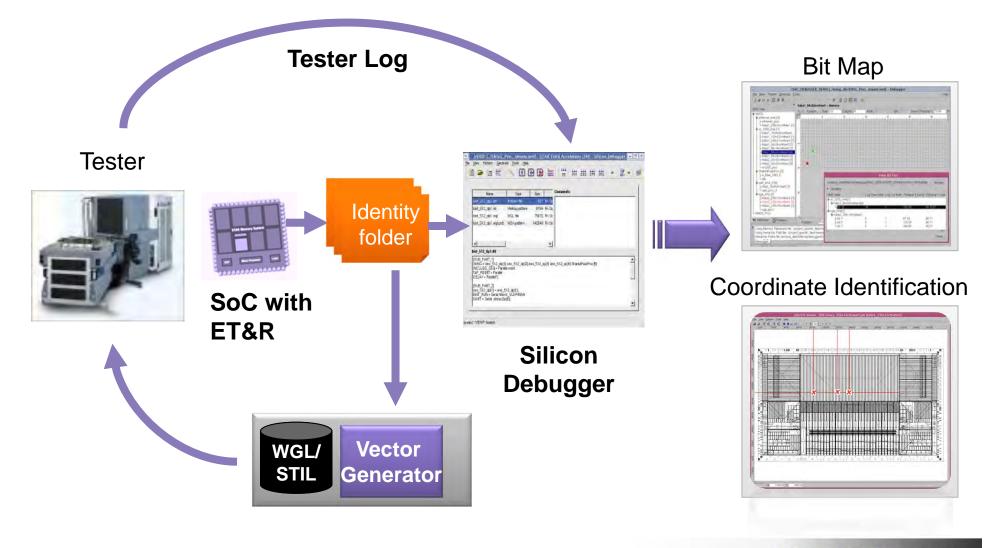

# Automated Rapid Fault Isolation and Identification

SYNOPSYS<sup>®</sup> Accelerating Innovation

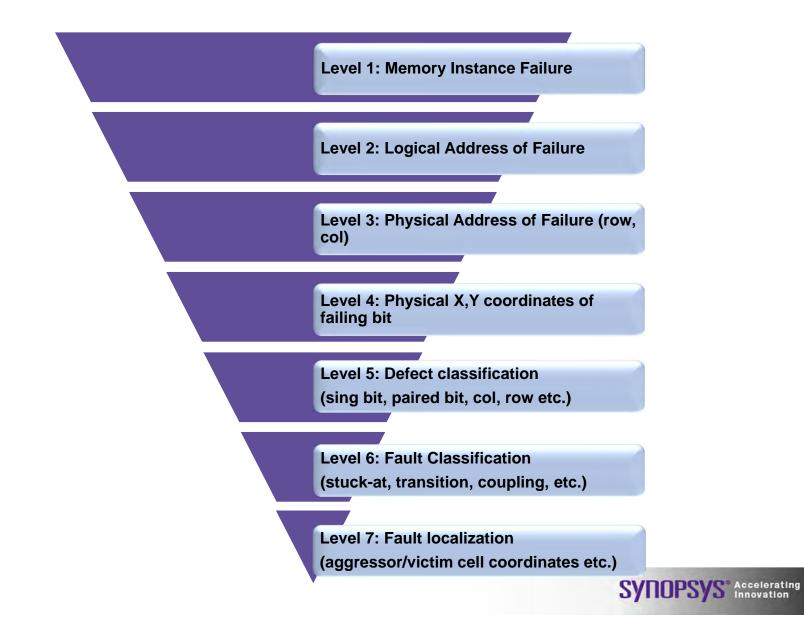

#### **Multi-level Precision Diagnostics**

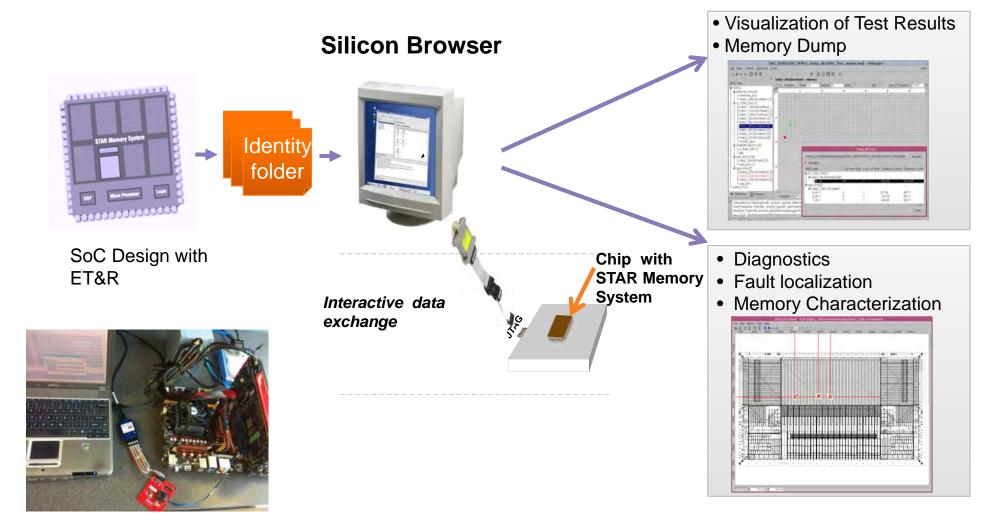

#### **Low Cost Failure Diagnostics Solution**

SYNOPSYS<sup>®</sup> Accelerating Innovation

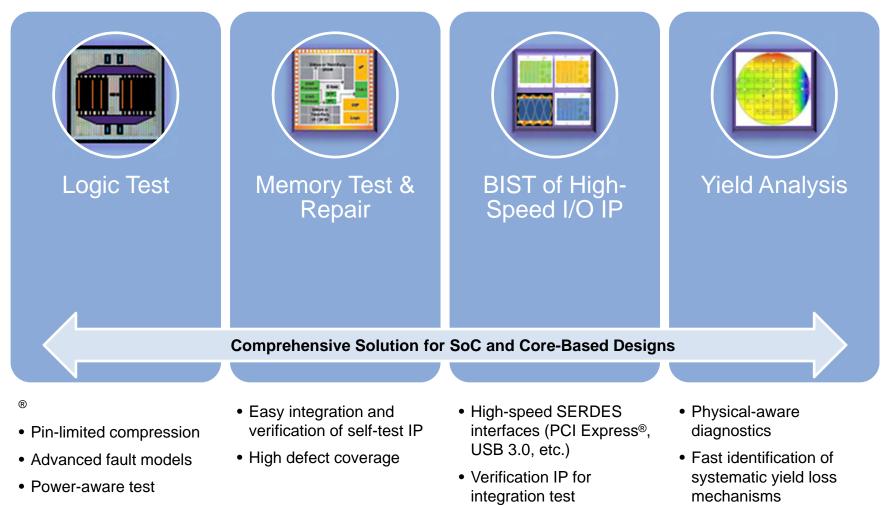

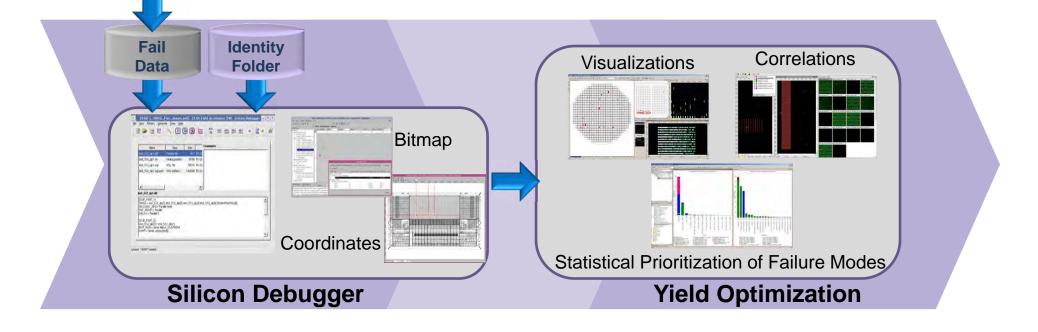

## **Yield Optimization**

Tester

- Embedded Test & Repair Yield Optimization

- Test/Repair IP Insertion

- Vector Generation

- Localization & Signatures •

- - Failure Visualizations

- Cross-Domain Correlations

- Dominant Failure Modes

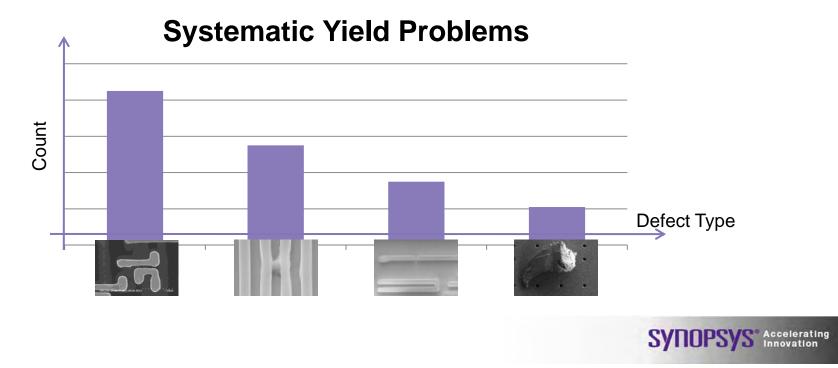

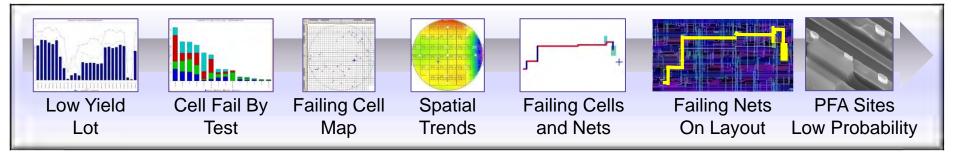

#### Identifying Dominant Failure Mechanism How to get the largest yield improvement

- Rise in systematic defects – Very few dirt particles or fall-on defects

- 100s of failed dies in first silicon

- 10-50 fault candidates per failed and diagnosed die

- 15-20 metal segments & Via per candidate net

• 100x10x10 = 10k sites for FA

- For each silicon lot during ramp

• FA cycle time per site: 4-8 hours – Can manage <10 sites only

### **How Does Volume Diagnostics Help?**

- Volume Diagnostics

- Statistical Analysis of Diagnostics results from multiple failing chips

- Identifies systematic, yield-limiting issues by using design data

- Produce outputs for Physical Failure Analysis (PFA)

## **Design-Centric Volume Diagnostics**

#### **Multi-Tool Manual Flow**

#### 2-3 Weeks

\*PFA – Physical Failure Analysis

- An order of magnitude faster systematic failure localization

- Prioritization of failure types based on yield impact

- Success in capturing dominant systematic failure mechanisms

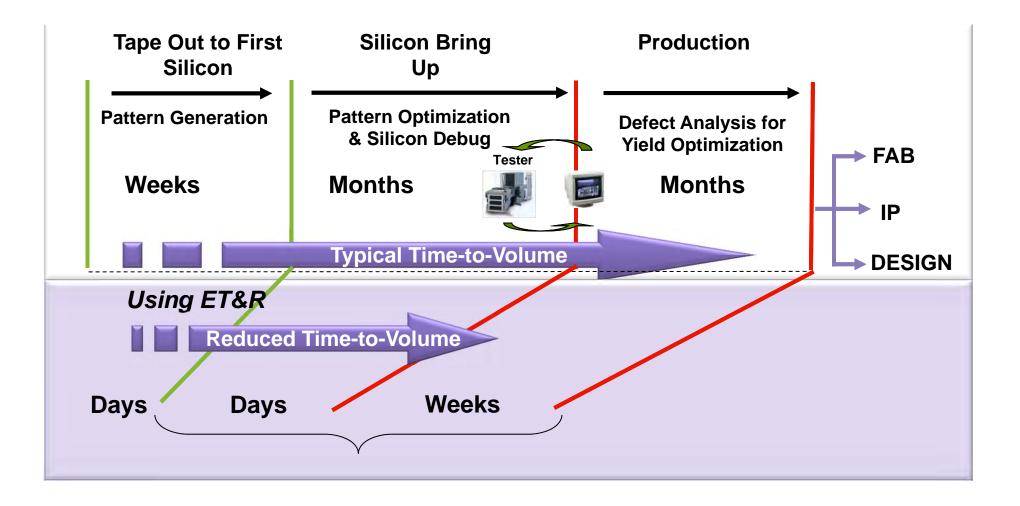

### **Shortest Time to Volume**

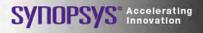

### **Trends for 3D Stacking**

SYNOPSYS<sup>®</sup> Accelerating Innovation

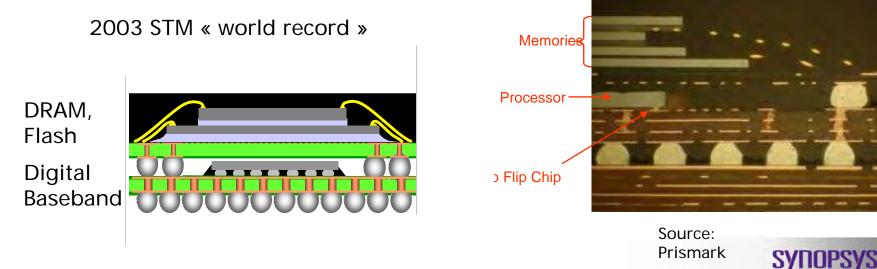

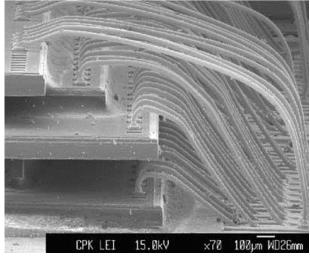

## **3D Packaging in cell phones**

- 3D packaging used in cell phones for several years

- Stacked dies with Wire bond

Memory

- Package on Package (PoP)

Accelerating Innovation

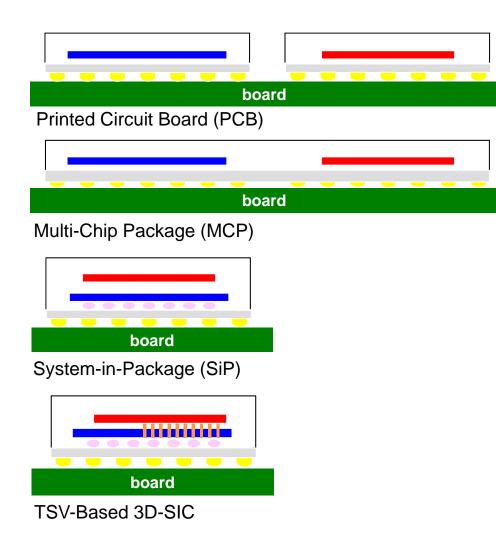

### **Beyond SoC: SiP Alternatives**

- SoC: System-on-Chip. Integrate combinations of logic, processor, SRAM, DSP, A/RF, DRAM, NVM

- SiP: 3D Stacked Dies

- 1. Non-TSV

- bare die stacking: wirebond, flipchip, embedded die substrate

- package stacking: PoP, PiP

- 2. TSV

- via first, via middle, via last

#### **Evolution in 3D Technologies**

#### non-TSV

#### Limitations

- Peripheral bonds only

- Long wire bonds (high inductance, high crosstalk, low speed interconnect)

- Limited to low-density interconnects and with specific I/O pad routing

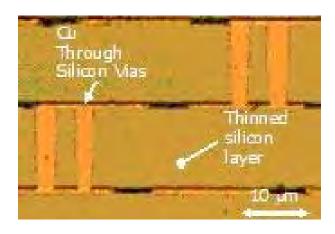

#### TSV

#### **Benefits**

- Area placement

- Excellent electrical characteristics

- High densities

- Orders of magnitude higher interconnect densities between dies

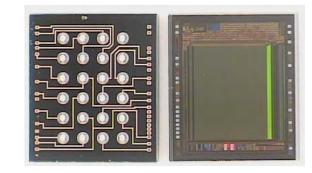

#### **Through Silicon Via Pros and Cons**

- Pros

- Allow even smaller package outline

- No pad extension needed

- Lower sensitivity to foreign material at Camera assembly

- Wire bonding compatible layout

- Reflow process compatible

- Better interconnect routing capability

- Cons

- More complex technology

- Glass

- Silicon

- Back-end processes

- Cost

Through via contacts From top to bottom

## 3D Stacking is Not New...<sup>But TSVs Are!</sup>

#### Multi-Chip Packaging

- Dense integration

- Heterogeneous technologies

#### Vertical Stacking

- Denser integration

- Smaller footprint

- Through-Silicon Vias (TSVs)

- Even denser integration

- Increased bandwidth

- Increased performance

- Lower power dissipation

- Lower manufacturing cost

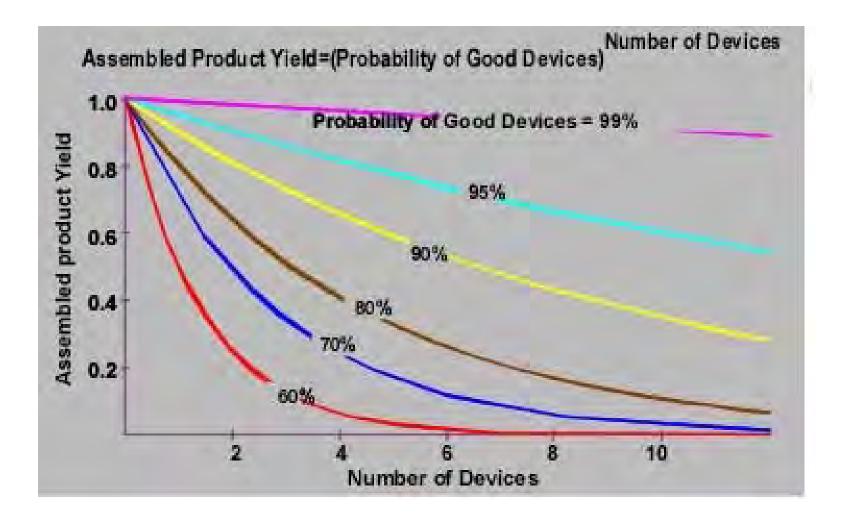

### **Yield Implication Due to 3D Levels**

SYNOPSYS<sup>®</sup> Accelerating Innovation

### **Tests for 3D Induced Effects**

- Test Coverage for TSV Interconnect

- Defect Coverage for due to

- Thinning Process

- Thermal Dissipation

## Known Good Die Challenge:

Conventional burn-in challenge

- $\odot\,$  Full speed test and burn-in prior to packaging

- $\odot$  Higher pin count with finer pitch

- $\odot\,$  Increased functionality and frequency

- KGD requires

- $\odot\,$  Extra stress during probe, carriers, or WLBI

- Necessary for SiP productio

## Wafer Level Burn-in and Test

Greatly simplifies backend IC fabrication line

#### Wafer-level burn-in and test

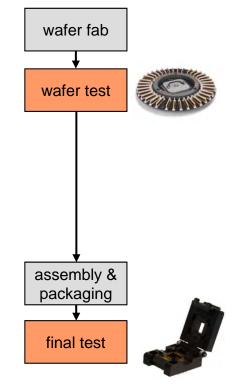

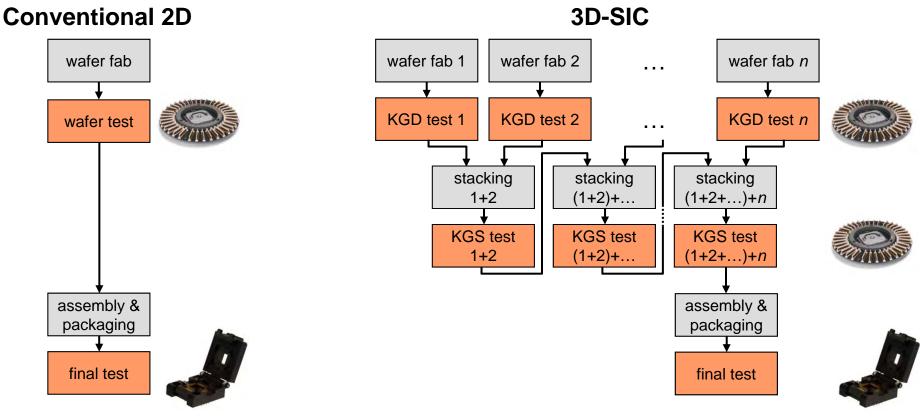

### **Conventional 2D Test Flow**

#### **Conventional 2D**

- Main role of Final Test (FT): guarantee outgoing product quality

- Main role of Wafer Test (WT): prevent unnecessary package cost

- WT executed only if benefits exceed costs:  $(1-y) \cdot d \cdot p > t$

with

- y: fabrication yield

- *d*: fraction of faulty products that the WT can <u>d</u>etect ('test quality')

- *p*: <u>preventable product cost</u>

- *t*: <u>t</u>est execution cost

### 2D Test Flow vs. 3D Test Flow

- Terminology

- **KGD** : Known-Good Die test

- KGS : Known-Good Stack test

Test access is distinctly different! Test contents might be different.

Better name would have been "Known-<u>Bad</u> Die/Stack" test ☺

#### **Required Infrastructure**

- Language for test description transfer

- Core Test Language, CTL (IEEE Std. 1450.6) [Kapur 2002]

- On-chip Design-for-Test for electrical test access

- Test wrappers

- Around cores: IEEE Std. 1500 [Da Silva et al. 2006]

- Around dies: to be developed

- Around full-stack product: IEEE Std. 1149.1 [Parker 2003]

- Test Access Mechanisms

- Intra-die: test bus, TestRail [Marinissen et al. ITC'98]

- Inter-die: TestElevator

• EDA support for automated 'test expansion' from module-level test into chip-level test

### All What Is Known – And Some More...

- All manufacturing defects that can occur in conventional 2D chips, can also occur in 3D-SICs

- Hence, we need to apply all known test methods

- Logic: stuck-at, transition, delay, VLV, ...

- Memory: array, decoder, control, data-lines, ...

- Analog: INL, THD, ...

- In addition:

- 1. Tests for new intra-die defects

- 2. TSV interconnect tests

### **Advanced TSV-Interconnect Test**

- Advanced fault models for TSV interconnects

- Delay faults

- Testing of *infrastructure* TSV interconnect

- Power/ground TSV interconnects

- Clock TSV interconnects

- TSV interconnect *Redundancy & Repair*

- Crank up bonding yield

- Evaluate benefit/cost trade-offs

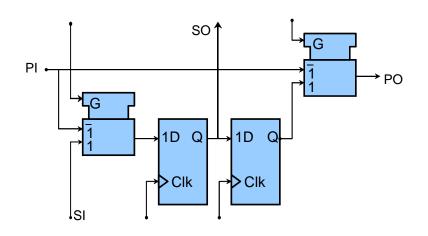

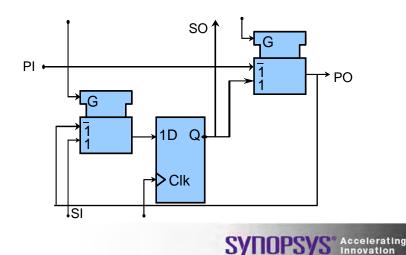

### Wrapper Style: P1838

#### IEEE Std. 1149.1 ('JTAG')

- Interface

- Single-bit for data and control: TDI-TDO

- Wrapper cells with double FFs

- No ripple-through during shift

- Control via TAP Controller: fixed-protocol Finite State Machine

#### **IEEE Std. 1500**

- Interface

- Mandatory single-bit: WSI-WSO

- Optional n-bit: WPI-WPO

- Scalable wrapper cells

- Single-FF cell most common

- Control via flexible instruction shift register

### The Role of Advanced DfT Techniques

- **RPCT Reduced Pad-Count Testing** Reduce width of scan-test interface

- Useful to limit additional probe pads for KGD testing

- Same test data volume: smaller interface  $\rightarrow$  longer test length

#### • TDC – Test Data Compression

Reduce off-chip test data volume by on-chip (de-)compression

- Definitely applicable to 3D-SIC 'super chips'

- Great combination with RPCT

- BIST Built-In Self-Test

On-chip stimulus generation and response evaluation

- Reduces off-chip test data volume to (virtually) zero

- Narrow TAMs / TestElevators

- Protection of proprietary test contents execute and trust

- Especially attractive for memory dies MBIST

### **3D Test Resource Partitioning**

- 3D-SICs offer new opportunities to system architects

- 3D-SICs offer new opportunities to DfT architects

- Which DfT resource to put in which die?

- $\Rightarrow$  Test Resource Partitioning

- Example: DRAM-on-Logic

- 1. MBIST in DRAM Die

- "3D-Prepared" DRAM

- Proprietary memory content does not need to be released

- 2. MBIST in Logic Die

- Drop-in MBIST module provided by DRAM vendor

- MBIST implemented in logic process technology

- Communication over TSV-based interconnects

### **Reliability Faults**

- Intermittent Faults:

- unstable hardware activated by environmental changes (lower voltage, temperature)

- often become permanent faults

- identifying requires characterization

- process variation main cause of IF

- Transient Faults:

- occur because of temporary environmental conditions

- neutrons and  $\alpha$ -particles

- power supply and interconnect noise

- electromagnetic interference

- electrostatic discharge

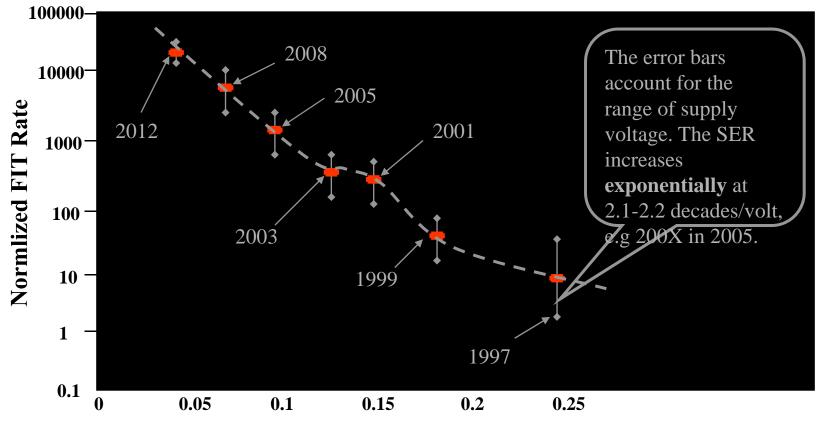

## **Reliability Faults (cont)**

- Infant Mortality

- rate worsens due to transistor scaling effects and new process technology and material

- Aging Induced Hard Failures

- performance degradation over time (burn-in shows)

- degradation varies over chip-chip and core-core

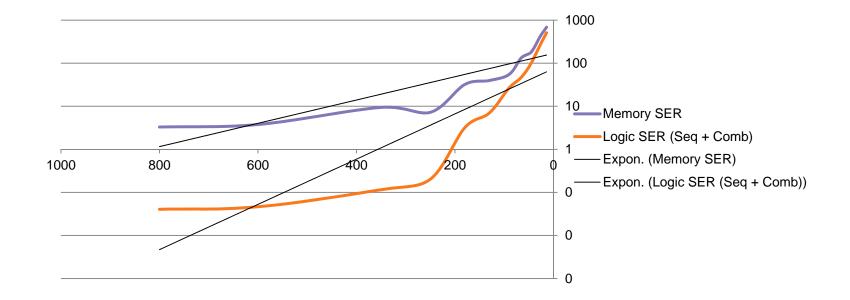

- Soft Errors

- Random logic still at risk

- RAM decreasing SEU per bit

- Low Vmin increases bit failures in memories

- Transient Errors, such as timing faults, crosstalk are major signal integrity problems

## **Field Reliability Challenge**

From AMD, Intel, Compaq, 1999

SYNOPSYS<sup>®</sup> Accelerating Innovation

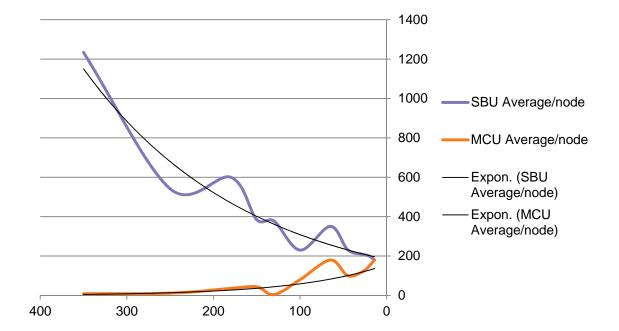

#### **MCU Growth Over Technology Nodes**

Source: iRoC

#### **SER Growth at SOC Level**

Source: iRoC

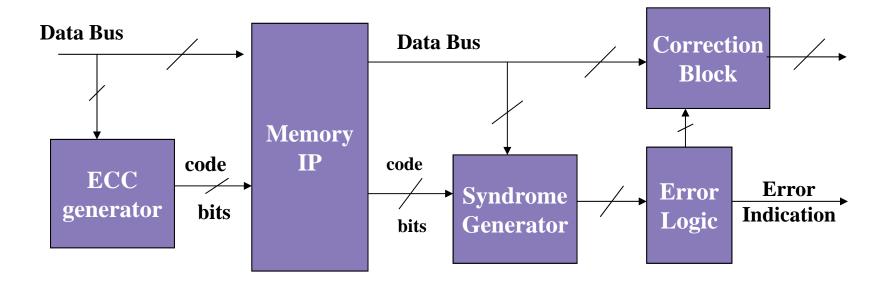

## **Robustness IP for ECC**

• Standard ECC architecture provides single bit repair

Accelerating Innovation

SYNOPSYS

• RAM multi-bit upset probability depends on cell to cell distance

# Thank You

#### SYNOPSYS® Accelerating Innovation