June 8 - 11, 2014 | San Diego, California

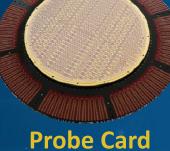

## Conductive Paste-Based Interconnection Technology for High Performance Probe Card

Sang-il Kwon Eddy Kang TSE Co., Ltd.

#### **Overview**

- Introduction of TABP Technology

- Key Technology of Core to Core Interconnection

- Test Results & Application Examples

- ✓ Electrical & Thermal Reliability of Core to Core Interconnection PCB by Actual Application

- Probe Card Application by Design Rules

- Conclusions

## TSE Who we are

#### TSE Co., Ltd.

**Memory Test Board**

Load Board

Test Socket

## ŚŴĨŴ

#### **IEEE Workshop**

TigerElec

**TaisElec**

June 8-11, 2014

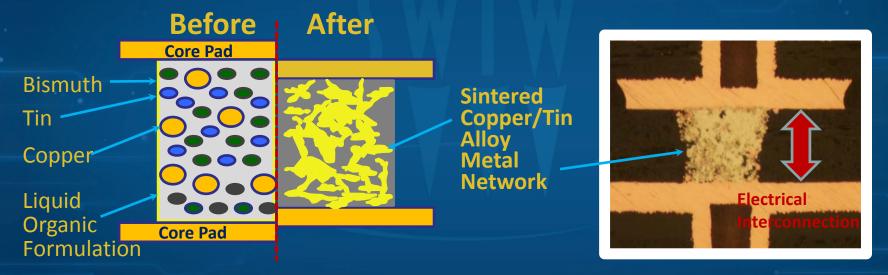

#### What is TABP?

## TABP = "TSE Advanced Bump PCB" → Core to core interconnection PCB

<Structural Change of Conductive

Paste by Sintering>

<Section View>

S. Kwon and E. Kang

June 8-11, 2014

## **Advantages of TABP**

- Free of Thick Board Drilling

- Free of High Aspect Ratio Via Hole Plating

- Reducing Complexity of Back Drilling

- Enhance Fabrication Capability for Fine Pitch HDI PCBs

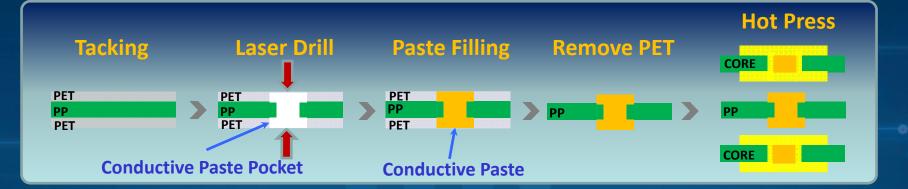

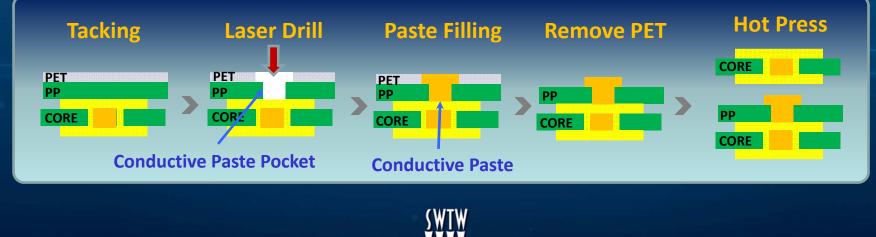

## **TABP Fabrication Process Flow**

#### • Prepreg Tacking Type

#### • Core & Prepreg Tacking Type

## Key Technology

#### Electrical Conductivity

(TSE Advanced Bump PCB)

TABP

#### Thermal Reliability

- Perfect Sintered Alloy Structure

- Sufficient Amount of Paste Fill

- Optimized Forming of Conductive Paste Pocket

- Withstanding Thermal Stress

- ✓ Sintered Alloy

- ✓ Bonding Layer

- Sufficient Resin at Bonding Layer

- Optimized Material, Layup & Design

## **Electrical Conductivity**

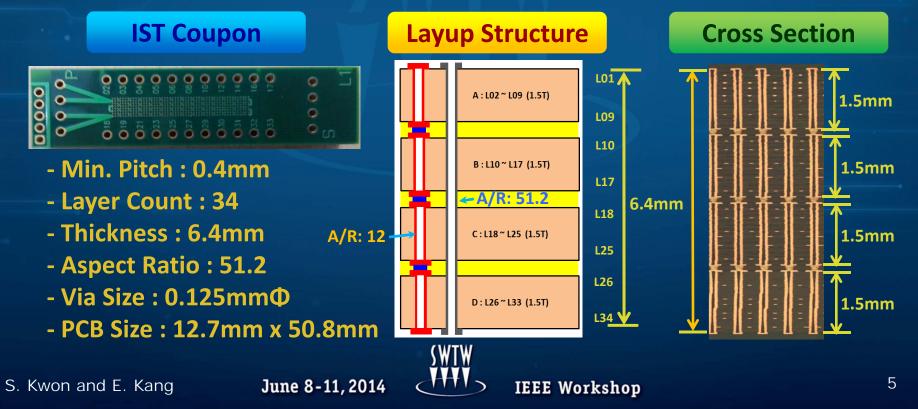

#### Coupon Board

- 0.5mm Pitch 12DUTs & 0.4mm Pitch 12DUTs

- Each Via has 1 TABP interconnection.

- BGA Count of Each DUT = 1,024

- Each Via in Same DUT connected by Daisy Chain

- PCB Thickness = 1.2mm

#### DC Interconnection Resistance Values

|                   |      |                                      | 그는 그는 것이 모두는 것이 가지 않는 것이 같은 것이 많은 것이 많이 많이 많이 했다. |

|-------------------|------|--------------------------------------|---------------------------------------------------|

| <b>BGA Pitch</b>  |      | Daisy Chained DUT (1,024 BGA 24DUTs) | Each BGA Via<br>(Total Count=24,576Ea)            |

| 0.5mm             | Max. | 6.0Ω                                 | 6.65mΩ                                            |

| (12DUTs)          | Min. | 5.64Ω                                | 4.64mΩ                                            |

| 0.4mm<br>(12DUTs) | Max. | 7.63Ω                                | 7.05mΩ                                            |

|                   | Min. | 7.25Ω                                | 4.81mΩ                                            |

#### Measured by DVM, Microcraft EMX6151

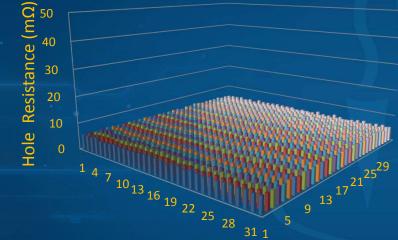

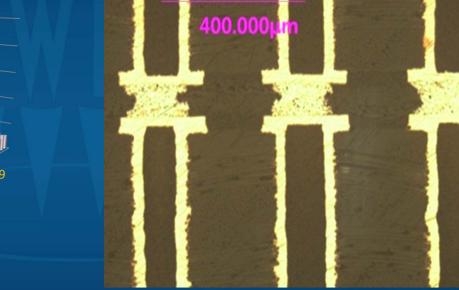

## **Electrical Conductivity**

• Via Holes Resistance of 1 DUT • Cross Section of Test Coupon

- BGA Pitch : 0.4mm

- 1,024 TABP Vias in 1DUT

- Max Via Hole resistance : 7.05mΩ

- Laser Drill Diameter : 150µm

- Prepreg Thickness : 110µm

#### <Stable Sintered Alloy Structure>

L57.785µr

June 8-11, 2014

## **Thermal Reliability**

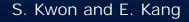

#### • Cross Section Analysis after Solder Pot Floating Test

- Thermal Impact Condition : 3 Times, 288°C Solder Pot Floating 10sec

- BGA Count per Each DUT : 100, 600, 1024 & 1600 Ea

- Each Via in Same DUT connected by Daisy Chain

- All BGA Interconnection Test was passed.

- TABP can withstand Thermal Impact of Solder Floating Test.

## **Thermal Reliability**

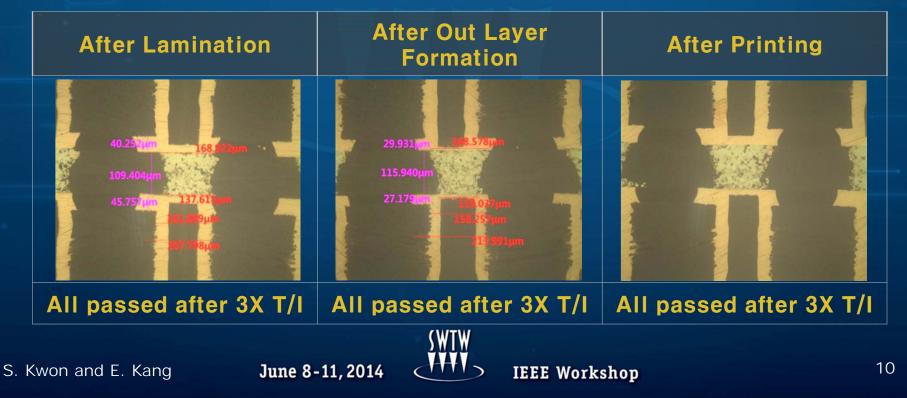

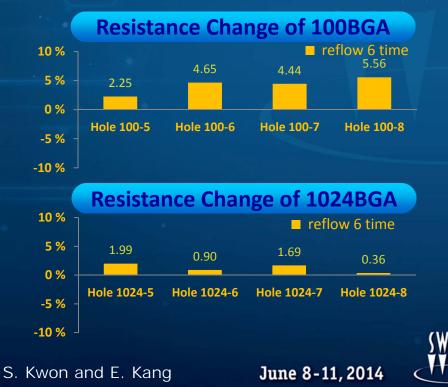

#### • Resistance Changes after Solder Reflow Exposures

- Reflow Condition : 6 Times Reflow @260°C

- BGA Count per Each DUT : 100, 600, 1024 & 1600 Ea

- Each Via in Same DUT connected by Daisy Chain

- All BGA Interconnection Test was passed.

- IPC Standards for DC Resistance Change after Reflow : Max 10%

## **Thermal Reliability**

#### • Cross Section Analysis after 6x Reflow Exposure

- Board Profile : 296FBGA, 0.35mm Pitch, 4mmT, 3 TABP, 0.15mm Laser Drill

- Applied Thermal Impact Condition : 6 Times Reflow @260°C

- TABP's Structural Stability can withstand 6 times of Reflow Condition.

# < Cross Section after Thermal Impact>

**Stable Paste Structure & Bonding Condition**

June 8-11, 2014

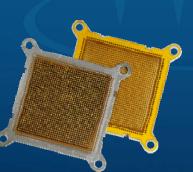

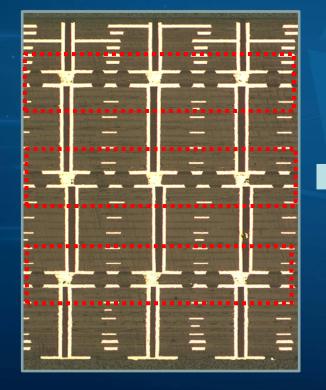

## **TABP Application Examples**

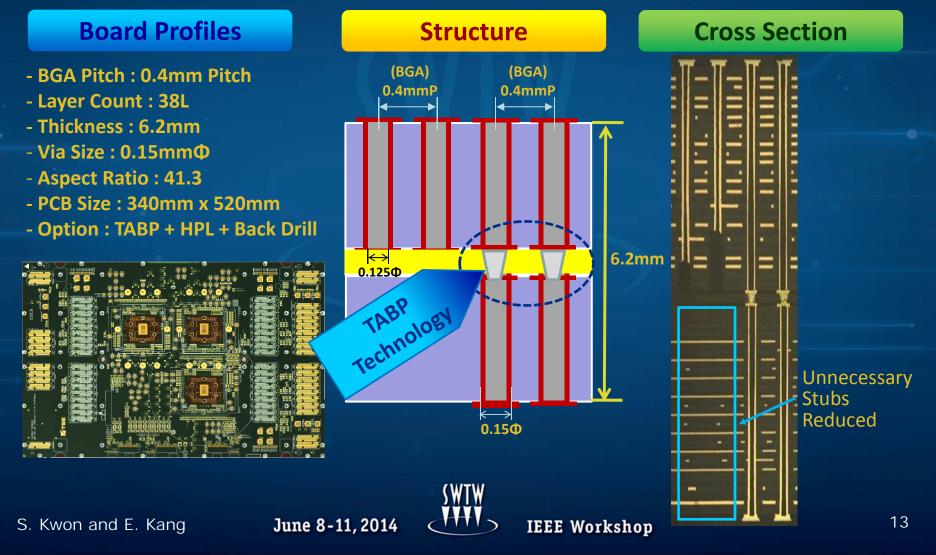

#### • Load Board – 0.4mm Pitch, Aspect Ratio 41.3

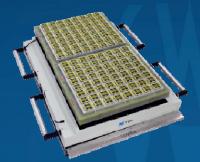

## **TABP Application Examples**

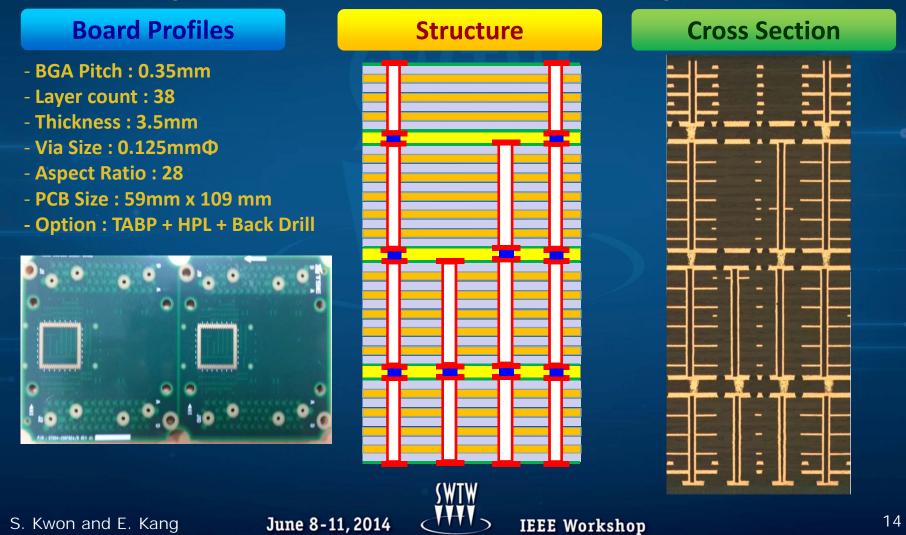

#### • Memory Test Board – 0.35mm Pitch, Aspect Ratio 28

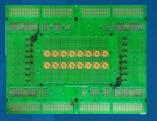

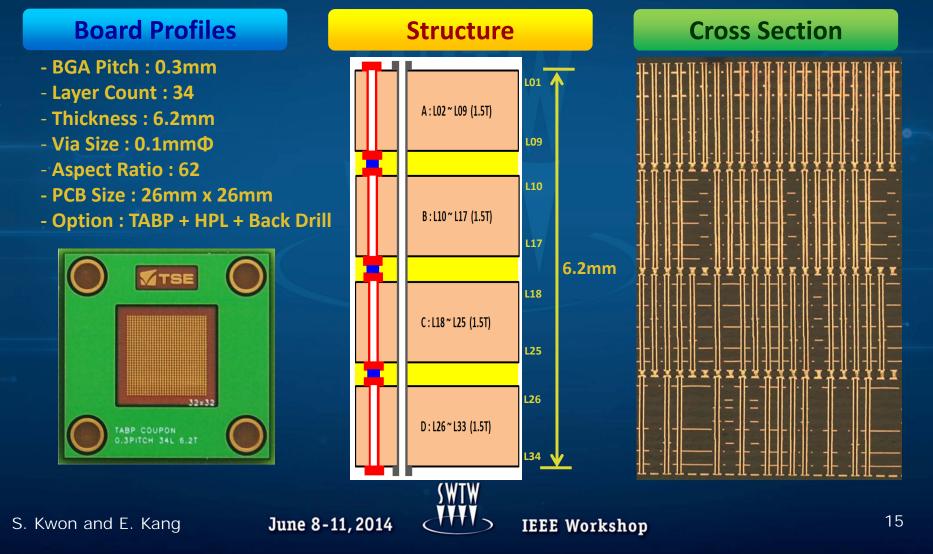

#### **TABP Application Examples**

#### • Pretest Coupon - 0.3mm Pitch, Aspect Ratio 62

## **Challenges for Probe Card PCB**

- High Layer Count / High Aspect Ratio

- SI Performance for High Speed Application

- Design/Fabricate PCB at Competitive Conditions

#### TABP is a Solution for Advanced Probe Card PCB.

- by Eliminating of Thick Board Drilling

- by Eliminating of High Aspect Ratio Via Plating

- by Reducing Drilling Complexity & Improving Yield

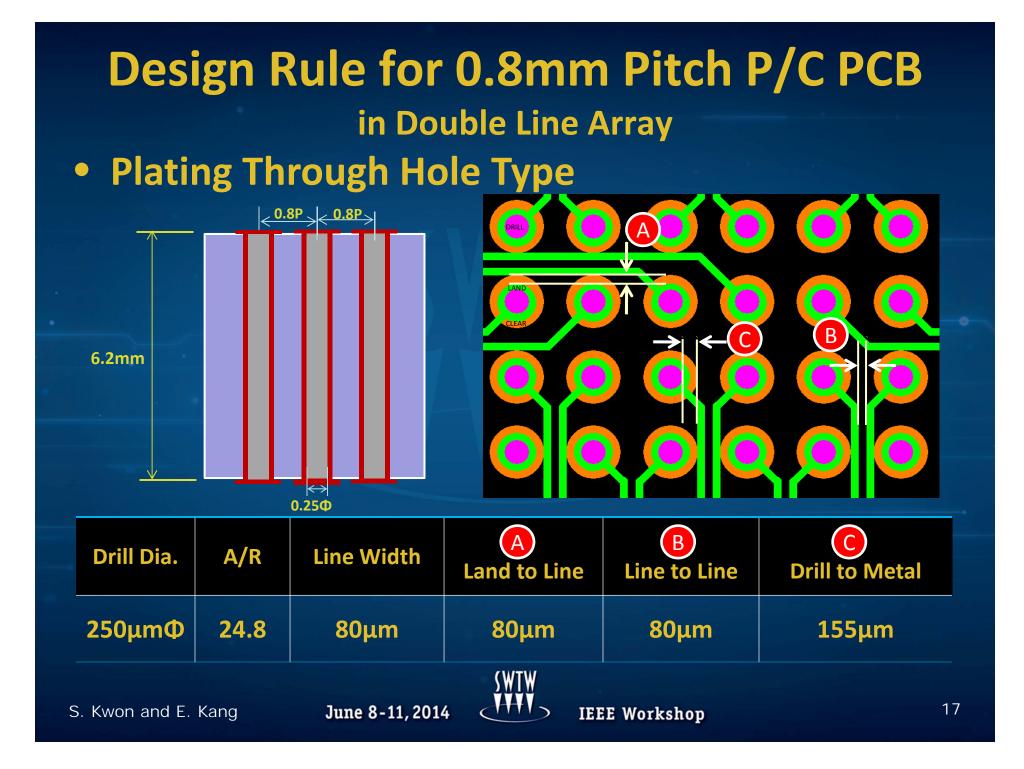

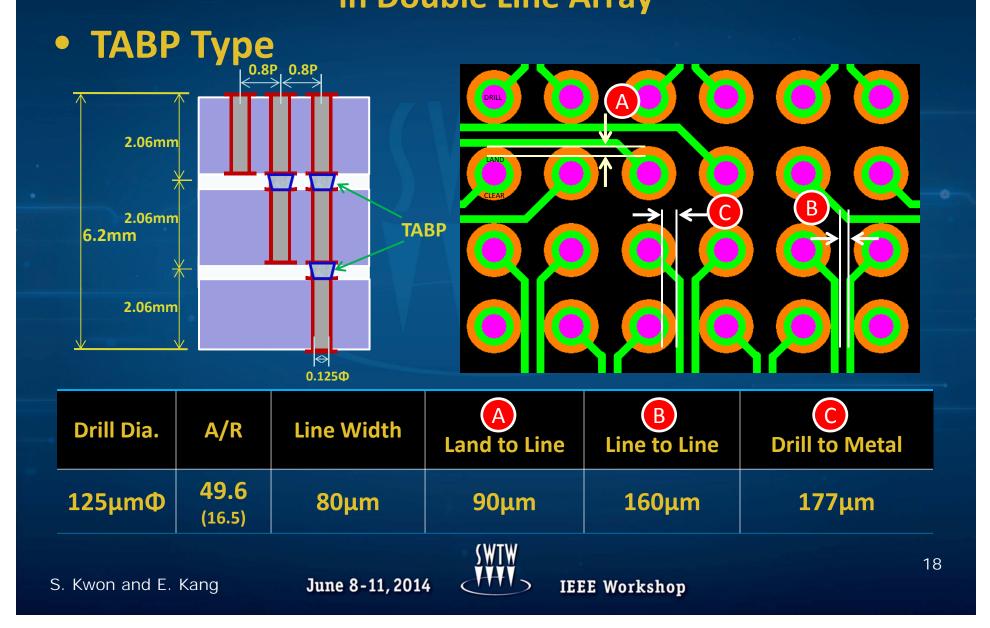

#### Design Rule for 0.8mm Pitch P/C PCB in Double Line Array

#### Conclusions

- Conductive Paste Based Core to Core Interconnection Technology at PCB was realized. Especially excellent core to core conductivity and thermal reliability were proved. Therefore, we hope the TABP technology would pave the way for fine pitch and high aspect ratio PCB fabrication.

- 0.4mm Pitch, Aspect Ratio 41.3 Load Board & 0.3mm Pitch, Aspect Ratio 62 Board were possible to fabricated with TABP Technology.

- Test boards for wafer test also need TABP technology to respond for the requirement of multi sites, fine pitch and high frequency performance.

S. Kwon and E. Kang

June 8-11, 2014

## Thank you very much.

## **Questions?**

June 8-11, 2014