# SW Test Workshop

Semiconductor Wafer Test Workshop June 7 - 10, 2015 | San Diego, California

# Are You Really Going to Package That?

Ira Feldman Debbora Ahlgren Feldman Engineering Corp.

# Outline

- Situation

- Cost of Test

- New Paradigm

- Probe Card Cost Drivers

- Computational Evolution

- New Approaches

- Conclusion

Feldman & Ahlgren

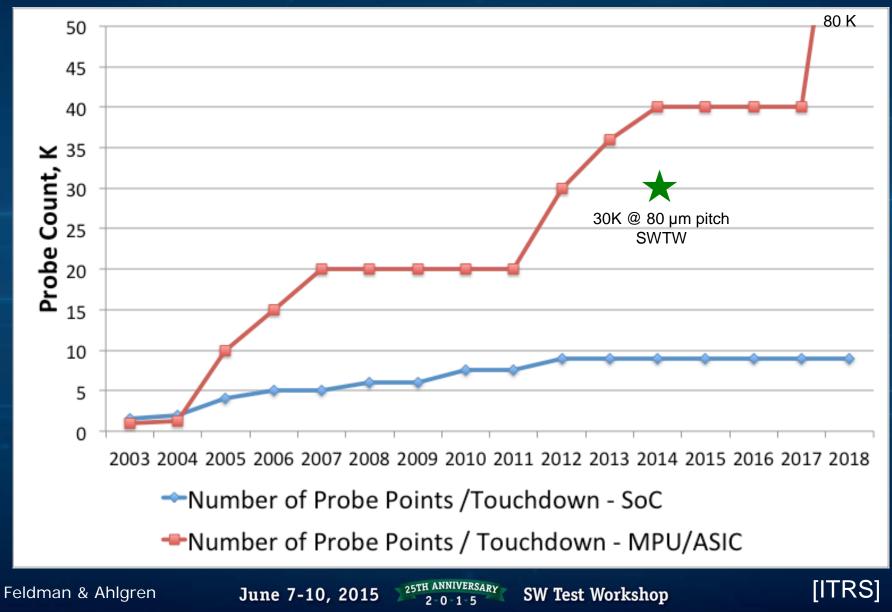

## **Increasing Wafer Probe Count**

# Wafer Level Chip Scale Packaging

#### WL-CSP(Wafer Level CSP) Process

**RDL** Forming/ Encapsulation Wafer Process Dicing Wafer Level Packaging Fujitsu Bad die End up packaged here

Feldman & Ahlgren

June 7-10, 2015 🔰

25TH ANNIVERSARY 2 0 1 5

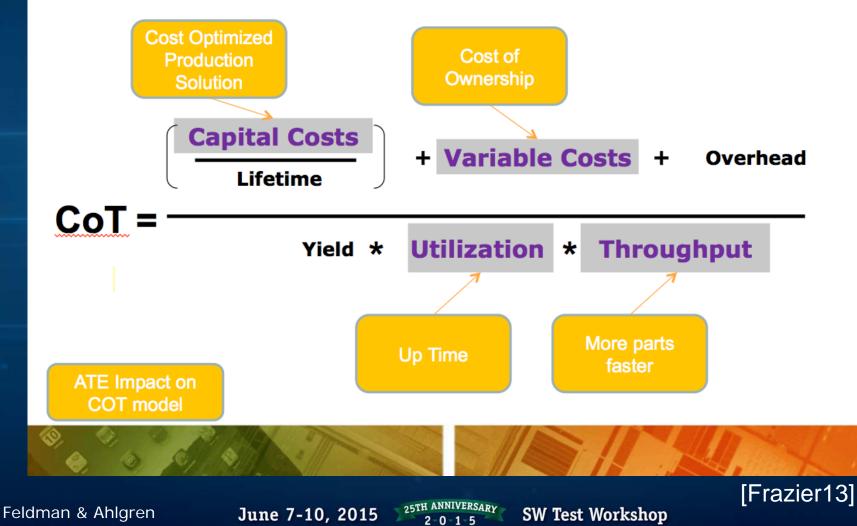

#### Semi Market Effects on ATE

Cost Pressures on test continue

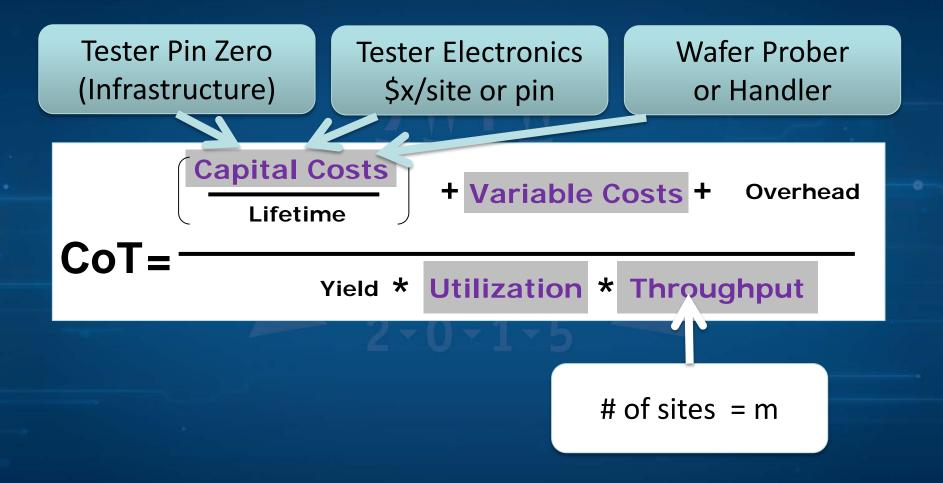

## **Capital Costs**

Feldman & Ahlgren

June 7-10, 2015

### **Usual Math...**

|                                       | # of sit             | es = m   |

|---------------------------------------|----------------------|----------|

|                                       | Total                | Per Site |

| Tester Pin Zero<br>(Infrastructure)   | TPZ                  | TPZ/m    |

| Tester Electronics<br>\$x/site or pin | \$x/site * m = x * m | X        |

| Wafer Prober<br>or Handler            | WP                   | WP/m     |

|                                       |                      |          |

[Rivoir03]

Feldman & Ahlgren

June 7-10, 2015

25TH ANNIVERSARY 2 0 1 5

# **Example Calculation**

|                                       | # of sites = m |            |

|---------------------------------------|----------------|------------|

|                                       | m = 1          | m = 8      |

| Tester Pin Zero<br>(Infrastructure)   | \$250 K        | \$31.25 K  |

| Tester Electronics<br>\$x/site or pin | \$50 K         | \$50 K     |

| Wafer Prober<br>or Handler            | \$300 K        | \$37.5 K   |

| COST PER SITE                         | \$600 K        | \$118.75 K |

Feldman & Ahlgren

June 7-10, 2015 25TH ANNIVERSARY

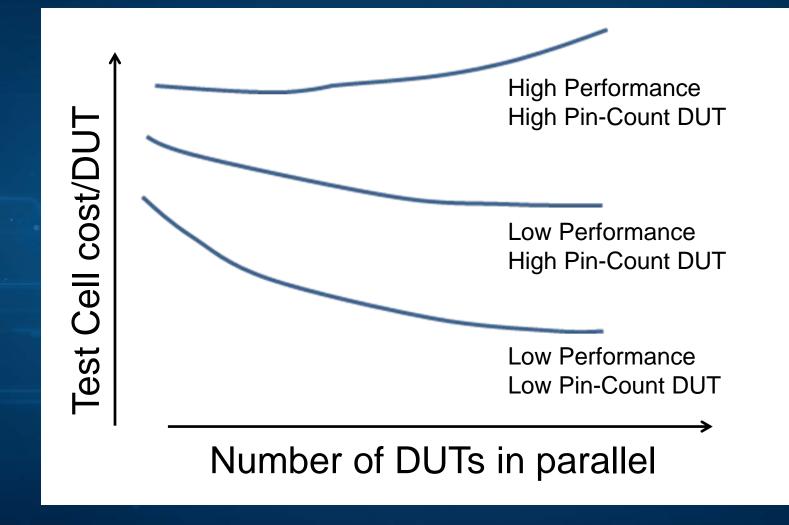

### Performance vs. Cost

Feldman & Ahlgren

June 7-10, 2015

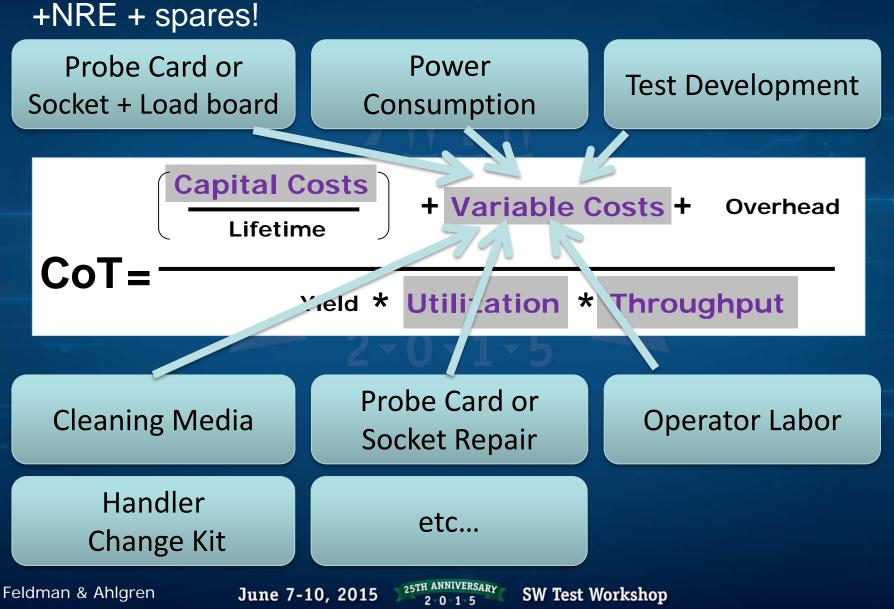

### **Variable Costs**

### **New Paradigm**

# Variable Costs >> Capital Costs over life of test cell

Example: single Probe Card > Tester Cost (often so expensive that they are being capitalized!)

June 7-10, 2015 25TH ANNIVERSARY SW Test Workshop

Feldman & Ahlgren

# **Typical Probe Card Cost Drivers**

#### • Linear

Number of probes (for singulated technology)

#### Slightly more than linear

Number of holes to be drilled (for singulated technology)

Low force probe technology

[Feldman11]

# **Typical Probe Card Cost Drivers**

#### • Non-linear (some area & some exponential)

- Mechanical elements

- Increased force

- Larger area for co-efficient of thermal expansion (CTE) match

- Active area

- Larger space transformer (more layers?) & interposer

- Larger PCB (plating variance across area, tight pitch issues)

- Probe head (photolithographic processes w/defect density)

- Printed Circuit Board (PCB)

- Size & layer count

- Advanced materials

- High frequency / high bandwidth challenges

Feldman & Ahlgren

June 7-10, 2015

SW Test Workshop

[Feldman11]

# **Operational Issues Too**

#### Supply related

- Cycle time to build probe card

- Higher cost of "spares"

- Higher repair cost if head cannot be repaired

#### Operational

Decreased step pattern efficiency

[Wegleitner13]

[Leong14]

- All die on touchdown are limited by longest test time

- Adaptive test limitations

- Costly for low yielding wafers

- Retest is costly

#### Longer metrology times

Feldman & Ahlgren

June 7-10, 2015 2

### **Other Issues...**

- Site to site correlation not copy exact

- Slower to reach "economies of scale"

- fewer copies ordered on multisite

- Increased investment for slight increases in capacity

- Will probe cards scale to 450 mm?

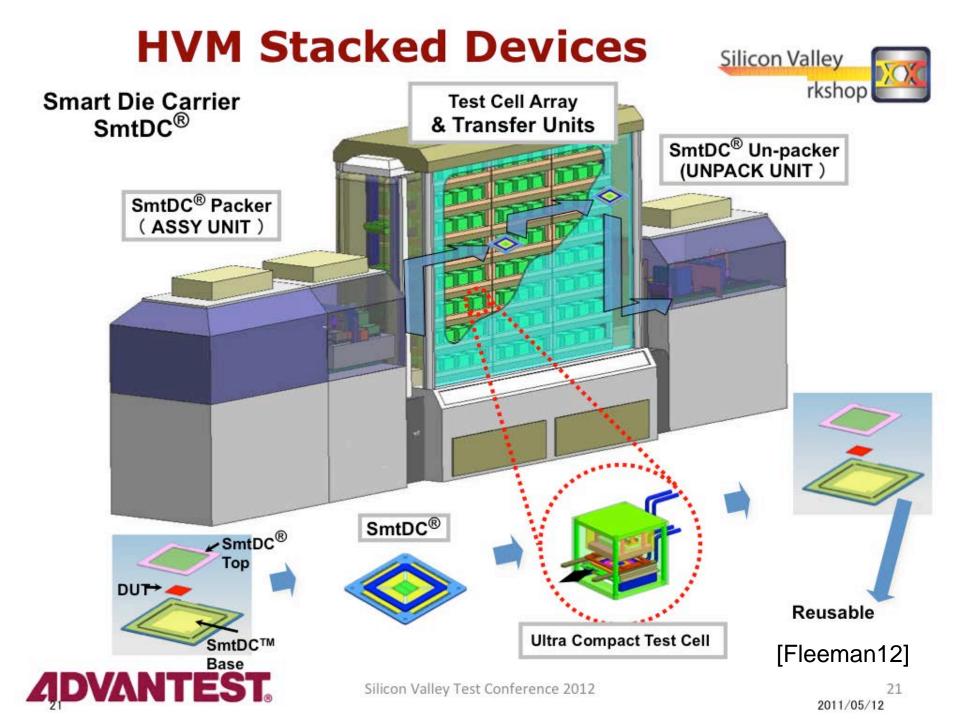

Testing of 2.5/3D die stacks

[Feldman12]

[Feldman13]

Feldman & Ahlgren

## **Computational Evolution**

datacenterknowledge.com

#### Time & Increasing Performance

IBM System/360 - computerhistory.org

ANNIVERSADV

IBM 5150- Wikimedia / Zarek

June 7-10, 2015

Facebook.com/PhoneDesigner

SW Test Workshop

Feldman & Ahlgren

# **Simplified Die Handling?**

pazumpa.com

20thcenturytoycollector.com

Feldman & Ahlgren

### **'PEZ'** Nano-Tester

"Contactor" / Probe Head

Load Board 6" (150 mm) sq. ? Handling & Active Thermal

Electronics & Power Supplies

Feldman & Ahlgren

June 7-10, 2015 2 0 1 5

Ρ

A S

Ν

Ρ

F

A

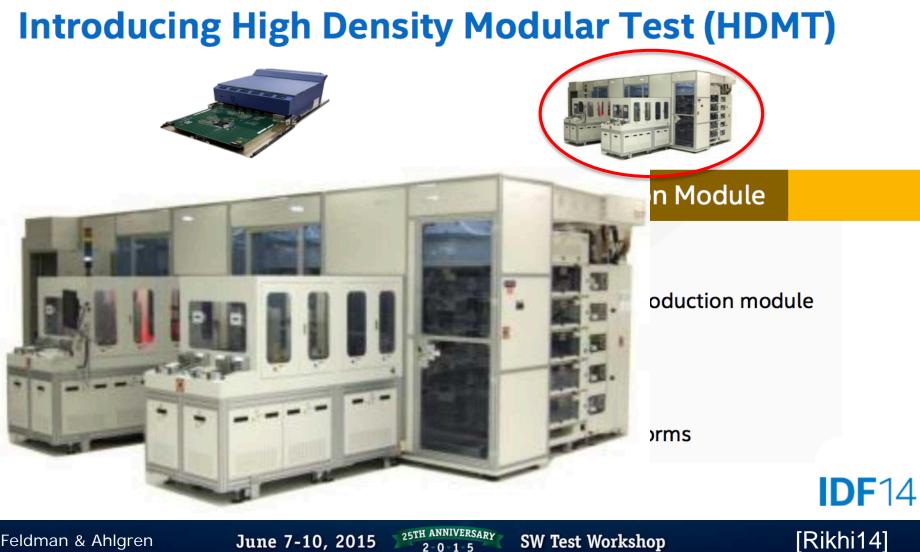

# **Intel HDMT**

#### Introducing High Density Modular Test (HDMT)

#### Engineering Module

#### **Production Module**

**IDF**14

[Rikhi14]

- Common Architecture

- Fast TTM Engineering Module

- >30 sites with parallel, asynchronous operation in production module

- Flexible Architecture

- Enables standard instrumentation integration (PXI)

- Low Cost

- > 2X Cost improvement over conventional test platforms

39

June 7-10, 2015 2 0 1 5

### Intel HDMT

Feldman & Ahlgren

June 7-10, 2015

# Conclusions

Previous "answers" need to be re-evaluated as boundary conditions change

- New product requirements and packaging technology will force changes

- Solutions need to be optimized at test cell, factory, and supply chain level

- Increased ability to build test solutions that fit product mix vs.

living with legacy solutions

- Careful choices need to be made about "plug and play" alternatives

# • Capital and Operating budgets need to balanced and rationalized

Feldman & Ahlgren

### Acknowledgements

- Dave Armstrong Advantest

- Rey Rincon Freescale

- Jochen Rivoir Advantest

- Jeff Roehr Texas Instruments

Plus "Anonymous" at IDM and Fabless...

Feldman & Ahlgren

June 7-10, 2015 2-0-1-5 SW Test Workshop

# Thank You! Ira Feldman ira @ feldmanengineering.com

Please visit Ira's blog www.hightechbizdev.com

June 7-10, 2015 2-0-1-5 SW Test Workshop

### References

Feldman11 – Ira Feldman, Feldman Engineering Corp., "Probe Card Cost Drivers from Architecture to Zero Defects", IEEE Semiconductor Wafer Test Workshop (SWTW) 2011

Feldman12 - Ira Feldman, Feldman Engineering Corp., "The Road to 450 mm Semiconductor Wafers", IEEE Semiconductor Wafer Test Workshop (SWTW) 2012

Feldman13 - Ira Feldman, Feldman Engineering Corp., "Ideal 3D Stacked Die Test", IEEE Semiconductor Wafer Test Workshop (SWTW) 2013

Fleeman12 - Gary Fleeman, Advantest, "Getting to Known Good Stack", Silicon Valley Test Workshop, October 2012

Fraizer13 – Mike Frazier, LTX-Credence, "What will Drive the ATE Market beyond 2013?", SEMICON Singapore 2013

Feldman & Ahlgren

### **References - continued**

ITRS – International Technology Roadmap for Semiconductors, www.itrs.net

Leong14 – Alexander Witting (GLOBALFOUNDRIES), Amy Leong, et. al (FormFactor), "Key Considerations to Probe Cu Pillars in High Volume Production", IEEE Semiconductor Wafer Test Workshop (SWTW) 2014

Rikhi14 – Sunit Rikhi, Intel, "Leading at the edge of Moore's Law with Intel Custom Foundry", Intel Developer Forum (IDF) 2014

Rivoir03 – Jochen Rivoir, Agilent Technologies, "Lowering Cost of Test: Parallel Test or Low-Cost ATE?", IEEE Asian Test Symposium 2003

Wegleitner13 - Al Wegleitner (Texas Instruments), Tommie Berry (FormFactor), "When Brick Wall is not the best, PART II (A Touch Down Optimization Study)", IEEE Semiconductor Wafer Test Workshop (SWTW) 2013

Feldman & Ahlgren