## An Automated Bad Blocks Analysis System Development for NAND Flash

Sung-Kwan Jung, Min-Kyo Seo

skjsa.jung@samsung.com, mk27.seo@samsung.com

Samsung Electronics, Samsung Electronics

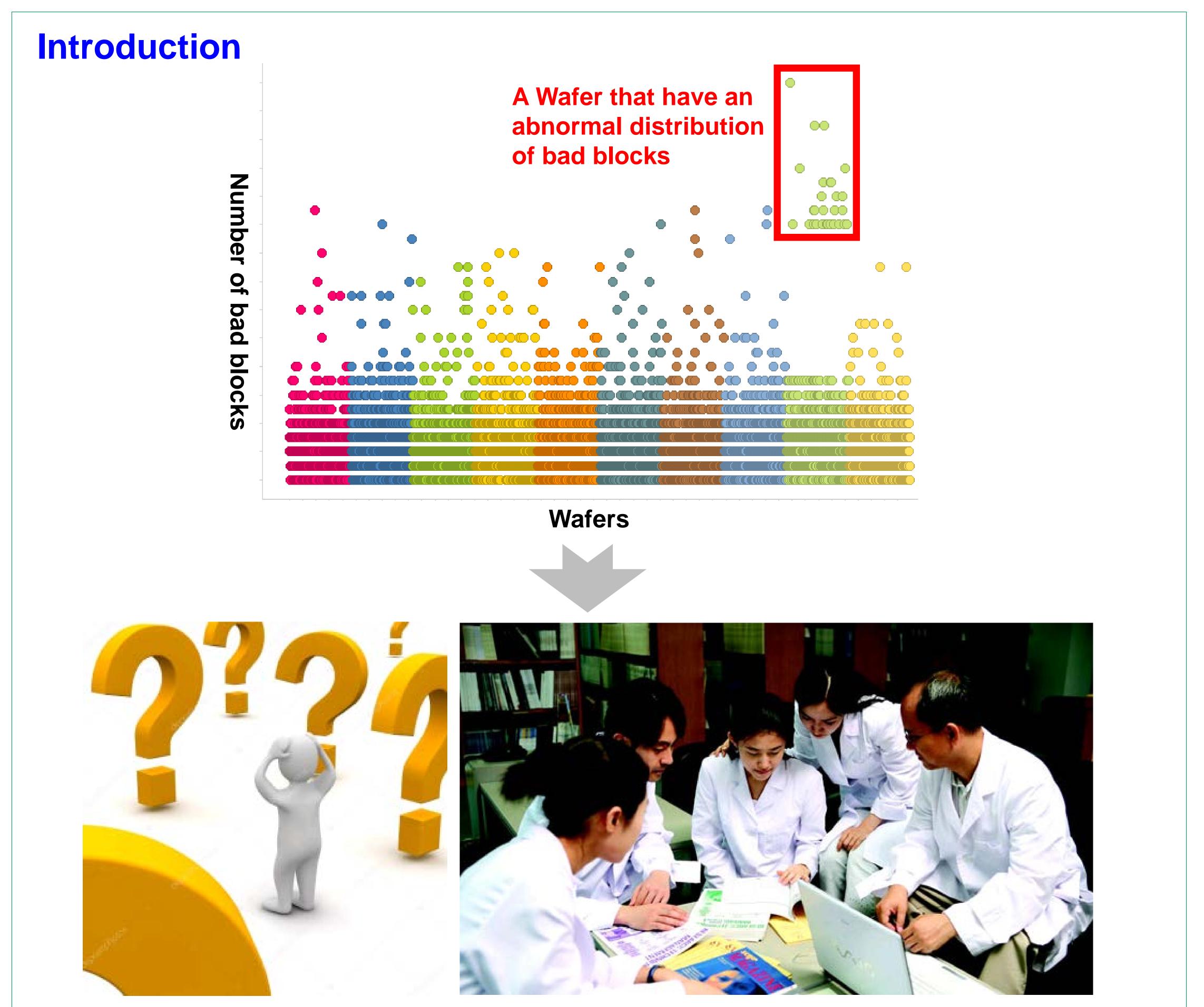

- NAND Flash : Some bad blocks.

- Bad Block

- One or More invalid bits : Reliability is not guaranteed

- One of the most important factors : Great infulence to the quality

- Wafer Probe Test

- Electrically checks : All individual chips on wafer

- Bad blocks per each chip

If we don't the additional failure analysis, we don't Know the failure type of bad blocks

SW Test Workshop 2017, June 4 to 7, 2017

## **Proposed Method**

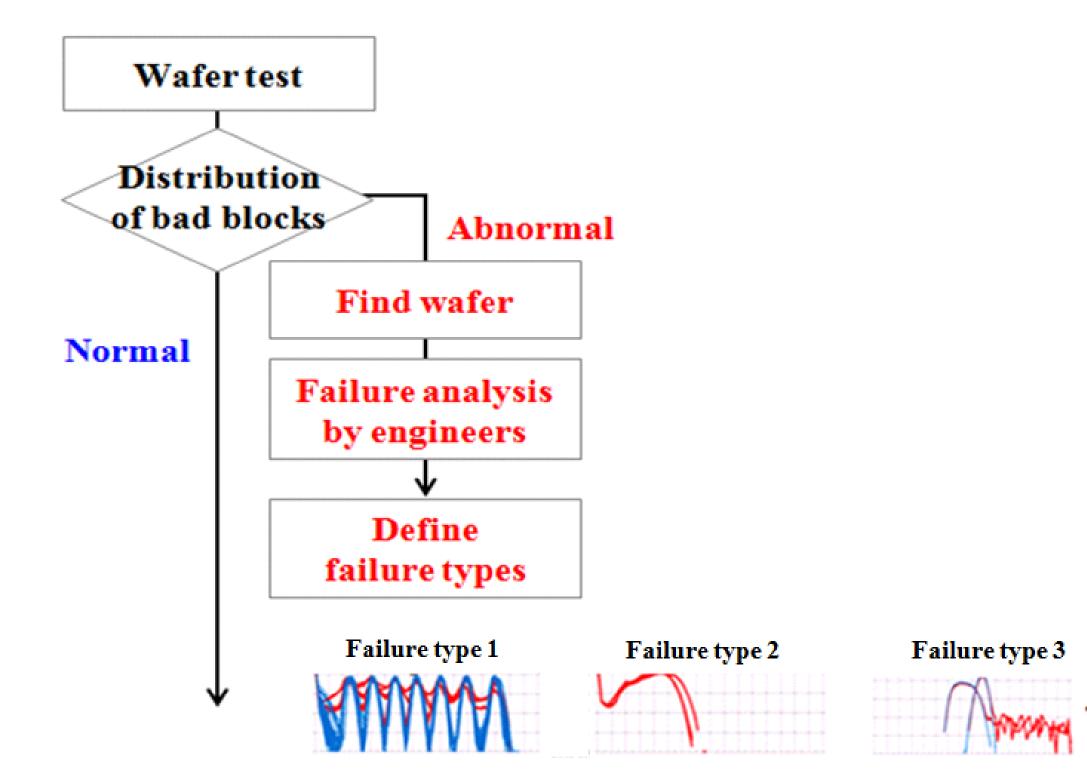

- Process of failure analysis

- Monitor the distribution of bad blocks

- Directly conduct failure analysis

- Define specific failure types of bad blocks

- Too much time and effort

Only a small number of bad blocks

Wafer probe test To Be The proposed system

- Develop an automated bad blocks analysis system

- First, get information of all bad blocks per each chip

- Second, set to internal memory of test equipment

- Third, conduct multiple test items

- Finally, define failure types of bad blocks by the logic

- Can know specific failure type of bad blocks without additional failure analysis

- Can efficiently monitor changes of failure types without extra time and effort

## **Results**

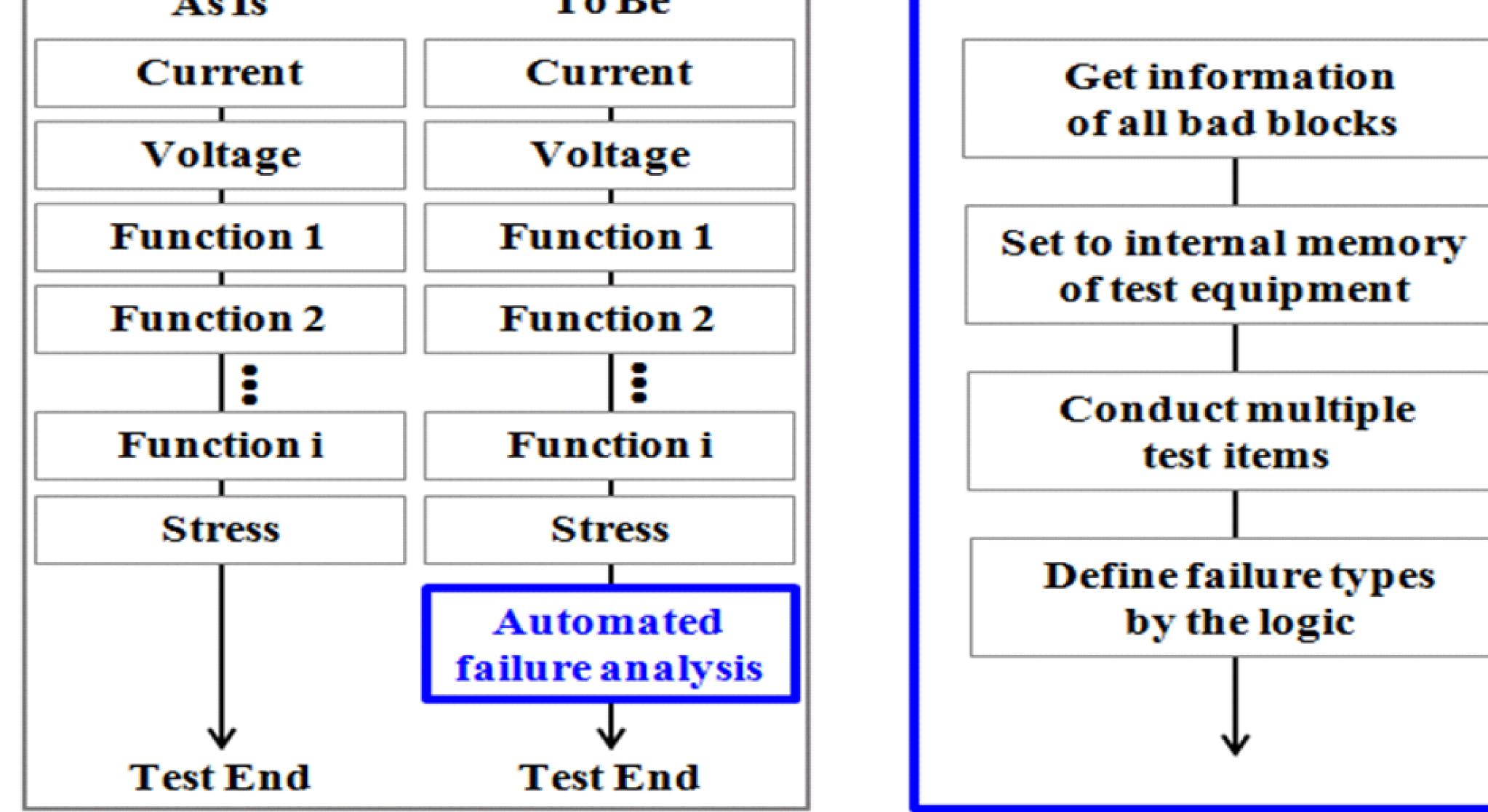

As Is

To Be

| Procedure of<br>failure analysis | Chip   | Bad blocks |  |

|----------------------------------|--------|------------|--|

| 1                                | Chip1  | Α          |  |

| 2                                | Chip1  | В          |  |

| 3                                | Chip1  | С          |  |

| 4                                | Chip2  | D          |  |

| 5                                | Chip2  | E          |  |

| 6                                | Chip3  | F          |  |

| 7                                | Chip3  | G          |  |

| •••                              |        |            |  |

| 49                               | Chip10 | AW         |  |

| 50                               | Chip10 | AX         |  |

| Procedure of<br>failure analysis | Chip | Bad blocks        |

|----------------------------------|------|-------------------|

| 1                                | All  | A, D, F, ••• , AW |

| 2                                | All  | B,E,G, ••• ,AX    |

| 3                                | All  | С                 |

Parallel failure analysis (Time : 0.6 hour)

**95% reduced** (9.8 hour  $\rightarrow$  0.6 hour)

Serial failure analysis (Time : 9.8 hour)

✓ Significantly reduce time of failure analysis :  $95\%(9.8Hr \rightarrow 0.6Hr)$

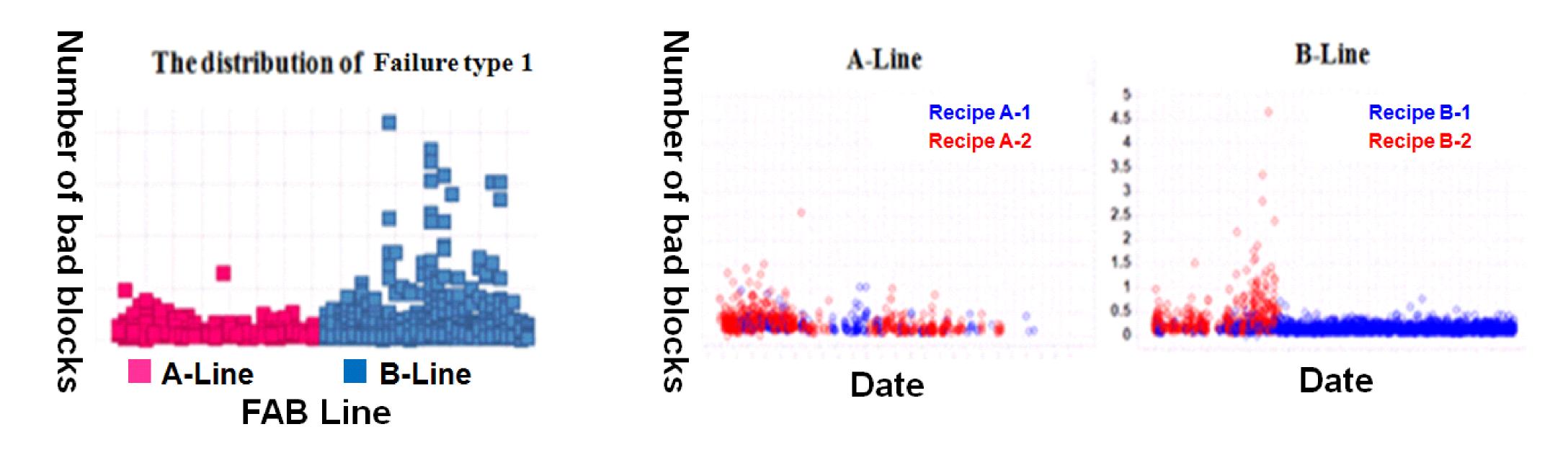

Compare distribution of failure type 1 :

B-Line is higher than A-Line(some recipes)

## Conclusion

- Requirements for quality about nand flash are recently growing

- Many companies study various methods to improve the quality

- So, we develop an automatic bad blocks analysis system

- System automatically analyze failure types of bad blocks in real time

- Can know specific failure type of bad blocks without additional failure analysis

- Can efficiently monitor changes of failure types without extra time and effort

SW Test Workshop 2017, June 4 to 7, 2017