SW Test Workshop Semiconductor Wafer Test Workshop

# Improved ON-resistance Measurement at Wafer Probe using a "DARUMA" stage

Masatomo TAKAHASHI ACCRETECH, Japan **Nobuyuki TOYODA** TESEC, Japan

June 4-7, 2017

### Background

- Trend of MOSFET

- Transition of low ON resistance Overview of DARUMA Chuck (Rds<sub>(on)</sub>) products

- Present situation

- Measurement by Standard stage

- Matter of concern

- Suspected root cause

- Solution

- DARUMA

- - Advantage of DARUMA Chuck etc.

- Verification

- Measurement by "DARUMA"

- Comparison with standard stage \_

- Simulation

- Conclusion •

# Trends of MOSFET

- Application and Criteria

- Load switch for DC Supply-unit in server

- Low On-Resistance (Rds<sub>(on)</sub>)

- Low Thermal Resistance (Rθjc, etc.)

- Wide Safe Operating Area (SOA)

- Switching device for switched-mode power supply (SMPS)

- Low Rds<sub>(on)</sub>

- Low Gate Charge (Qg)

- Motor control

- Low Reverse Recovery Time (trr)

# Trends of MOSFET

- Purpose vs Representative Characteristics

- Energy savings ⇒ Low On-Resistance

(Low loss)

- Fast switching ⇒ Low gate Capacitance (High speed)

- High reliability ⇒ Wide Safe Operating Area,

(High performance) High breakdown resistance

- Miniaturization ⇒ Enhancement of Heat-resisting property (Small packaging)

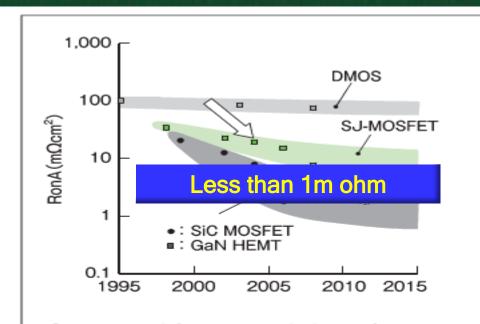

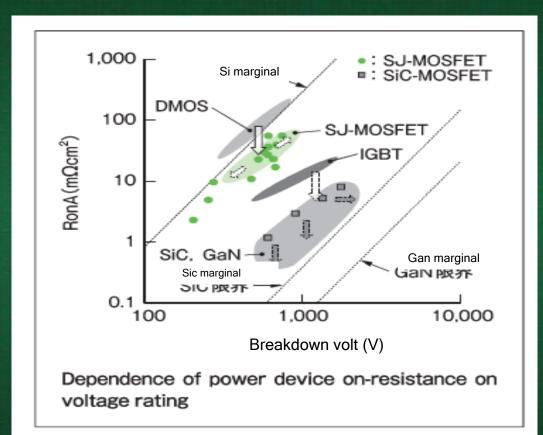

# **Transition of low ON resistor products**

Current and future trends in performance improvement of 600 V metal-oxide semiconductor field-effect transistors (MOSFETs)

Graphs from *Toshiba Review* Vol.65No.1 (2010)

Takahashi, Toyoda

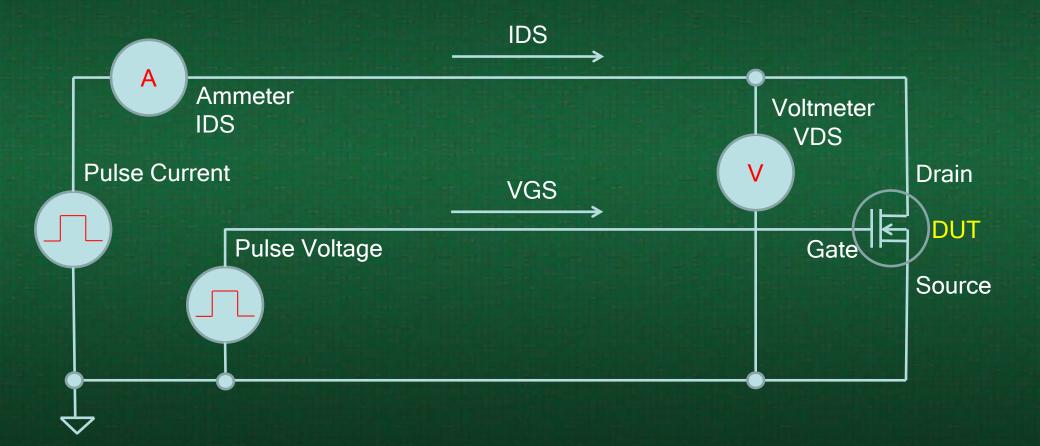

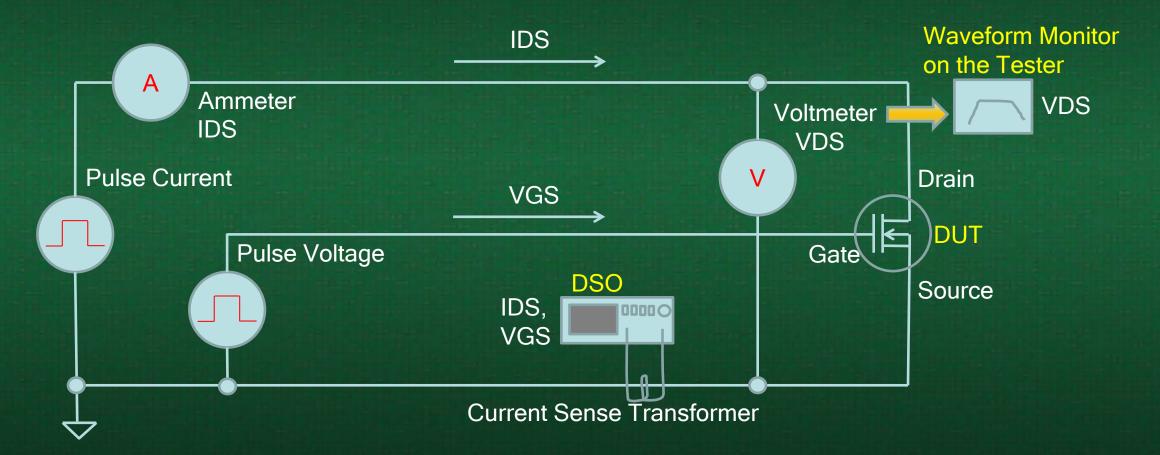

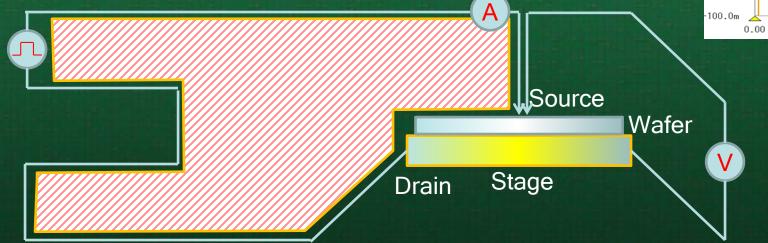

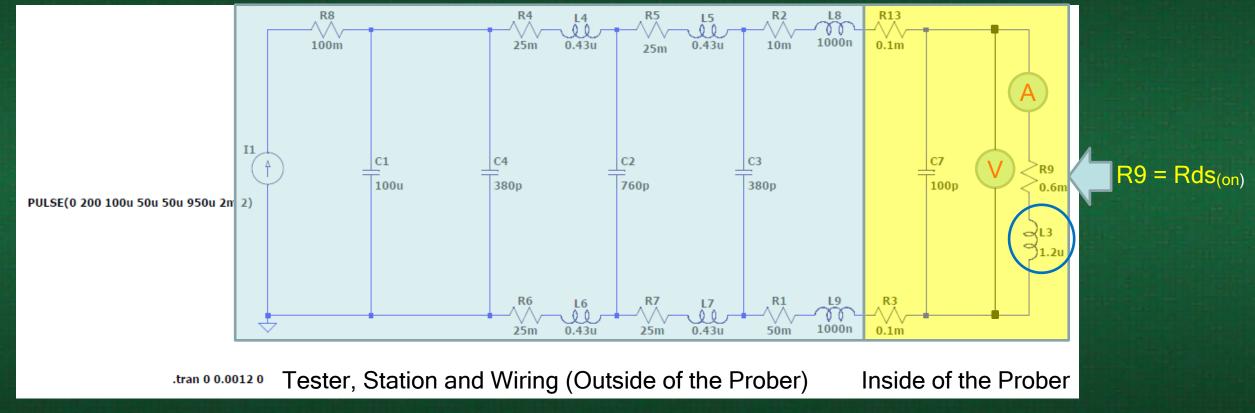

### Simplified Schematics for Rds<sub>(on)</sub> testing at wafer probe

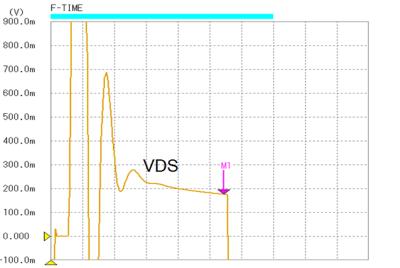

### Simplified Schematics for Rds<sub>(on)</sub> to check waveform

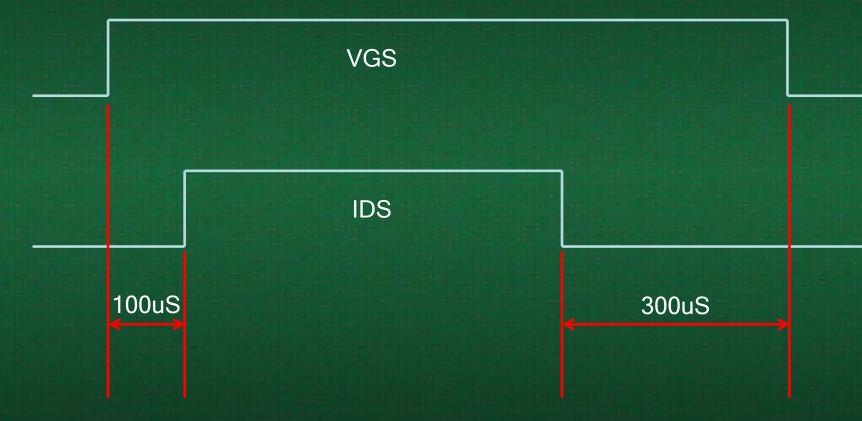

### Timing chart

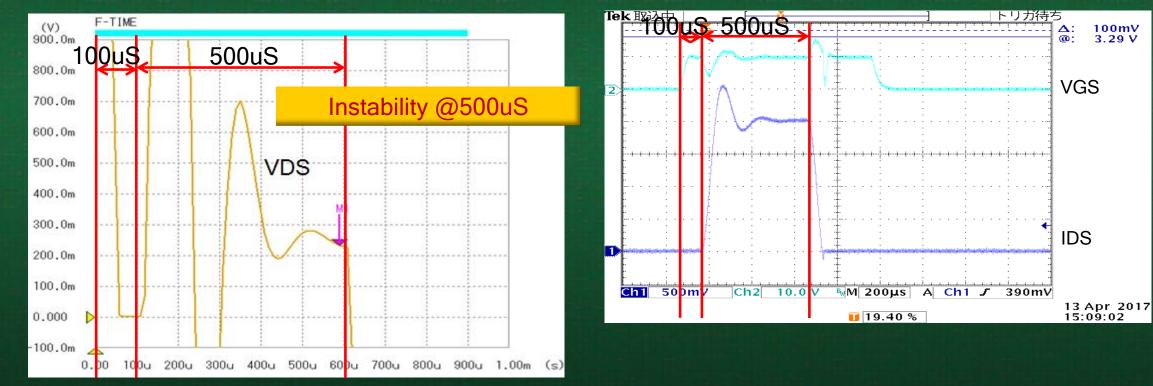

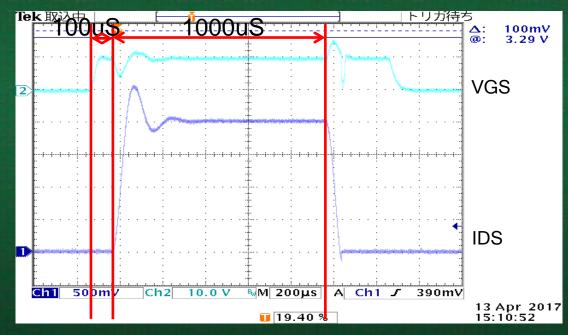

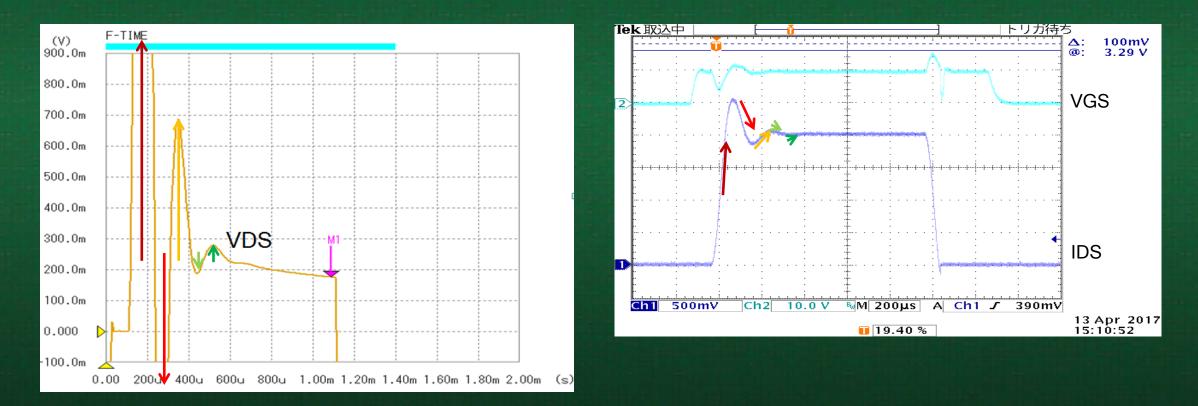

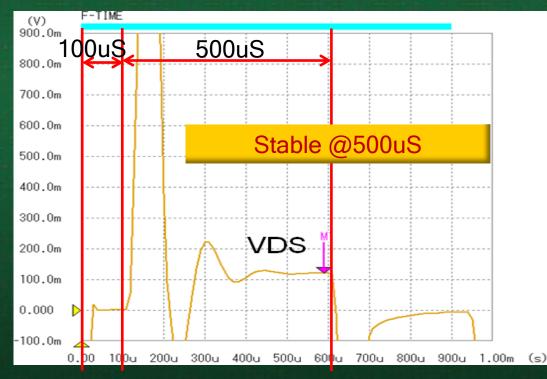

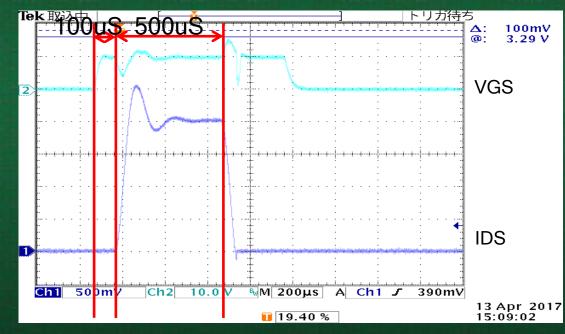

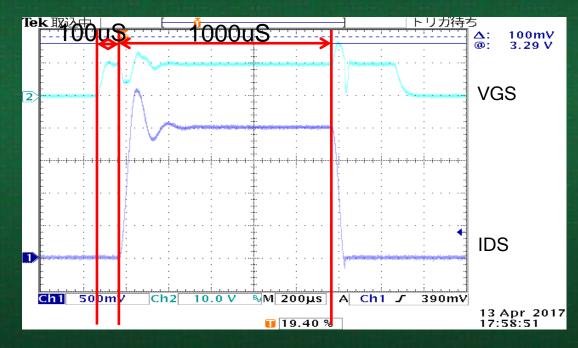

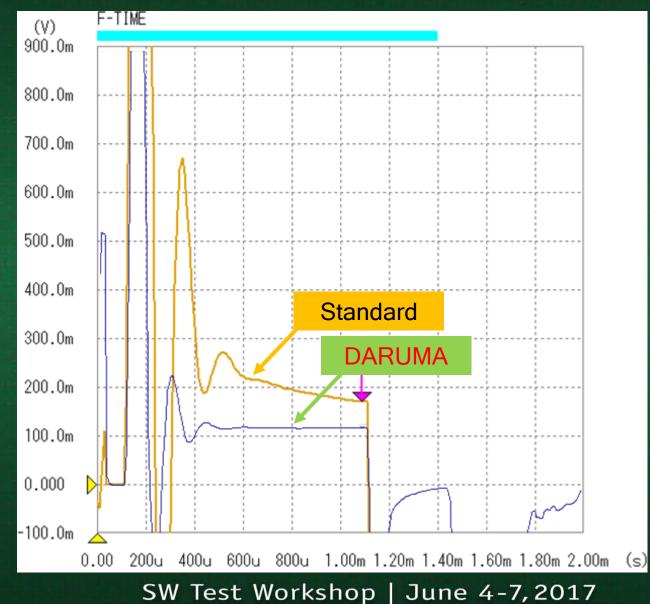

### [Measurement result-1] Test condition : Rds<sub>(on)</sub>, IDS=200A, Test time=500uS Stage type : Standard

100mV

3.29 V

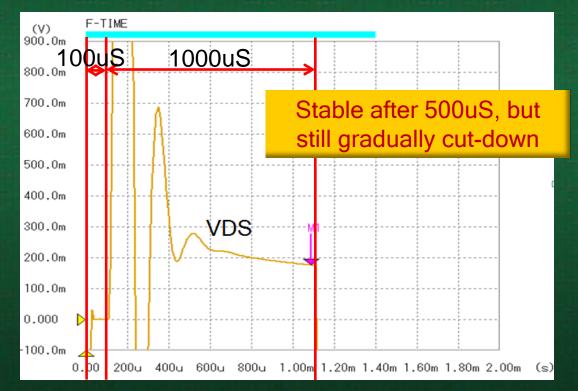

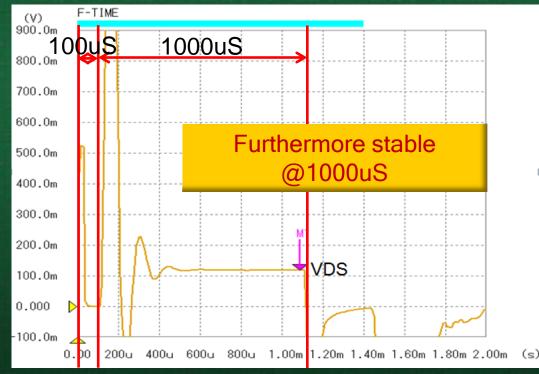

### [Measurement result-2] Test condition : Rds<sub>(on)</sub>, IDS=200A, Test time=1000uS Stage type : Standard

# Matters of concern

Measurement waveform is unstable (Need longer test time to be stabilize)

**Increases Forcing time of test current**

Increases temperature of the tested device

Decreases the test accuracy and production quality

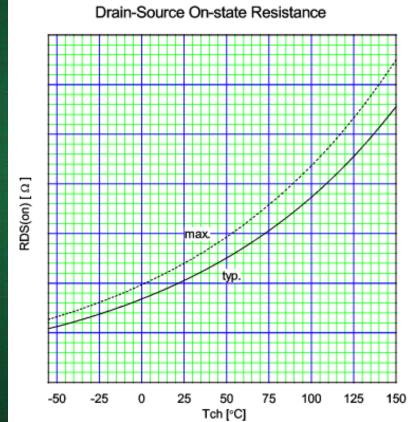

# Matters of concern ON resistance vs Channel temperature

#### Ideal test environment (Temperature)

- Exists when the channel(Junction) and case (package) temp are the same.

- Requires "Very short pulse" during on-resistance test to achieve temperature parity between Junction and Case

- Characteristic of MOSFETs, the on-resistance will rise as the device temp is increased in an attempt to protect the device itself (as the resistance increases, the current decreases)

- Therefore, when testing Rds<sub>(on)</sub>, controlling the temperature rise is critical to measurement stability.

- To control the temp during test,

"minimize the test time"

From Fuji Electric AN-079 Rev. 1.1

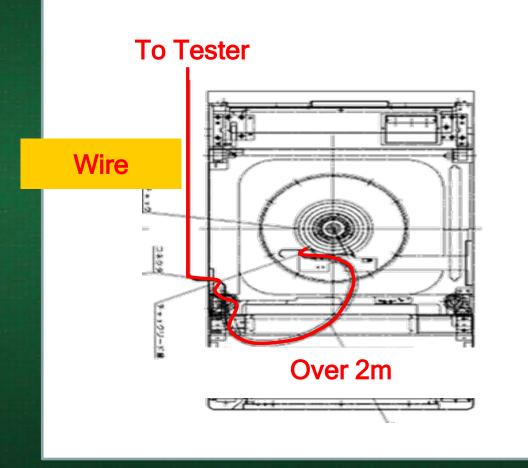

- Ls (Stray Inductance)

- Self inductance of wire loop (round trip)

Diameter of the wire to be '2a',

When the current is uniformly distributed in the electric wire,

and the conductor is nonmagnetic.

$L = 4 * \log(d/a) * 10^{-7} [H/m]$

- Ls (Stray Inductance)

- Mutual inductance between parallel wires

Pair of parallel wires, When I >> d , and in the air atmosphere.  $M = 2 * I * (log(2 * I / d) - 1) * 10^{-7} [H]$

Takahashi, Toyoda

SW Test Workshop | June 4-7,2017

d

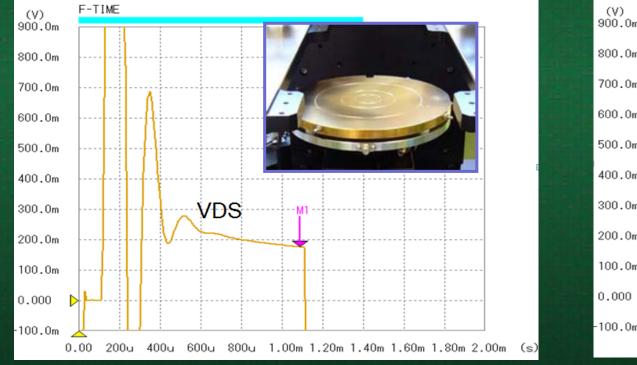

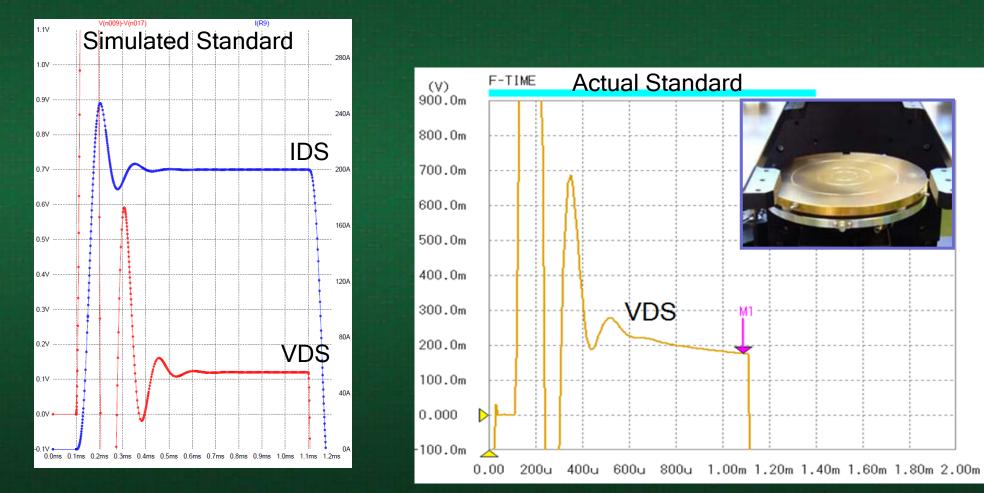

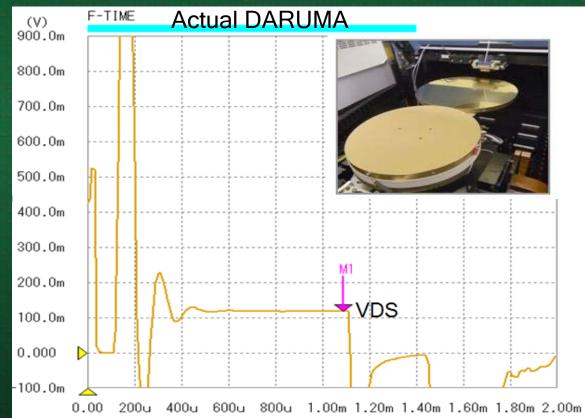

- VDS waveform is NOT stable.

Influence of the Stray Inductance (Ls) of the wiring between DUT and source & measurement circuits.

- Ls increases as the wire loop increases.

800u

1.00m 1.20m 1.40m 1.60m

200u

# The cause of the VDS "Spiking" is in Ls. ΔV=Ls(di/dt)

# **"DARUMA"**

- The Daruma doll, is a hollow, round, Japanese traditional doll modeled after Bodhidharma (Dharma), the founder of the Zen sect of Buddhism. Daruma has a design that is rich in symbolism and is regarded more as a talisman of good luck to the Japanese.

- When purchased, the eyes are white so a person can decide on a goal or wish and paint one eye in. Once the goal is achieved, the second eye is filled in.

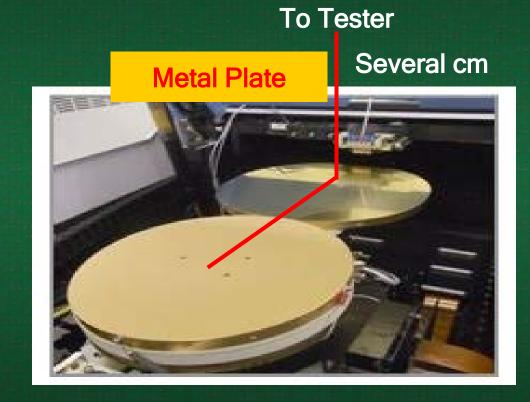

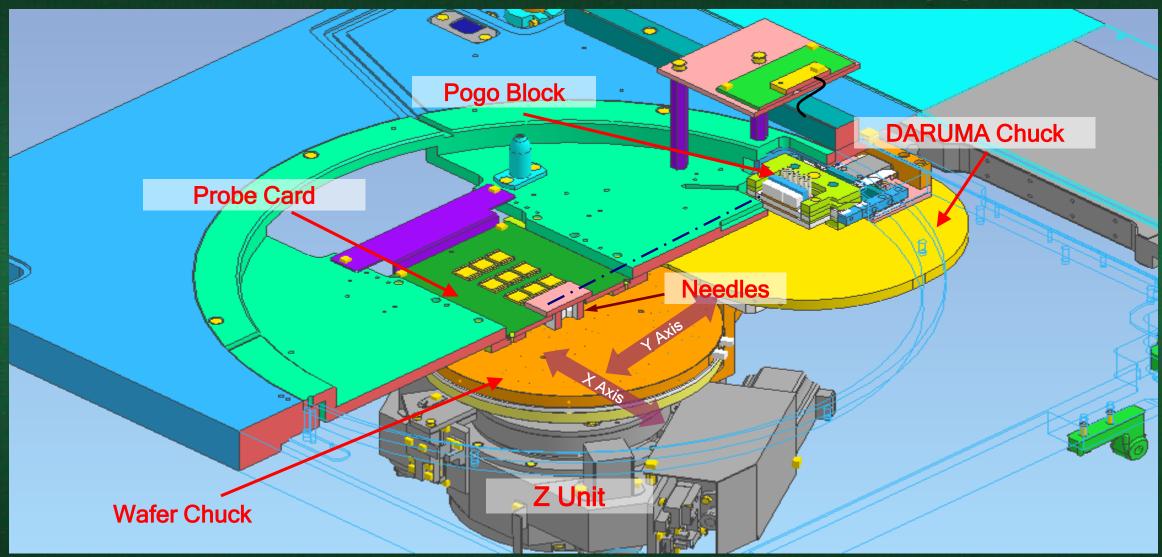

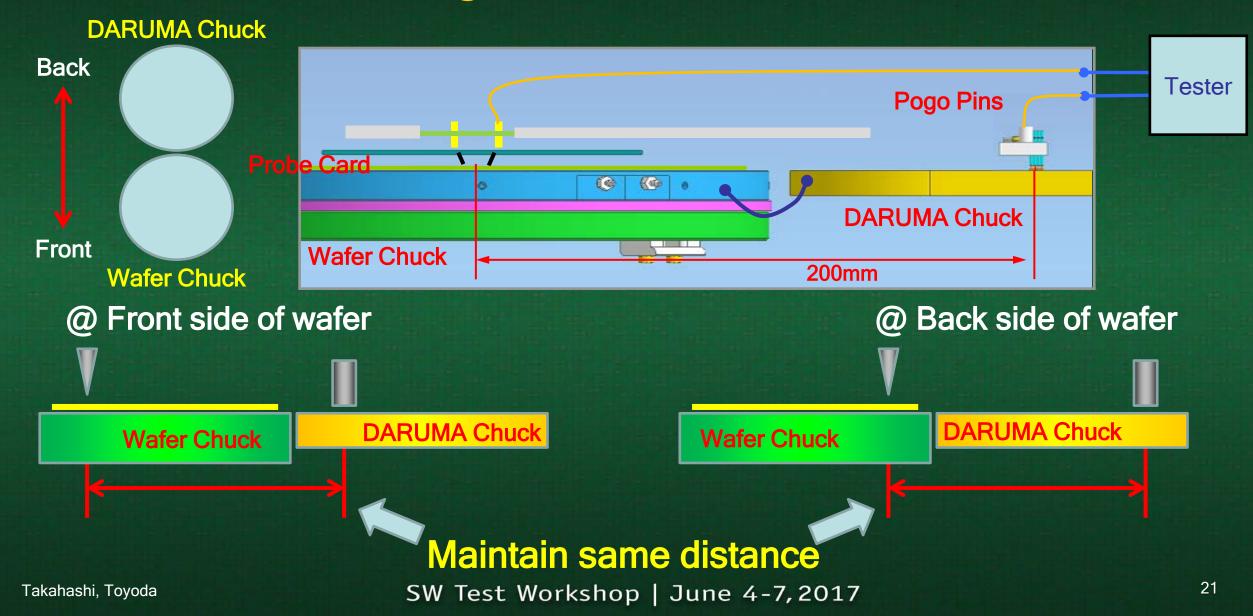

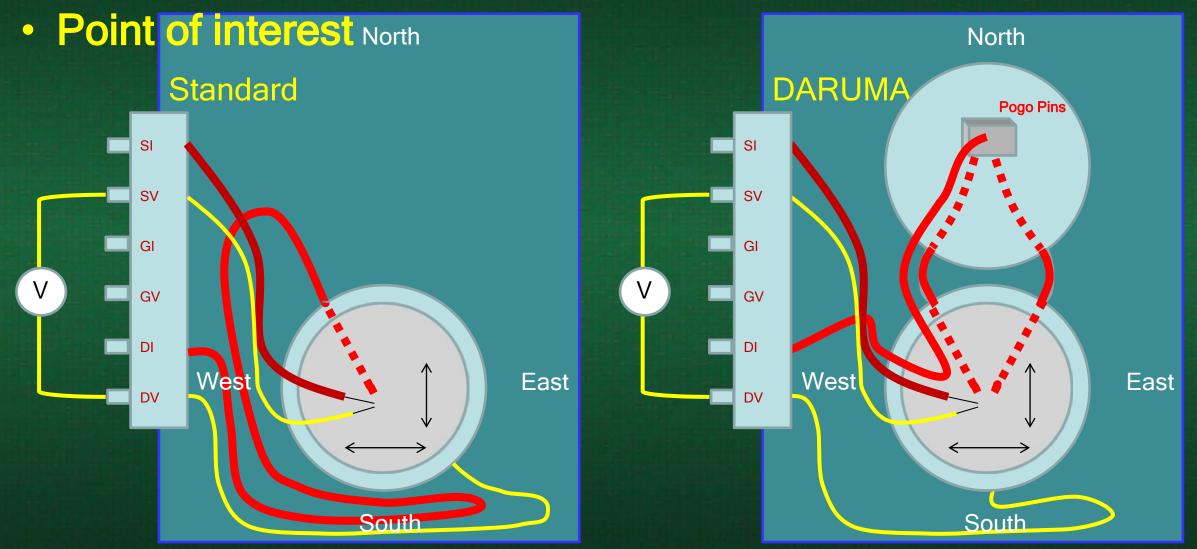

# **Overview of DARUMA Chuck (1)**

#### Standard connection

#### **DARUMA** connection

# **Overview of DARUMA Chuck (2)**

# **Advantage of DARUMA Chuck**

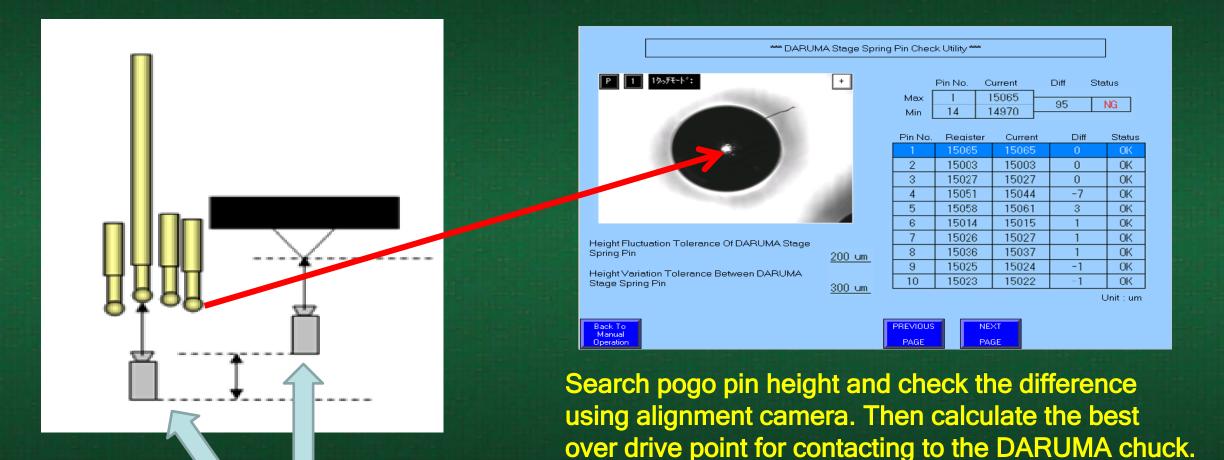

# **Alignment for Pogo Pins**

#### Probe to pad alignment camera

# Maintenance

Turn ON voltage/Contact resistance <- Chuck surface condition</li>

Large current/Inductive load test -> Deteriorating chuck top Required periodical chuck top maintenance

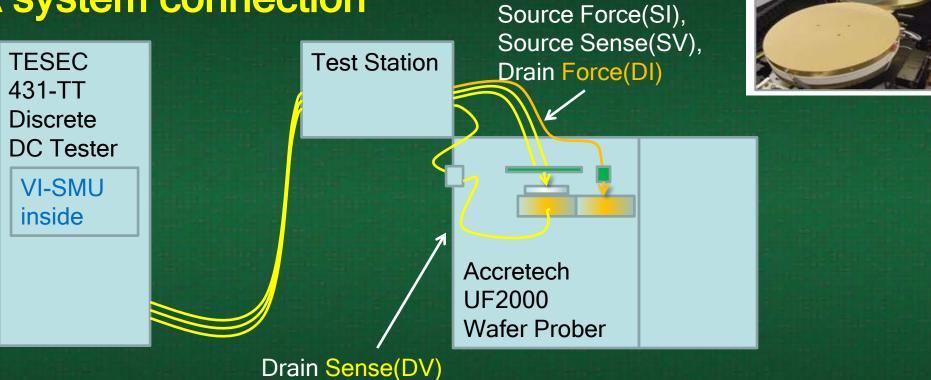

# **Overview of Evaluation Setup**

# Verification

Test Station

### DARUMA System connection

TESEC

431-TT

Discrete

DC Tester

**VI-SMU**

inside

Gate Force(GI), Gate Sense(GV), Source Force(SI), Source Sense(SV), Drain Force(DI)

Accretech

Wafer Prober

UF2000

Drain Sense(DV)

# Verification

### [Measurement result-1] Test condition : Rds<sub>(on)</sub>, IDS=200A, Test time=500uS

### Stage type

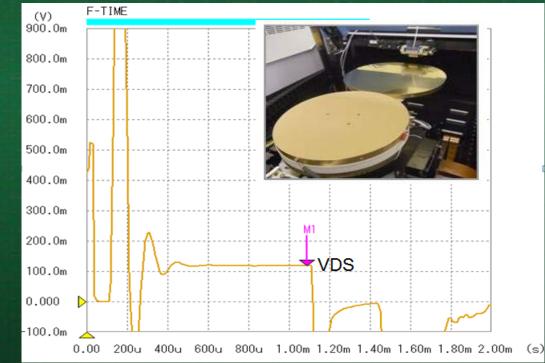

# Verification

### [Measurement result-2] Test condition : Rds<sub>(on)</sub>, IDS=200A, Test time=1000uS

Comparison with standard stageTest condition : Rds(on), IDS=200A, Test time=1000uSStandard connectionDARUMA connection

Takahashi, Toyoda

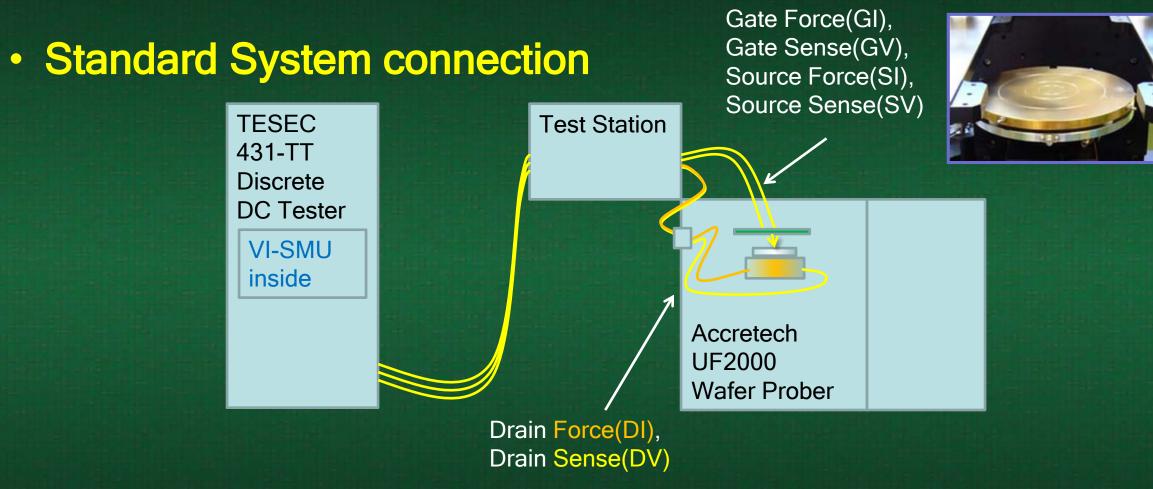

### Standard system connection

Source Force(SI), Source Sense(SV) TESEC Test Station 431-TT Discrete **DC** Tester **VI-SMU** inside Accretech UF2000 Wafer Prober Drain Force(DI),

Gate Force(GI),

Gate Sense(GV),

Drain Sense(DV)

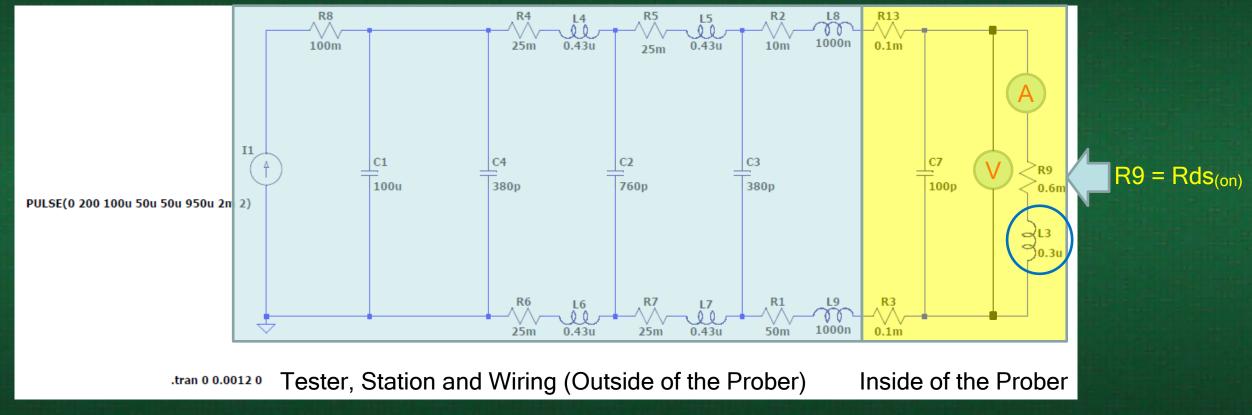

### DARUMA system connection

Gate Force(GI),

Gate Sense(GV),

### Point of interest

Device Connection Comparison Table Standard vs DARUMA

|  |    |              | the second design of the second se |

|--|----|--------------|-----------------------------------------------------------------------------------------------------------------|

|  |    | Standard     | DARUMA                                                                                                          |

|  | GV | Probe Card   | ÷                                                                                                               |

|  | GI | Probe Card   | ÷                                                                                                               |

|  | SV | Probe Card   | ÷                                                                                                               |

|  | SI | Probe Card   | ÷                                                                                                               |

|  | DV | South East   | South                                                                                                           |

|  |    | of the Stage | of the Stage                                                                                                    |

|  |    | North West   | North of the                                                                                                    |

|  | DI | of the Stage | Stage                                                                                                           |

|  |    | via 2m Wire  | via DARUMA                                                                                                      |

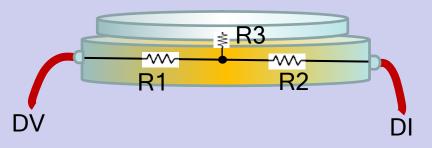

### Point of interest

R3 is Contact resistance between Wafer and Stage.

R1 and R2 do not affect to VDSON value. R3 is added to VDSON. It is only R3 that increases VDSON. Measurement values are almost independent of location.

### Simulated model Schematics for Standard connection

Takahashi, Toyoda

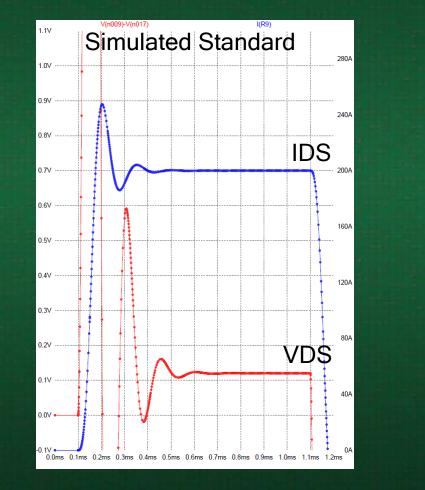

### Waveform Simulated vs Actual, @Standard

SW Test Workshop | June 4-7,2017

(s)

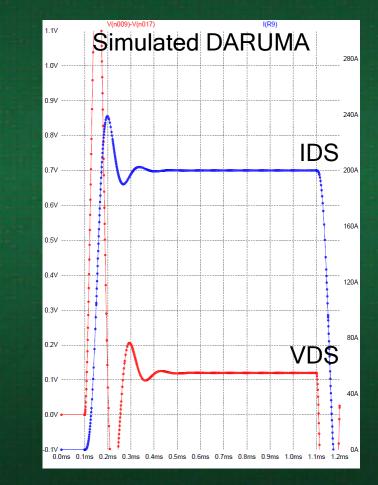

### Simulated model Schematics for DARUMA connection

Takahashi, Toyoda

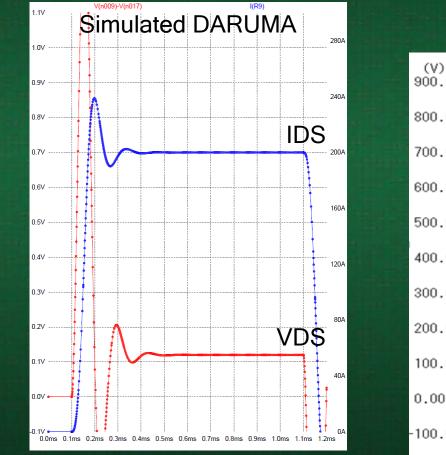

### Waveform Simulated vs Actual, @DARUMA

Takahashi, Toyoda

SW Test Workshop | June 4-7,2017

(s)

### Simulated Waves comparison Standard vs DARUMA

# Conclusion

- Demand for higher-efficiency of Mobile and Automotive devices, is driving the need for MOSFETs with even lower Rds<sub>(on)</sub>.

- Improving measurement accuracy while at the same time reducing device stress will continue to be test challenges for the future.

- However, by employing a "DARUMA" stage, these test challenges can be met at wafer probe when testing (Rds<sub>(on)</sub>) on MOSFETs. Ls will be minimized to enable reduced test time (especially at high current). By reducing test time, temperature rise will be reduced producing less stress on the DUT also resulting in more stable and accurate measurements.

# Acknowledgements

We would like to thank the following colleagues for supporting this workshop.

ACCRETECH Yuji SHIGESAWA Tomoyuki MYOJO Shoji TERADA

Yuichi KAKIZAKI Kiyoaki KOYAMA Muneo ISHINOHACHI Masashi HOSHINO

\$ 5 6

We hope these efforts bring further development of products that will contribute to societal advancements.