### SW Test Workshop Semiconductor Wafer Test Workshop

### Probing solutions and inherent customization to enable advanced copper-based 3D integration schemes

Dong-pill Yang, SEC Jung-woo Sung, SEC

Emanuele Bertarelli, Technoprobe Raffaele Vallauri, Technoprobe Dong-Hun Lee, Technoprobe Korea Marco Prea, Technoprobe

June 3-6, 2018

### **Overview**

- Background: Cu probing & Fan-Out Panel-Level Packaging (FOPLP) trends

- Probing technology path finding and know-how acquisition on Cu-based applications

- 1) Cu probing: early studies

- 2) Processors probing

- Customer A case study

- Customer B case study

- 3) Wide I/O memories probing

- IMEC case study

#### • Moving to FOPLP, RDL Cu pad probing: SEC case study

- 1) Technology customization

- 2) Results of qualification at Customer

- Lessons learned and future work

### **Cu probing trend**

- A general trend can be identified in EWS towards Cu probing

- This is one of the key ingredients to allow semiconductor manufacturers to exploit 3D packing architectures with high interconnection density

- Main drivers are recent mobile processors and high performance memories

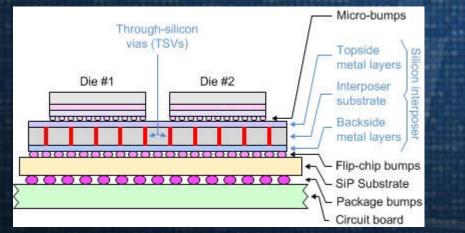

2.5D IC / System in Package using a Si interposer and through-silicon vias (TSVs)

3D IC / System in Package example: Memory dies stacked and attached to logic die and/or analog/RF die attached to a digital logic die, ...

SW Test Workshop | June 3-6, 2018

Ref. [1]

### **3D IC benefits versus 2D IC**

#### Smaller footprint

More functionalities into a small space

#### Shorter interconnect length

- Decrease power consumption and power budget

- Increase bandwidth = high bandwidth memories, parallel access

#### Design freedom

- Higher order of connectivity vs. 2D architecture

- Heterogeneous components can be integrated

#### Cost improvements

Partitioning of large chips into smaller dies for improved yield and testability

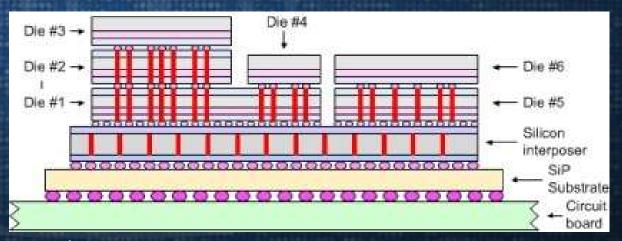

## Packaging trend in mobile applications

Ref. [2]

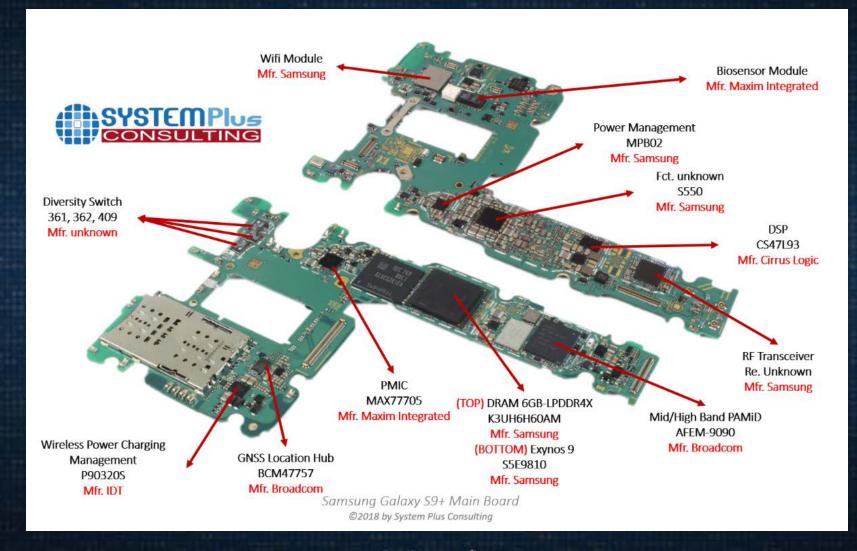

# **Readiness for fan-out panel level packaging**

Emanuele Bertarelli

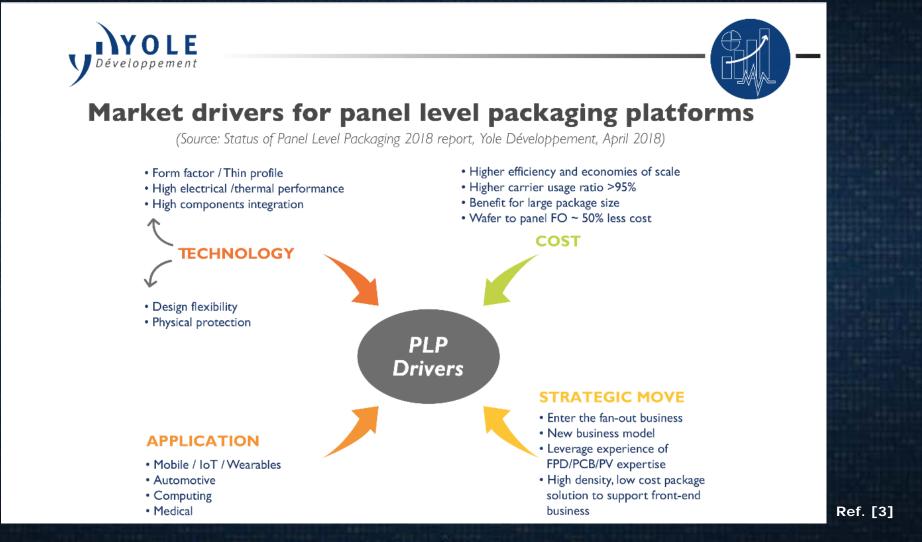

# Panel level packaging technology drivers

Emanuele Bertarelli

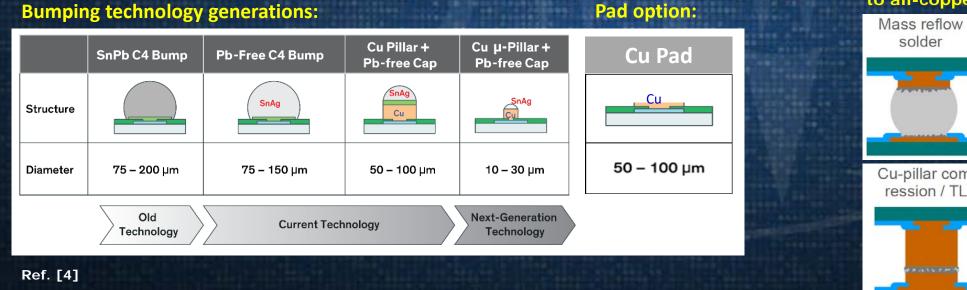

### **Cu-based interconnects**

- Reducing solder amounts (finally to zero), Cu-based bumped interconnects gain lower pitch capability and higher current carrying capability

- Cu pad is an interesting option for RDL layer testing

#### Roadmap from solder to all-copper interconnects:

#### SW Test Workshop | June 3-6, 2018

Ref. [5]

### **Probing technology requirements**

#### Processors probing requires...

- High current carrying capability

- Probing at both RT and Hot

- Minimum pitch is not critical ( $\geq$  90 µm FA)

### • Wide I/O memories probing requires...

- Ultra fine pitch ( $\leq$  50  $\mu$ m FA)

- Current carrying capability is not critical

### **Early studies**

From the beginning, explorative studies on Cu blank wafers showed the importance of tip material and scrub control to guarantee contact stability

### **Early studies**

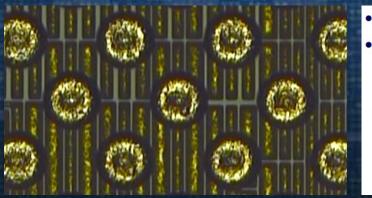

#### • Looking at Cu surface:

- Surface morphology and metallurgy differ largely from Customer to Customer, requiring dedicated customization studies

- Cu surface (pads, pillars) are more prone to oxidation or at least the oxide layer is impacting more contact resistance – than Al surface (pads)

**Customer A**

**Customer B**

#### **Customer IMEC (see paper)**

Refs. [6,7]

### **Processor probing**

### Technology development through

- Probing technology path finding

- Customer A case study

- Customer B case study

### **Processor probing**

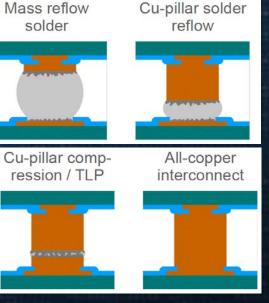

**Probing technology development**

- TP reference technology is TPEG<sup>™</sup> T3 LCR2

- Arianna<sup>™</sup> A3 HC & Arianna<sup>™</sup> AS90 HC are proposed for this application to

- Improve contact resistance stability

- Improve current carrying capability

| PARAMETER       | TPEG™ T3 LCR2     | Arianna™ A3 HC    | Arianna™ AS90 HC    |

|-----------------|-------------------|-------------------|---------------------|

| Needle diameter | 2 mils equivalent | 2 mils equivalent | 2.4 mils equivalent |

| X/Y Alignment   | ±10 μm            | ±10 μm            | ±10 μm              |

| Z planarity     | Δ 20 μm           | Δ 20 μm           | Δ 20 μm             |

| Min pitch FA    | 90 µm             | 90 µm             | 90 µm               |

| CCC             | 500mA             | 1200 mA           | 1500 mA             |

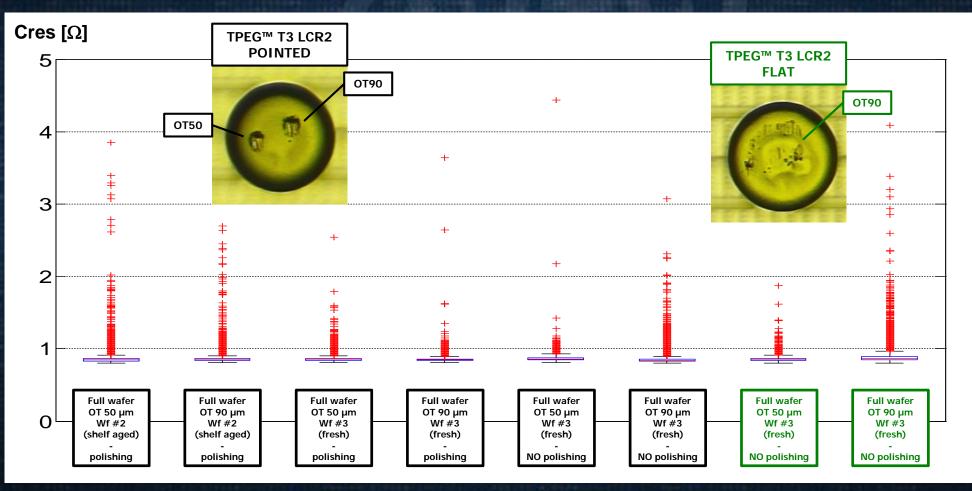

### Processor probing Customer A case study

#### • TPEG<sup>™</sup> T3 LCR2: comparing pointed vs flat tip

### Processor probing Customer A case study

#### • Moving to Customized Tip solution: TPEG<sup>™</sup> T3 LCR2 vs Arianna<sup>™</sup> A3 HC

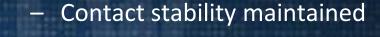

### **Processor probing** Customer B case study – 1<sup>st</sup> run

#### • Customer required to emulate Cu bump wafer testing as follow:

- 3x full wafers with polishing frequency 100, OD =  $75\mu$ m electrical

- 4x full wafers no polishing (tot. 1800 PTDs), OD =  $75\mu$ m electrical

- Success criterion: maximum Cres Probe Std Dev < 250 m $\Omega$

| Technology     | Tip<br>Option | Scrub<br>Option | Probe<br>count | Max Probe SD<br>polishing | Max Probe SD<br>NO polishing |

|----------------|---------------|-----------------|----------------|---------------------------|------------------------------|

| TPEG™ T3 LCR2  | Pointed       | Controlled      | 48             | 13 m $\Omega$             | 13 m $\Omega$                |

| TPEG™ T3 LCR2  | Flat          | Controlled      | 48             | $4 \text{ m}\Omega$       | 19 m $\Omega$                |

| Arianna™ A3 HC | Customized    | Controlled      | 48             | $8{ m m}\Omega$           | $6 \text{ m}\Omega$          |

| Arianna™ A3 HC | Customized    | Standard        | 48             | 20 m $\Omega$             | $87 \text{ m}\Omega$         |

#### Stable electrical contact stability is found for all technologies

- Superior performances are confirmed for TP Customized Tip solution with controlled scrub

- Controlled scrub mechanics is providing a measurable advantage

### **Processor probing** Customer B case study – 1<sup>st</sup> run

- Arianna<sup>™</sup> A3 HC, standard scrub

- Max Probe SD = 87 m $\Omega$

- Slight, progressive contact instability

- Arianna<sup>™</sup> A3 HC, controlled scrub

- Max Probe SD = 6 m $\Omega$

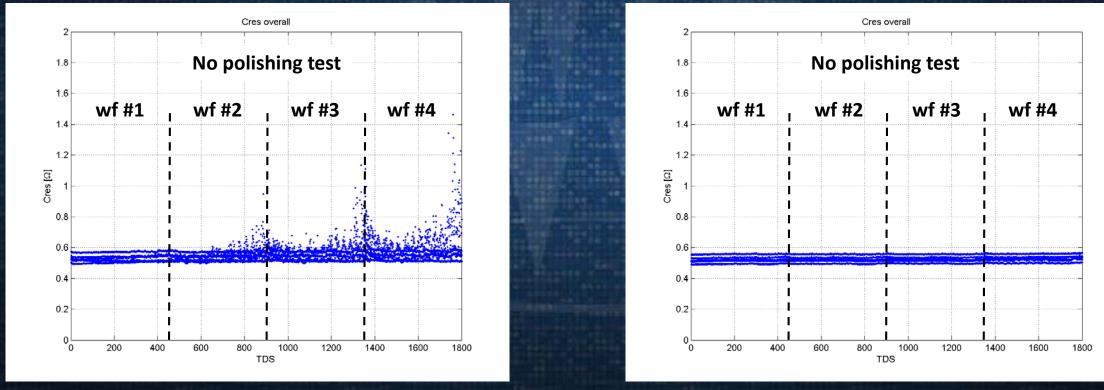

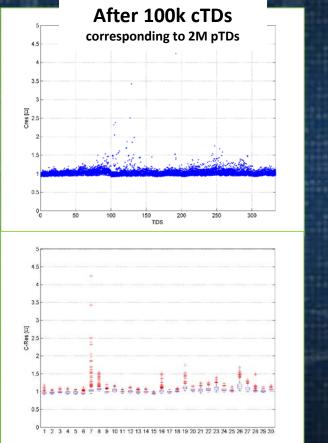

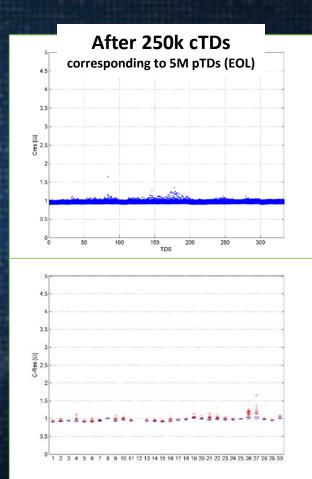

### **Processor probing** Customer B case study – 2<sup>nd</sup> run

#### • Based on positive results with Arianna<sup>™</sup> A3 HC technology, the Customer required to

- Further improve current carrying capability

- Assess stability of electrical performances over entire life span  $\rightarrow$  new evaluation procedure

- Improve HF performances

#### • Technoprobe proposed to move to Arianna<sup>™</sup> AS90 HC

- Customized tip evaluated on Cu blank, showing high Cres stability

- Cres ~ 0.5  $\Omega$  (including interconnection)

- Maximum Cres Probe Std Dev = 5 m $\Omega$

- Total standard deviation (on 48 probes) = 27 m $\Omega$

- Dedicated tip designs to probe on Customer wafer are developed: Geometry 1 & Geometry 2

SW Test Workshop | June 3-6, 2018

**Overall Cres**

cleaning freq 100)

(1000 TDs,

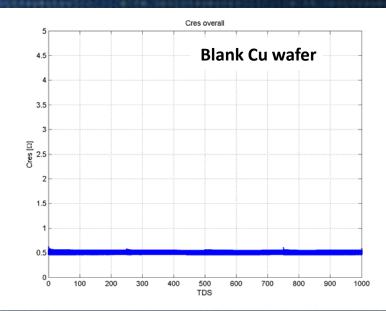

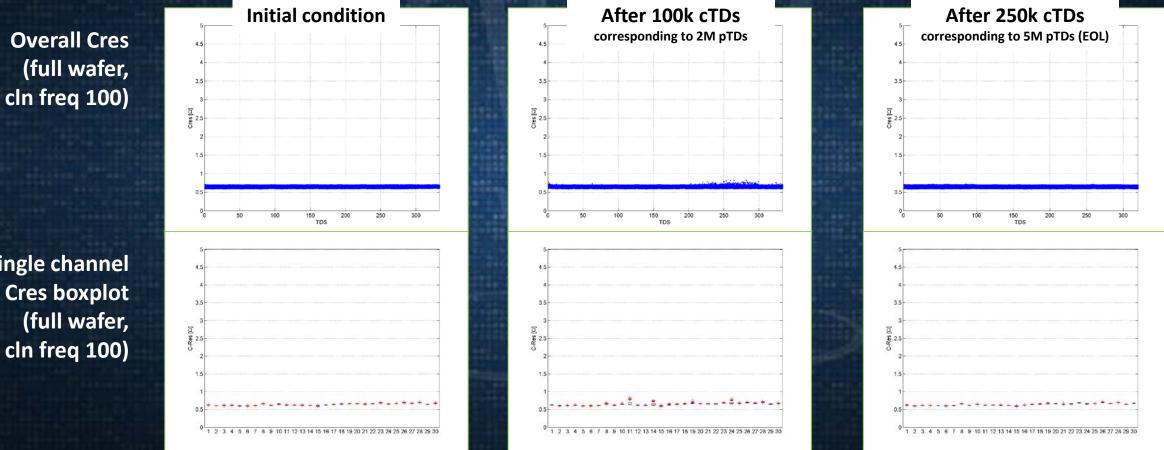

### **Processor probing** Customer B case study – 2<sup>nd</sup> run

#### • Arianna<sup>™</sup> AS90 HC with Geometry 1 – cleaning ageing test

Single channel Cres boxplot (full wafer, cln freq 100)

**Overall Cres**

cln freq 100)

(full wafer,

### **Processor probing** Customer B case study – 2<sup>nd</sup> run

#### Arianna<sup>™</sup> AS90 HC with Geometry 2 – cleaning ageing test $\bullet$

Single channel **Cres boxplot** (full wafer,

## Wide I/O memories probing

#### Technology development through

- Probing technology path finding

- IMEC case study (ref.[8] dedicated paper at SWTW 2018 presented by IMEC "Leading-Edge Wide-I/O2 Memory Probing Challenges: TPEG<sup>™</sup> MEMS Solution")

### Wide I/O memories probing Probing technology path finding

TSV/μ-bump memory dies probing needs ultra-fine pitch FA technologies

- TP first solution to address 40µm FA is dated 2010 to provide an engineering level solution (FT 1.0, mechanical manufacturing)

- As further step, TP applied TPEG<sup>™</sup> MEMS concept also to ultra-fine pitch

#### TPEG<sup>™</sup> MEMS Tx0 probe family was developed

Target application is 60-50-40μm FA probing over Al pads or μ-bumps

Now the respective Arianna<sup>™</sup> Ax0 solutions are being introduced

– Target application is 60-50-40 $\mu$ m FA probing over Cu pads or  $\mu$ -pillars

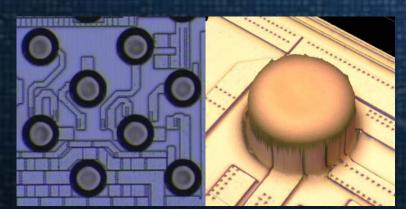

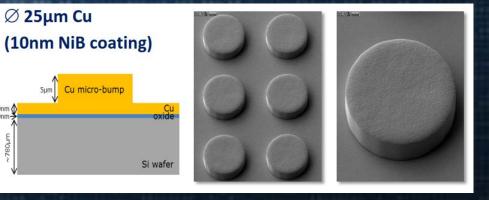

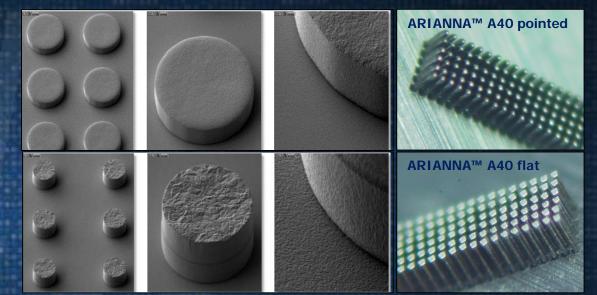

### Wide I/O memories probing Customer IMEC case study

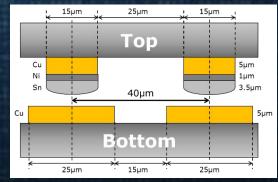

#### IMEC Blanket Micro-Bump wafer

- JEDEC Wide I/O 2 (JESD-229/2)

- Top side: Cu/Ni/Sn  $\varnothing$  = 15 $\mu$ m

- Bottom side: Cu (+NiB)  $\emptyset$  = 25 $\mu$ m

- Micro-bumps shorted by blanket Cu

### • TP probe card

- 73 x 6 probes at 40µm pitch FA

- Micro-wired space transformer

- Arianna<sup>™</sup> A40 flat probe head for Top side

- Arianna<sup>™</sup> A40 pointed probe head for Bottom side

See Refs. [6,7,9] for details.

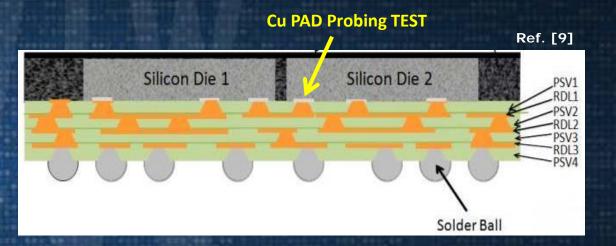

Moving to FOPLP, RDL Cu pad probing

All path finding and know-how acquisition efforts allowed Technoprobe to conceive a solution to cope with requirements of FOPLP, Cu pad probing

Specific SEC challenges and requirements drove us to develop a probing technology capable of:

- Small pad opening

- Thin Cu metallization layer

- Possible irregular pad topography

**Technoprobe Technology customization**

- Requirement from SEC is to probe on Cu pads on RDL

- Main targets for evaluation:

- Same or better electrical contact

performances vs. Al pad reference

Minimal pad damage to allow

safe multiple testing (RT, Cold, Hot)

Arianna<sup>™</sup> AS90 technology with further customized tip geometry and material is selected

- Tip Geometry 3 is selected

- A novel alloy "Type 2" is specifically developed for this application

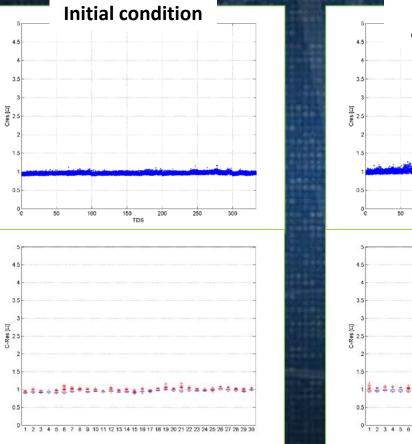

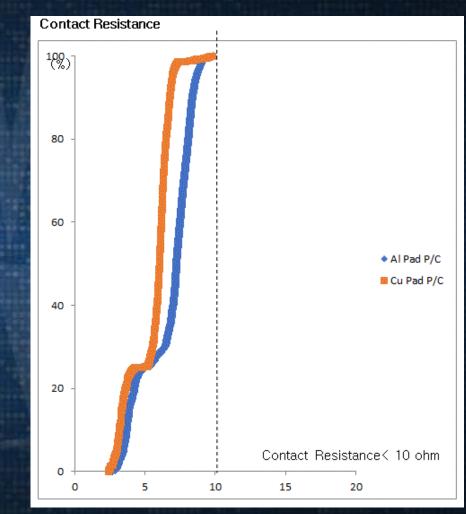

#### **Results of qualification at Customer**

#### Stable Cres is found

Results reported are for full wafer trial run

- Probing electrical performances are exceeding Al Pad benchmark in terms of

- LVCC Margin test

- DC test

- DFT(Scan) test

- Function test

- Analog test

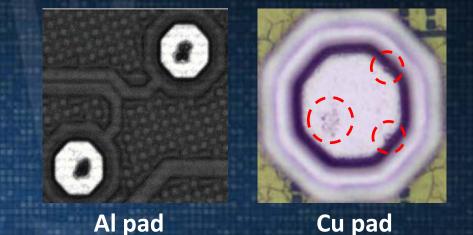

### SEC case study Results of qualification at Customer

#### Cu pad damage is very limited

- Scrub depth is not exceeding 300 nm

- No delamination issues found

Based on wear out data from the field, expected lifetime with current cleaning recipe is exceeding 1M probing TDs for RT testing

**Results of qualification at Customer**

- Arianna<sup>™</sup> AS90 technology has been qualified by SEC for RT & HT testing and released to mass production

- Stable Cres is found with requested scrub mark depth and size

- This result is achieved by a dedicated customization of probe tip (alloy and geometry)

### Lessons learned

Cu probing on diverse target structures (pads, pillars, μ-pillars) is gaining momentum driven by processors and high performance memories testing requirements in the evolving 3D packing architectures scenario

Key ingredients implemented by Technoprobe to successfully probe on different Cu structures are

- Tip : customized geometry and alloys

- Scrub control to guarantee contact stability during probing process

- ... and a joint development path between probe card vendors and customers, allowing Technoprobe to verify and further customize probing solution for unprecedented electrical and mechanical performances

### Thank you for your attention!

Dong-Pill Yang Principal Engineer, Product & Test Eng Team, SEC d37.yang@samsung.com

Jung-Woo Sung Senior Engineer, Product & Test Eng Team, SEC jungwoo.sung@samsung.com

Dong-Hun Lee General Manager, Technoprobe Korea dh.lee@technoprobekorea.com Emanuele Bertarelli, Ph.D. (Presenter) R&D Manager, Technoprobe emanuele.bertarelli@technoprobe.com

Raffaele Vallauri R&D and Process Eng Director, Technoprobe raffaele.vallauri@technoprobe.com

Marco Prea EVP WW Customer Operations, Technoprobe marco.prea@technoprobe.com

The work done by technical team members at Technoprobe R&D & Process Engineering Department is gratefully acknowledged.

Emanuele Bertarelli

### References

[1] M. Maxfield, 2D vs. 2.5D vs. 3D ICs 101 – EE Times Website [2] System Plus Consulting Website (http://www.systemplus.fr/) [3] Yole Développement Website (http://www.yole.fr/2014-galery-3D.aspx#I0002f5d1) [4] M. Lapedus, *Electroplating IC Packages* – Semiconductor Engineering Website [5] L. Del Carro et al., Functional electronic packaging – IBM Research Zurich Website [6] R. Vallauri et al., Challenges probing next generation full array products with 60 μm pitch and below – Proceedings of SWTW2015 (S01\_03) [7] R. Vallauri et al., Ultra-Fine Pitch Probing Challenges and Solutions – 1st IEEE European Test Symposium (2016) [8] F. Fodor et al., Leading-Edge Wide-I/O2 Memory Probing Challenges: TPEG<sup>™</sup> MEMS Solution – Proceedings of SWTW2018 (S02 03) [9] W.K. Choi et al., Ultra-Fine Pitch RDL Development in Multi-layer eWLB (embedded Wafer Level BGA) Packages - IMAPS 2015 Orlando