# High Power goes Vertical

Diana Damian - Rainer Gaggl - Gerald Hermann - Mauro Serra - Sebastian Salbrechter

### **Overview**

- Motivation

- Current Density on Chip Cantilever vs. Vertical Probes

- Chip Pad Metallization Cres Stability

- Probes Protection

- Conclusion

### Motivation

Power modules used in Electro-automotive application

**Extremely harsh test conditions for power devices** (IGBTs, Diodes, MOSFETs) dictated by Automotive application

- short circuit test (SCT) at up to 10x rated device current (shooting pulses of up to 3000 A on a single chip...)

- highest current densities made possible by SiC devices

- at hot temperature

- high voltage dynamic switching tests

- bare die test (KGD)

### Motivation - why going Vertical?

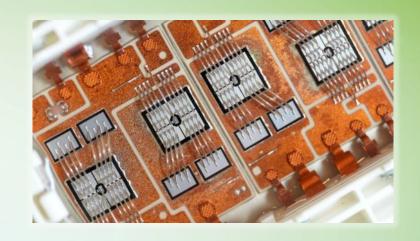

- Cantilever probes technology is well established for KGD power test up to 1000 A

- runs into limitations at very high chip current densities (A/mm² on chip pad)

- Vertical probes technology an option?

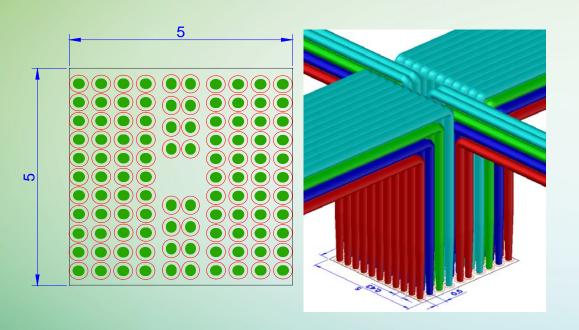

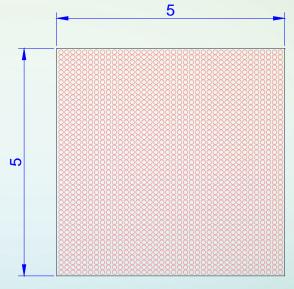

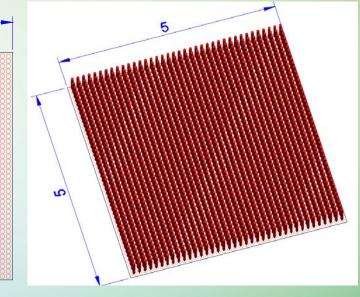

# Current densities for cantilever and vertical probe cards Small Chips – 5x5mm

Cantilever 40A/mm<sup>2</sup>

Vertical 70A/mm<sup>2</sup>

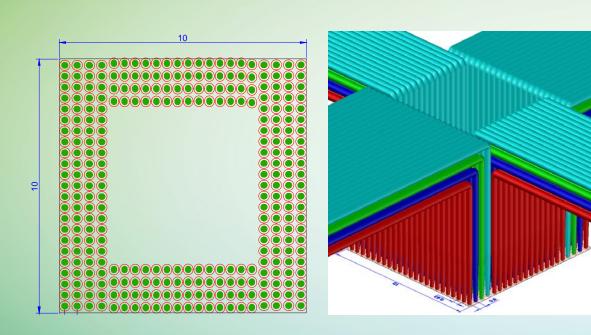

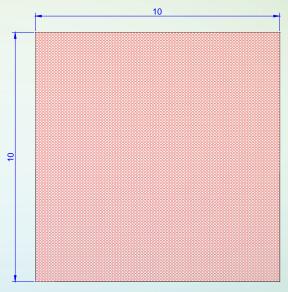

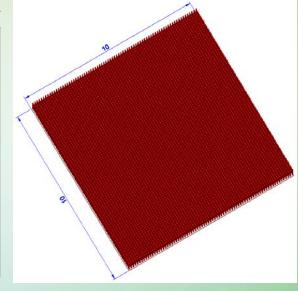

# Current densities for cantilever and vertical probe cards Big Chips – 10x10mm

Cantilever 30A/mm<sup>2</sup>

Vertical 70A/mm<sup>2</sup>

### **Current densities for cantilever and vertical probe cards**

#### **Conclusion:**

- Due to geometrical constraints regarding number of needle layers, current density of cantilevers decreases with increasing chip size

- With vertical technology, the current density remains almost constant as the chip area increases

### **Overview**

- Motivation

- **Current Density on Chip Cantilever vs. Vertical Probes**

- Chip Pad Metallization Cres Stability

- Probes Protection

- Conclusion

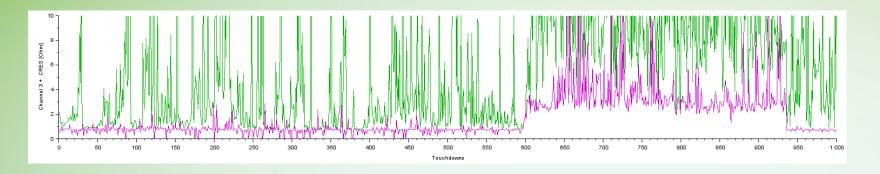

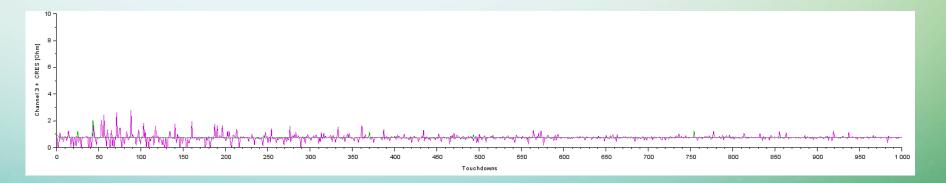

### Cres effect on probes lifetime

Ideal probing condition- constant Cres

Less than ideal condition- varying Cres

Current imbalance – probe damage

### **Contact Resistance vs Pad Material**

Al pads

## Pad material is extremly important in terms of contact resistance

Cu pads

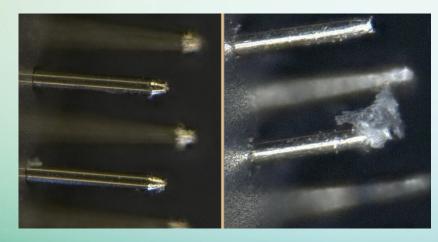

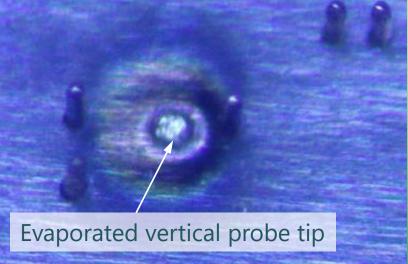

### What matters...

- Constant CRES is important for current balancing and needle wear

- Sensitive to tip contamination

Before \ After

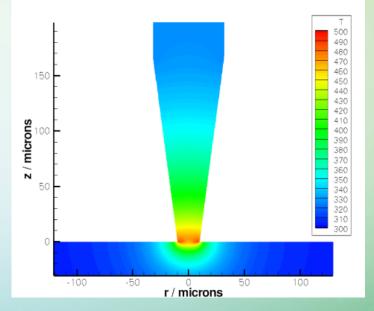

Probe tip heating in high current short pulse condition

### **Overview**

- Motivation

- **Current Density on Chip Cantilever vs. Vertical Probes**

- Chip Pad Metallization Cres Stability

- Probes Protection

- Conclusion

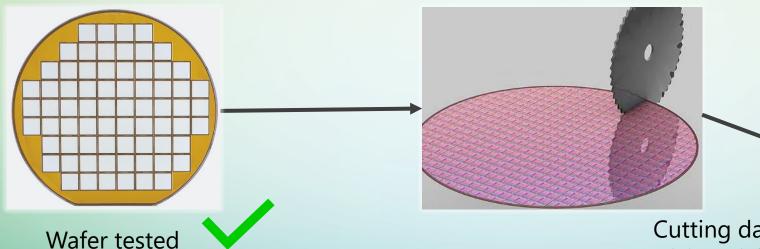

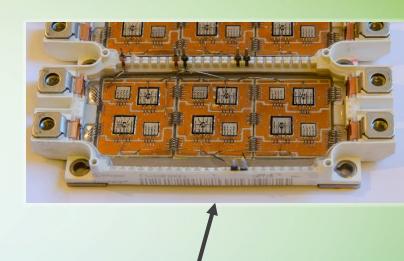

#### Power modules up to 32x

For high module yield, every single diced chip needs to be tested

> High power KGD tests

Cutting damage, Dicing yield

### **High Power KGD Tests**

- Various types of chip failures

- Some situations are critical for the probe card

- Shorted D.U.T. within Avalanche test

- Hot Spot

- Etc.

- > Overload protection

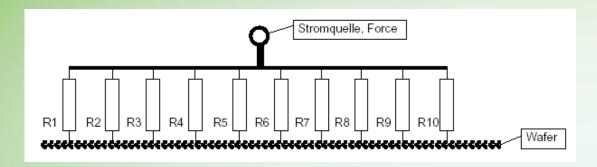

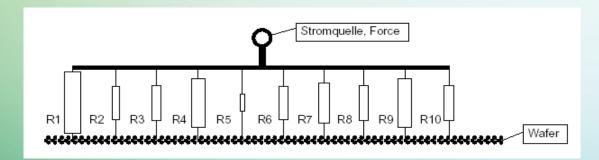

- In general: Need for homogeneous current distribution amongst probes

- > Active current balancing between probes

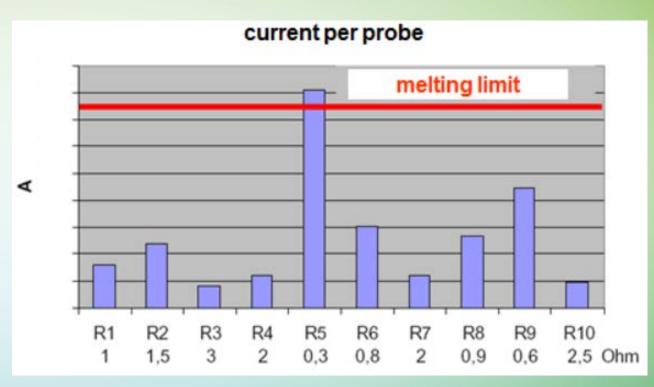

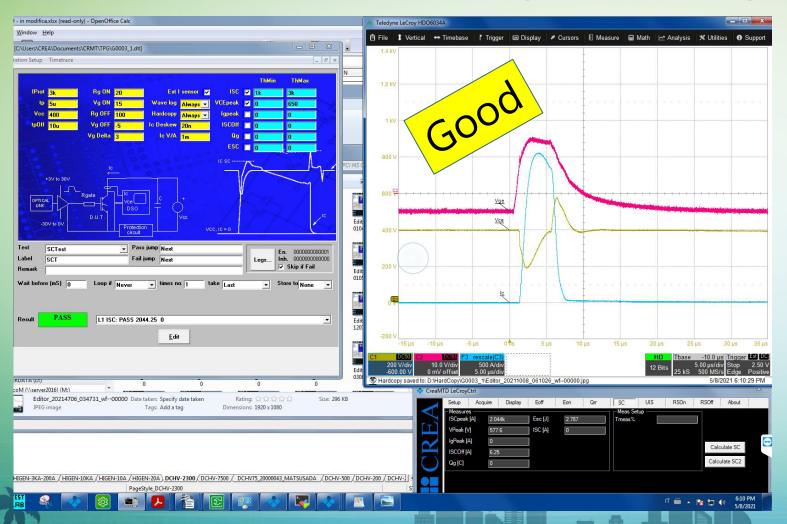

#### Active overcurrent protection

- Monitoring and limitation of current which is drawn at each tester channel

- Realized by CREA Semiconductor test equipment

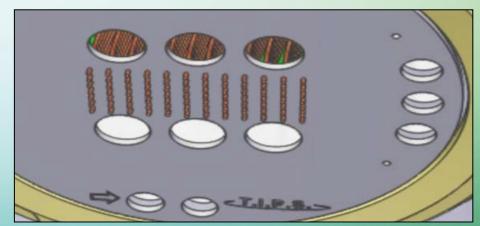

#### Alternative:

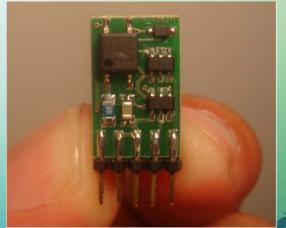

- T.I.P.S. Smart Clamp Technology

- Active current balancing/limiting

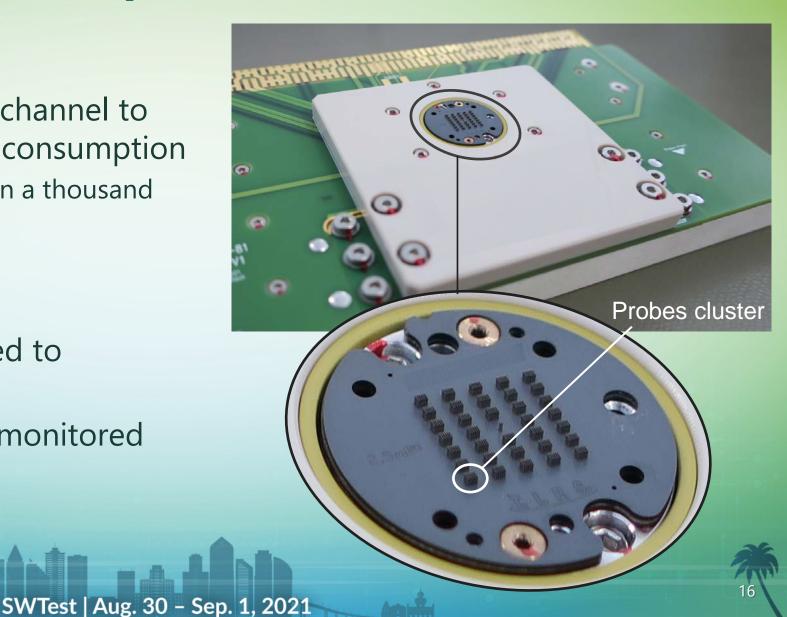

#### • Ideal:

- Every probe has separate channel to monitor and limit current consumption

- Not possible with more than a thousand probes

#### · Real:

- Several probes are bundled to one "cluster"

- Each cluster is separately monitored and protected (limited)

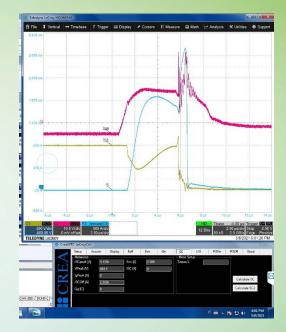

#### BENCH CHIP TEST: SCT TEST 5us @150°C 2000A@400V

### **Overview**

- Motivation

- **Current Density on Chip Cantilever vs. Vertical Probes**

- Chip Pad Metallization Cres Stability

- Probes Protection Overcurrent Protection

- Conclusion

### Conclusion

- Limits for high power KGD application can be pushed further:

- Vertical technology is means of choice

- Overcurrent protection is required to protect probe card in case of chip failure

- Investigations for higher current densities ongoing

- Optimize probes arrangement on chip pads

- Reduce needle pitch

- Increase maximum current per probes

### Acknowledgement / Q&A

- Thanks to everybody that was involved

- CREA Semiconductor Test Equipment

- T.I.P.S. Messtechnik GmbH

- If you need further information please contact:

- sebastian.salbrechter@tips.co.at

# High Power goes Vertical

Diana Damian - Rainer Gaggl - Gerald Hermann - Mauro Serra - Sebastian Salbrechter