Aug. 30 - Sep.

#### Next Generation SmartMatrix Probe Card Technology Enables 3000-Parallelism 1TD Test for D1z/D1a DRAM Process Node

# SAMSUNG

Joe Ceremuga (Speaker) Director, Memory Products, FormFactor ChangHyun Cho Principal Engineer, EDS team, Samsung

#### SmartMatrix 3000XP: Agenda

- Semiconductor memory market demand

- 1-Touchdown wafer test efficiencies

- SmartMatrix 3000XP features and benefits

- Technical challenges solved and performance feedback

- Summary and Acknowledgements

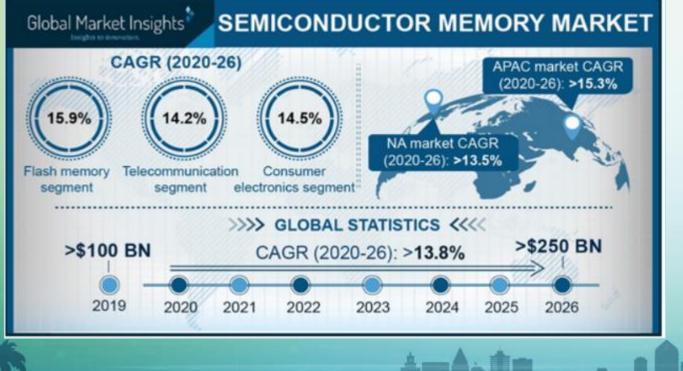

### **Strong Memory Market: Continued Growth**

DRAM demand has been strong through 2020-2021, expect to continue with applications growth

#### Leading IC Product Segments in 2020

Sales and Revenue Growth

| Rank  | Sales                             | \$M               | Revenue Growth                                    | 20/19<br>% Chg |

|-------|-----------------------------------|-------------------|---------------------------------------------------|----------------|

| 1     | DRAM                              | \$65,215          | NAND Flash                                        | 25%            |

| 2     | NAND Flash                        | \$55,154          | Cellphone Application MPUs                        | 24%            |

| 3     | Computer CPU                      | \$43,848          | Wired Comm—Spcl Purp Analog                       | 20%            |

| 4     | Computer and Periph—Spcl Purp Log | ic \$31,340       | Computer and Periph—Spcl Purp Logic               | 15%            |

| 5     | Cellphone Application MPUs        | \$26,615          | Wireless Comm—Spcl Purp Logic                     | 12%            |

| Sourc | e: IC Insights                    | Rankings apply to | IC product categories with more than \$100M in an | inual sales.   |

#### **DRAM Industry Growth Prospect**

- 2021-2026 9.7% CAGR

- ~\$65BN → ~\$110BN

Source: MarketWatch Aug '21

#### **DRAM Key Applications**

- Server/big data

- Mobile devices

- PC

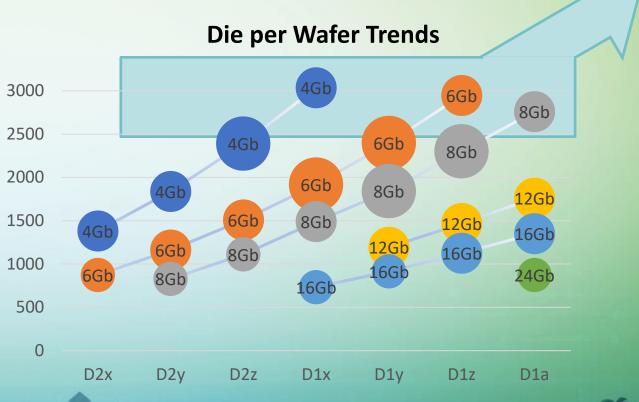

#### **Advancement of Die Per Wafer (DPW)**

- Latest process nodes support die shrink, leading to more die per wafer

- As density grows, die may become larger, but continued nodes drive increase in DPW.

**DRAM Process Roadmaps (for Volume Production)**

|                         |                                                                                                       | 2015                                                                           | 2016      | 2017                               | 2018                     | 2019                     | 2020 | 202  | <u> </u> |

|-------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-----------|------------------------------------|--------------------------|--------------------------|------|------|----------|

| Samsı                   | ung                                                                                                   |                                                                                | 1xnm      | 1ynm                               |                          | 1znm 1αnm                |      |      | 1β       |

| SK Hy                   | nix                                                                                                   | 21nm                                                                           |           | 1xnm                               | 1                        | rnm 1znm 1d              |      |      | m        |

| Micro                   | 'n                                                                                                    | 20nm                                                                           |           | 1xnm                               | 1ynm                     | 1znm 1αnm                |      |      | 1β       |

| схмт                    |                                                                                                       |                                                                                |           |                                    |                          | 1xnn                     | n    |      | 1ynm     |

| Sourc                   | e: IC Insig                                                                                           | hts                                                                            |           |                                    |                          |                          |      |      |          |

|                         | J                                                                                                     |                                                                                |           |                                    |                          |                          |      |      |          |

|                         |                                                                                                       | PRODUCTIC                                                                      | DN        | 2020                               | 2022                     | 2025                     | 2028 | 2031 | 2034     |

| DRAM                    | YEAR OF                                                                                               |                                                                                | DN        | 2020                               | 2022                     | 2025                     | 2028 | 2031 | 2034     |

|                         | YEAR OF                                                                                               | <b>PRODUCTIC</b><br>from above                                                 | DN        | <b>2020</b><br>2.7                 | 2022                     | 2025                     | 2028 | 2031 | 2034     |

|                         | YEAR OF<br>Calculated<br>Chip size (r                                                                 | <b>PRODUCTIC</b><br>from above                                                 |           |                                    | 2022                     | 2025                     | 2028 | 2031 | 2034     |

|                         | YEAR OF<br>Calculated<br>Chip size (r                                                                 | <b>PRODUCTIC</b><br>from above<br>mm)                                          |           | 2.7                                |                          |                          | 2028 | 2031 | 2034     |

| 4G                      | YEAR OF a<br>Calculated<br>Chip size (r<br>DPW (cell s<br>Chip size (r                                | PRODUCTIC<br>from above<br>mm)<br>size*Bit/chip<br>mm)                         | on 300mm) | 2.7                                |                          |                          | 2028 | 2031 | 2034     |

| 4G                      | YEAR OF a<br>Calculated<br>Chip size (r<br>DPW (cell s<br>Chip size (r                                | <b>PRODUCTIC</b><br>from above<br>mm)<br>size*Bit/chip                         | on 300mm) | 2.7<br>2908                        | -                        | -                        | 2028 | 2031 | 2034     |

| 4G                      | YEAR OF I   Calculated   Chip size (r   DPW (cell s   Chip size (r   DPW (cell s                      | PRODUCTIC<br>from above<br>mm)<br>size*Bit/chip<br>mm)<br>size*Bit/chip        | on 300mm) | 2.7<br>2908<br>3.8                 | -                        | - 2.7                    | 2028 | 2031 | 2034     |

| 4G<br>8G                | YEAR OF a<br>Calculated<br>Chip size (r<br>DPW (cell s<br>Chip size (r                                | PRODUCTIC<br>from above<br>mm)<br>size*Bit/chip<br>mm)<br>size*Bit/chip        | on 300mm) | 2.7<br>2908<br>3.8                 | -                        | - 2.7                    | 2028 | 2031 | 2034     |

| 4G<br>8G                | YEAR OF I   Calculated   Chip size (r   DPW (cell s   Chip size (r   DPW (cell s                      | PRODUCTIC<br>from above<br>mm)<br>size*Bit/chip<br>mm)<br>size*Bit/chip        | on 300mm) | 2.7<br>2908<br>3.8<br>1,777        | -<br>3.3<br>1,952        | -<br>2.7<br>2,969        |      | 2031 |          |

| DRAM<br>4G<br>8G<br>12G | YEAR OF I<br>Calculated<br>Chip size (r<br>DPW (cell s<br>Chip size (r<br>DPW (cell s<br>Chip size (r | PRODUCTIC<br>from above<br>mm)<br>size*Bit/chip<br>mm)<br>size*Bit/chip        | on 300mm) | 2.7<br>2908<br>3.8<br>1,777<br>4.7 | -<br>3.3<br>1,952<br>4.1 | -<br>2.7<br>2,969<br>3.3 | 2.6  | 2031 | 2034     |

| 4G<br>8G                | YEAR OF I<br>Calculated<br>Chip size (r<br>DPW (cell s<br>Chip size (r<br>DPW (cell s<br>Chip size (r | PRODUCTIC<br>from above<br>mm)<br>size*Bit/chip<br>mm)<br>size*Bit/chip<br>mm) | on 300mm) | 2.7<br>2908<br>3.8<br>1,777<br>4.7 | -<br>3.3<br>1,952<br>4.1 | -<br>2.7<br>2,969<br>3.3 | 2.6  | 2031 | 2034     |

## **1TD Wafer Test for Highest Efficiency**

- A 1TD Probecard tests all devices on wafer with a single touchdown

- <u>Why</u> is 1TD Wafer Test desirable?

- Highest wafer throughput, maximize test cell capacity

- Do more with less capital equipment (smaller factory / footprint needed!)

- Well-supported with recent demand.

- <u>Time benefit (1TD vs 2TD example)</u>

- Overall Wafer Test Time reduced by 33%. This is a 50% test cell throughput increase

- <u>Challenge</u>: Maintain 1TD probe card capability as DPW continues to increase

## SmartMatrix 3000XP: 1TD 3000DPW Probe Card

SM3000XP is an extension of the proven SmartMatrix probe card developed for high probe count, high parallelism, high density designs

| SM3000XP Key<br>Features                                                    | SM3000XP Benefits                                                                                                                                                             |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>FFI High Density ICs</b><br>ATRE ASICs, FET<br>modules                   | <b>Resolves part placement constraint</b> Enable physical placement of the required components to address the > 3000 parallelism requirement                                  |

| <b>FFI TTRE</b><br>Terminated TRE<br>module and test<br>solution            | <b>Lower cost of test</b> FFI proprietary termination solution<br>enables tester resource sharing of up to 32 times while<br>maintains signal performance on existing testers |

| <b>High-probe count</b><br>and Density<br>3D-MEMS springs on<br>DUTLet      | <b>Shorter lead time</b> Lithographically mount hundreds and thousand of probes on die as opposed to single probe bonding to substrate                                        |

| <b>Thermo-mechanical</b><br><b>stability</b><br>High-range dual temp<br>use | <b>Stability across temperature range</b> T11 MEMS spring with stable coplanarity across up to 170C temperature range (-45C to 125C, typical. 150C max)                       |

|                                                                             |                                                                                                                                                                               |

J Ceremuga, FormFactor Inc.

# **Key Challenges Solved for SM3000XP**

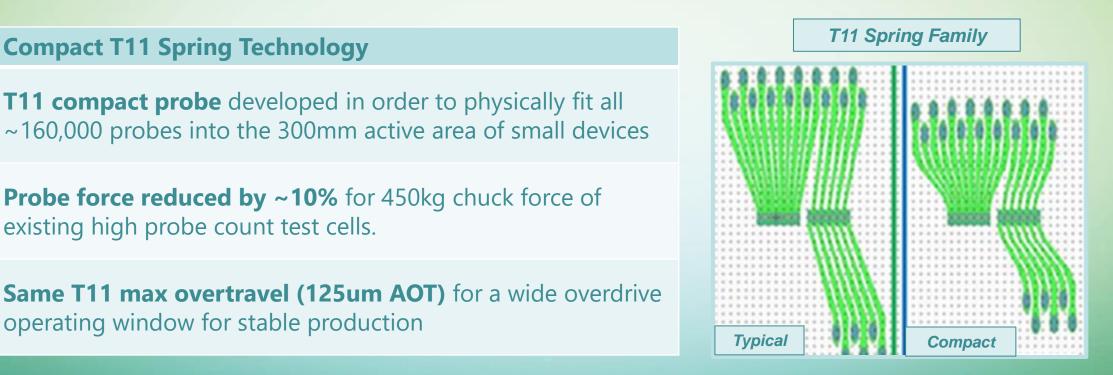

- 1. **Probe density:** >160,000 total probes on small device

- 2. <u>PCB routing/component density</u>: support for >40,000 nets and components

- 3. Signal integrity and PDN: maintain speed and amplitude with sharing

- 4. Mechanical Optimization: must support existing probe card test cell

- 5. <u>Probe mark Pad Size Capability</u>: achieve scrub marks within keepout across dual temperature test range

#### **Probe density: >160,000 total probes on small device**

#### **Developed** a "compact version" of the T11 field proven probe •

Less than 1.5mm length probe supporting 4mm die sizes or smaller

**Compact T11 Spring Technology**

existing high probe count test cells.

operating window for stable production

T11 compact probe developed in order to physically fit all

Probe force reduced by ~10% for 450kg chuck force of

### **PCB Routing / Component Density**

- Need to fit more technology in same probecard space

- Developed more compact and higher density switches and FETs

- ATRE share increased from x16 and x32 enables throughput increase

- 96 site ATE tester can achieve up to 3072// with x32 share

- Improved component placement precision on FFI processes

FFI Carmel 2XDC Boost Double-density 128-Switch per Package

**FFI PPS TRE x8 FET** 50% Area Reduction

J Ceremuga, FormFactor Inc.

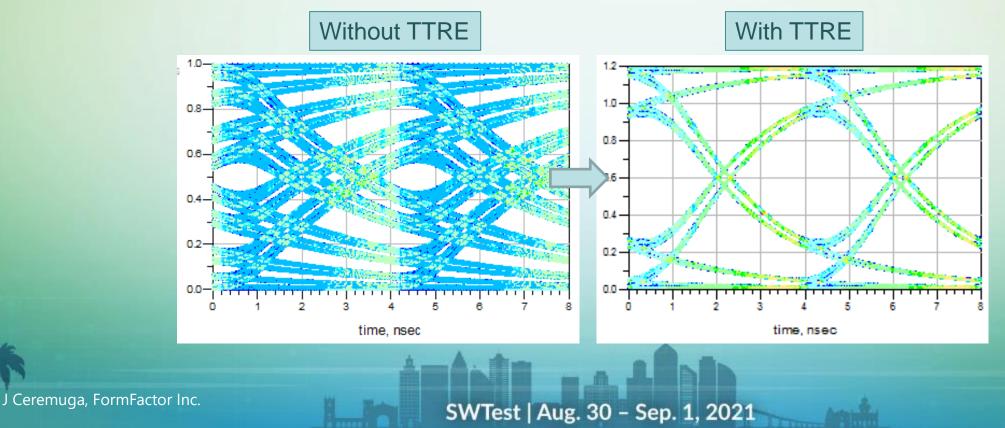

### **SM3000XP x32 TTRE Simulation**

- SI must be capable despite extended resource sharing

- TTRE (terminated TRE) termination improves signal reflection noise at the share point, increases signal amplitude, test speed is not compromised

- X32 probe card SI simulated performance with and without

- Without TTRE, the transient amplitude for x32-TRE share is not sufficient

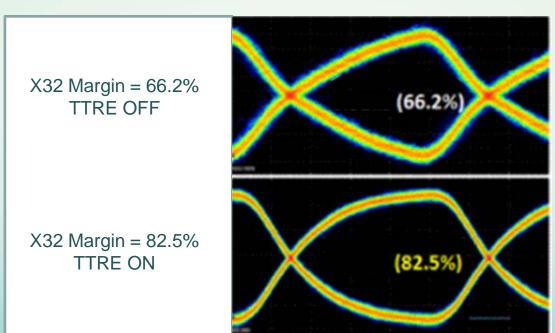

## Signal Performance result – Samsung

Extending Fan-Out / Sharing to X32: Signal transmission loss is compensated with FormFactor's ASIC.

#### **SI Performance Measurement Result**

Acceptable SI performance of x32 sharing with TTRE ON

J Ceremuga, FormFactor Inc.

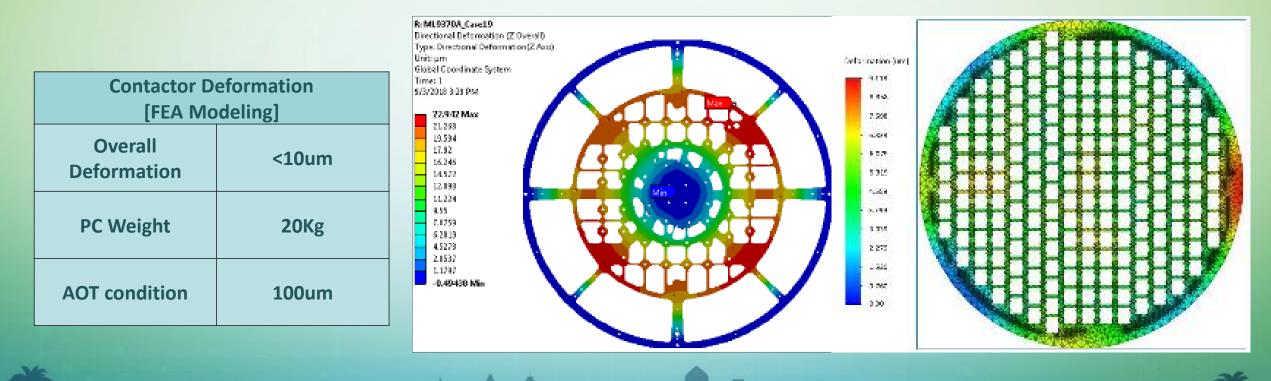

## **Probe card mechanical strength optimization**

- Mechanical Design: Achieved <10um contactor deformation for 160,000-probe load condition

- System stiffness depends on

- Probe card weight limitation, test head height and constraint limitation, and available space for electrical components

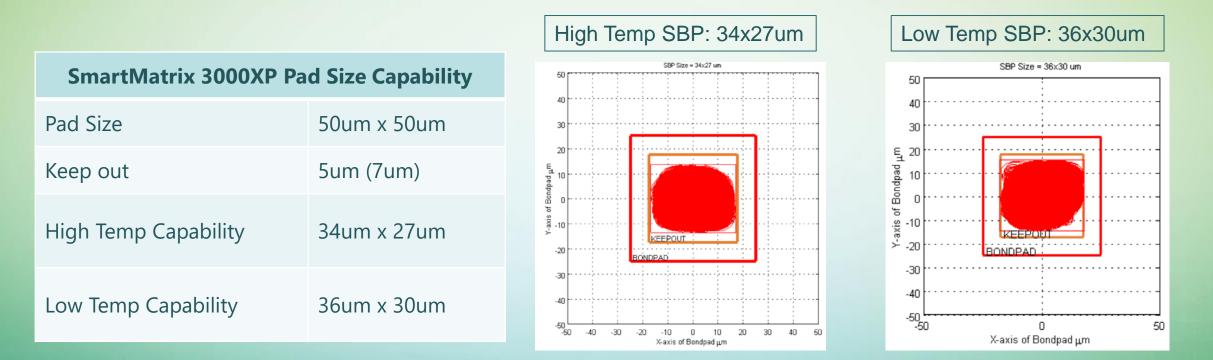

#### **Probe Mark result - Samsung**

- Mechanical Performance: Stable Contact Resistance achieved for ~160K probes using compact T11 probe at production overtravel

- Pad Size Capable: for both hot and cold test condition

Hot Temp Probe Mark

Cold Temp Probe Mark

J Ceremuga, FormFactor Inc.

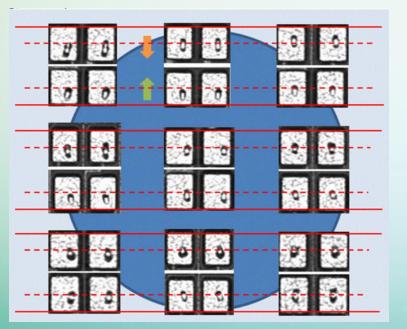

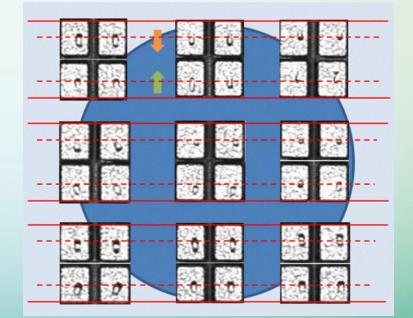

### **Probe Mark Performance, Touchdown on Pattern Wafer**

• <u>Pad Size Capability</u>: Probe mark keepout performance characterized on pattern wafer to ensure all required operating temperatures are satisfactory

Superior probe mark X/Y alignment and Pad Size Capability with 160k probes

J Ceremuga, FormFactor Inc.

#### **SM3000XP Summary**

#### • Summary

- FormFactor and Samsung have collaborated to achieve 1TD production probecard for 3000 DPW device

- The 1TD SM3000XP probecard enables 50% more wafer throughput versus 2TD probecard alternative. Total wafer test time is decreased by 33%.

SWTest | Aug. 30 - Sep. 1, 2021

#### Acknowledgements

- ChangHyun Cho, Samsung EDS Engineer

- MJ Lee, Cameron Harker, and FormFactor R&D Team

# **THANK YOU**

# SAMSUNG

l Ceremuga, FormFactor Inc.

Aug. 30 - Sep. 1, 2021