#### Fine Pitch Probing of Micro-Bumps for **Advanced Packages**

Pardeep Kumar Xallent Inc.

Zehao Li **Engineering Manager** Computer Vision Engineer Xallent Inc.

**Kwame Amponsah CEO & Founder** Xallent Inc.

**Theodore Levin Test Engineer IBM**

**Arthur Gasasira** Manager, Functional and Parametric Test **IBM**

#### Outline

- The market opportunity

- Significance of the problem

- Fine pitch probe cards and the heterogeneous integration test system (HITS<sup>TM</sup>)

- Test results and challenges

- Summary

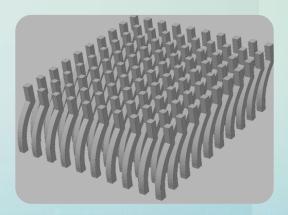

## What is Advanced Packaging?

Advanced semiconductor packaging combines multiple chips into a single package, offering increased functionality, performance, miniaturization, and is crucial for emerging technologies like AI, 5G, autonomous vehicles, and datacenters

## The Market Opportunity

- Advanced packaging is becoming increasingly important in the semiconductor industry due to the limitations of traditional scaling methods (Moore's Law)

- Market opportunity driven by megatrends in AI, 5G, autonomous vehicles and datacenters

- The projected 2029 revenues for advanced packaging is \$79B

with a CAGR of 10.7%

<sup>&</sup>lt;sup>1</sup> Yole intelligence, "Advanced packaging pushing the boundaries of semiconductor probe card market," SWTest 2024

## Significance of the Problem

- Chipmakers and integrators cannot afford to integrate faulty chiplets<sup>2</sup> and interposers into a package. A faulty chiplet or interposer could render an entire expensive package useless at significant cost, time, and effort.

- Thus, a probe card is required to test the functionality of chiplets and interposers prior to and after assembly.

- However, there is lack of fine-pitch probe cards for testing chiplets and interposers with fine pitch micro-bumps, copper pillars, and hybrid bond pads.

<sup>&</sup>lt;sup>2</sup>A chiplet represents a miniature integrated circuit (IC) with distinct set of functions.

#### **Limitations of Conventional Probe Cards**

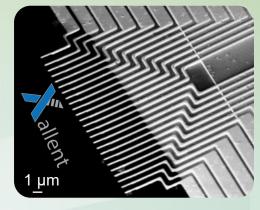

- Traditional probe cards, often based on cantilever or vertical probe technologies face limitations when applied to fine-pitch micro-bump (µbump) probing.

- Limitations include:

- Inadequate spatial resolution making it difficult to accurately contact very small µbumps

- High contact forces which could damage the delicate µbumps

- Poor planarity control leading to uneven contact and inaccurate measurements

## Fine Pitch Probe Cards for Advanced Package Tests

- Fine pitch probe cards enable the testing of current and future chiplets and advanced packages

- Improve packaging yields by proactively determining knowngood-chiplets (KGC) and interposers

- Shorten manufacturing and packaging iterations

**Kelvin Probe**

RF/High Frequency

Probe

**Ultrafine Pitch Probe**

**Grid Array Probes** (Early-Stage Dev)

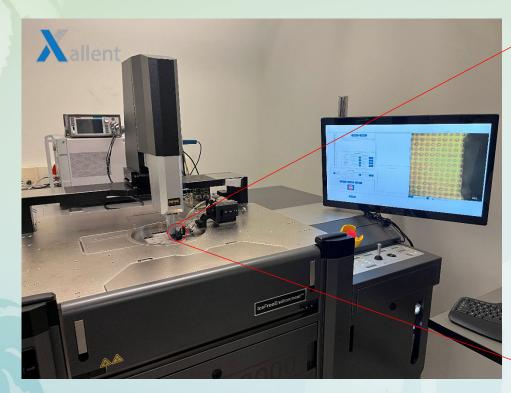

# The Heterogeneous Integration Test System (HITS) Provides the Insights

Reduced Capex with a single test system for multiple test applications System leverages Xallent fine pitch probe cards for electrical, mechanical, and photonics tests

Test system replaces machines up to 5X the price and occupying 5X the lab space.

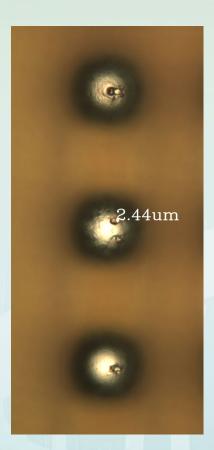

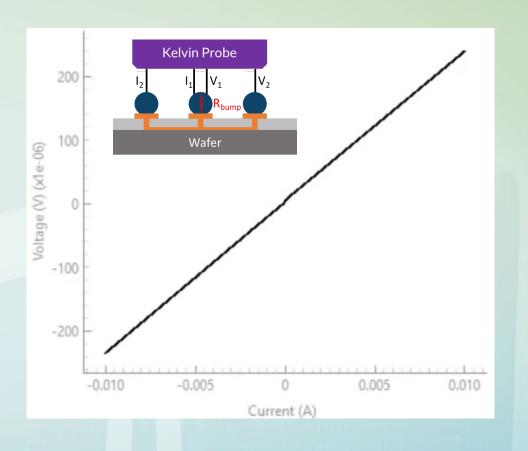

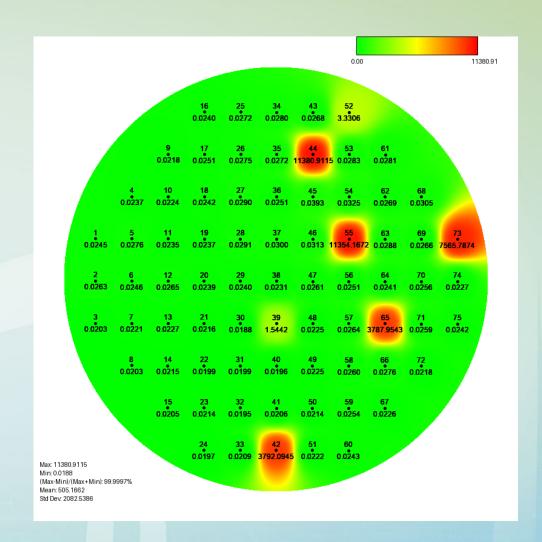

## Case Study: Micro-bumping Process Verification

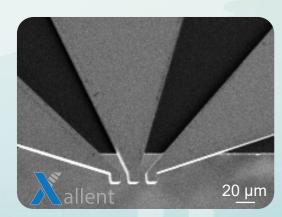

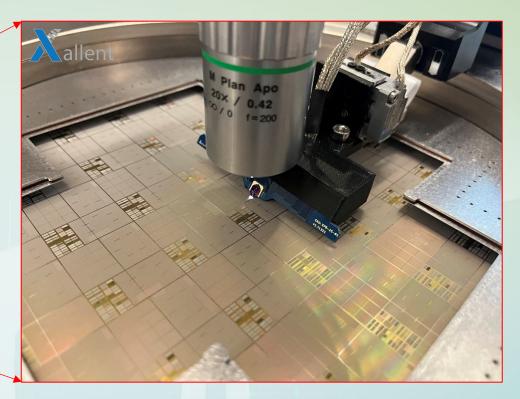

- Objective: Perform wafer acceptance tests (WAT) to determine the integrity of micro-bumping processes

- Platform: Leverage a custom fine pitch Kelvin probe and HITS<sup>TM</sup>

- Data: Measure the Kelvin resistance of 3-µbump test

structures and display results and statistics as a heatmap

#### Measurement Setup

**HITS**<sup>TM</sup>

Probe tips in contact with 300 mm µbump wafer

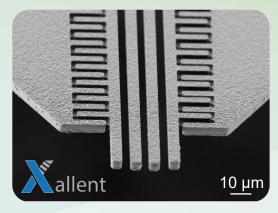

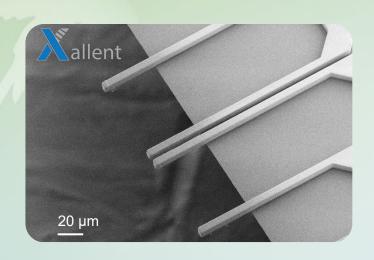

#### Fine Pitch Probe Specifications

| Parameter                      | Value         |

|--------------------------------|---------------|

| Number of tips                 | 4             |

| Arrangement                    | Inline        |

| Probe 1 & 2 spacing            | 65 μm         |

| Probe 2 & 3 spacing            | 5 μm          |

| Probe 3 & 4 spacing            | 65 μm         |

| Probe thickness                | 8 μm ±2 μm    |

| Probe-to-probe leakage current | ~500 pA @ 5 V |

| Current carrying capacity      | 100 mA        |

#### **Kelvin Resistance Measurements**

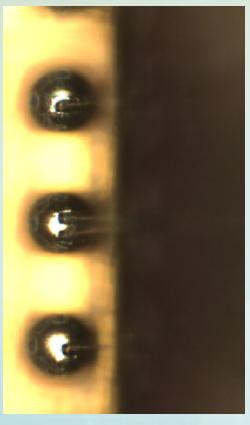

Virgin µbumps

Probes in contact with µbumps

Probed µbumps

#### **Kelvin Resistance Measurements**

- 75 dice on a 300 mm wafer were tested

- A single 3-µbump test structure was tested per die

- The median Kelvin resistance was 25 mΩ with minimum and maximum resistance values of 18.8 mΩ and 11.38 kΩ respectively

## **Challenges of Micro-bump Probing**

- Auto-focusing of µbumps

Leverage advanced algorithms for auto-focusing

- Accurate alignment between probe tips and µbumps

Utilize high precision stages and automation software

- Maintaining constant contact force

Utilize force feedback probes to continuously

monitor contact force during probing bad, CA, June 2 4, 2025

#### Summary

- Fine pitch probing is crucial for ensuring the reliability and performance of advanced packages, enabling the development of next-generation high performance computing (HPC) and high bandwidth memory (HBM) chips

- Our experiments demonstrate the effectiveness of our finepitch probing solution for accurate characterization of microbumping processes

- Reliable and repeatable measurements of Kelvin resistance, a key wafer acceptance test (WAT) parameter were achieved

## Acknowledgement

The authors thank MPI Corporation for providing a 300 mm semiautomatic wafer prober for the development of HITS<sup>TM</sup>, and special thanks to:

- Robert Carter

- Stojan Kanev

- Frank Fehrmann

Pardeep Kumar pardeep.kumar@xallent.com

https://xallent.com

#### References

- [1] M. Hutner, R. Sethuram, B. Vinnakota, D. Armstrong, and A. Copperhall, "Special session: Test challenges in a chiplet marketplace," in 2020 IEEE 38th VLSI Test Symposium (VTS), 2020, pp. 1–12.

- [2] F. M. Smits, "Measurement of sheet resistivities with the four-point probe," The Bell System Technical Journal, vol. 37, no. 3, pp. 711–718, 1958.

- [3] J. Ehrstein and C. Croarkin, "Standard reference materials: The certification of 100 mm diameter silicon resistivity SRMs 2541 through 2547 using dual-configuration four-point probe measurements," 1999 Edition.

- [4] M. Yamashita, T. Nishii, and H. Mizutani, "Resistivity measurement by dual-configuration four-probe method," Japanese Journal of Applied Physics, vol. 42, no. 2R, p. 695, Feb 2003. [Online]. Available: <a href="https://dx.doi.org/10.1143/JJAP.42.695">https://dx.doi.org/10.1143/JJAP.42.695</a>

- [5] N. Chandra, V. Sharma, G. Chung, and D. Schroder, "Four-point probe characterization of 4H silicon carbide," Solid-State Electronics, vol. 64, no. 1, pp. 73–77, 2011.

- [6] S. Thorsteinsson, F. Wang, D. H. Petersen, T. M. Hansen, D. Kjaer, R. Lin, J. Y. Kim, P. F. Nielsen, and O. Hansen, "Accurate microfour-point probe sheet resistance measurements on small samples," Review of Scientific Instruments, vol. 80, no. 5, p. 053902, May 2009.

- [7] P. F. Nielsen, D. H. Petersen, R. Lin, A. Jensen, H. H. Henrichsen, L. Gammelgaard, D. Kjar, and O. Hansen, "Microprobe metrology for direct sheet resistance and mobility characterization," in 2012 12th International Workshop on Junction Technology, 2012, pp. 100–105.

- [8] Keithley Instruments, Inc., "Resistivity Measurements Using the Model 2450 SourceMeter SMU Instrument and a Four-Point Collinear Probe," Application Note No. 3247. [Online]. Available: https://download.tek.com/document/Resistivity%20Mesrmnts%20using% 202450%20AppNote.pdf

- [9] J. Chan, "Four-Point Probe Manual," EECS 143 Microfabrication Technology, 1994. [Online]. Available: http://www-inst.eecs.berkeley.edu/\~ee143/fa10/lab/four\ point\ probe.pdf

- [10] ASTM International, "Standard test method for sheet resistance uniformity evaluation by in-line four-point probe with the dual configuration procedure," ASTM Designation: F1529-97, 1998. [Online]. Available: https://www.astm.org/f1529-97.html