# Introduction to Probe Cards

How They are Built & Tested

# PROBE CARDS & PROCESS COURTESY OF CERPROBE

## Design & Layout

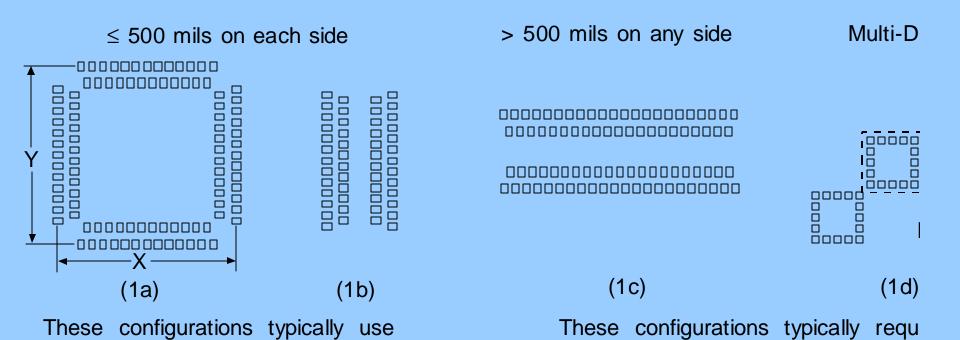

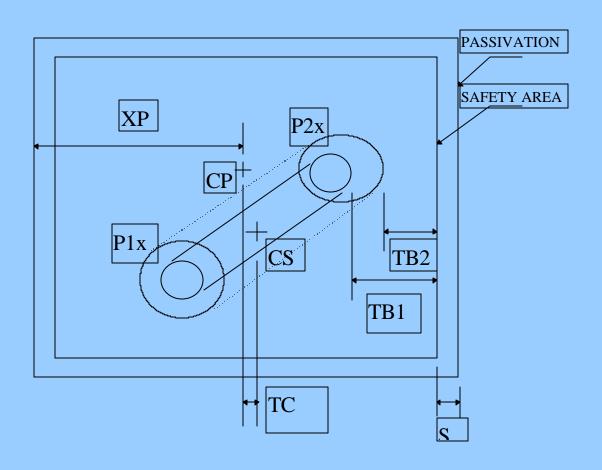

#### DIE PAD CONFIGURATIONS

semicustom or custom rings

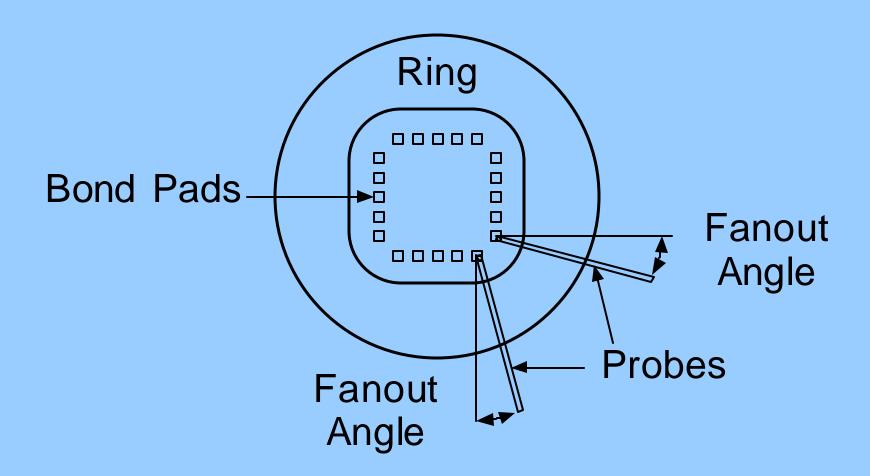

Figure 1: Die and Ring Configuration Examples

standard rings

Integrated Technology Corporation Copyright 1998

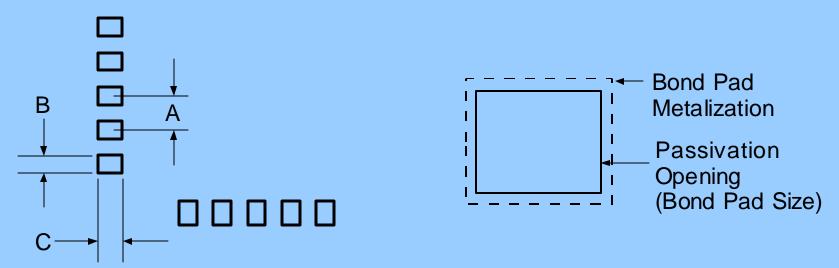

#### **BONDING PADS**

Figure 2: Bond Pad Pitch and Size

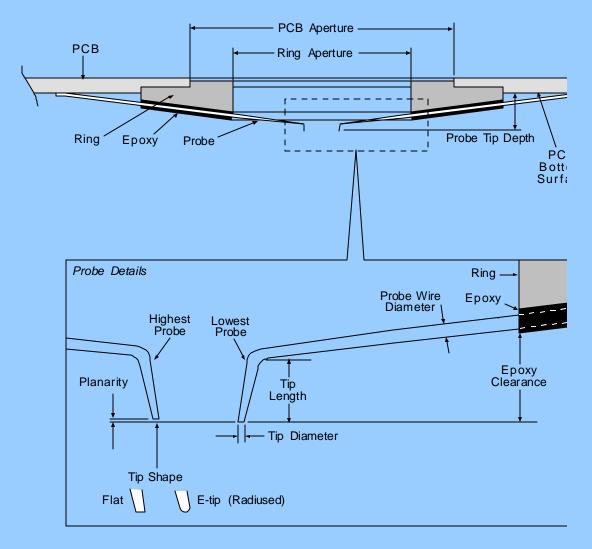

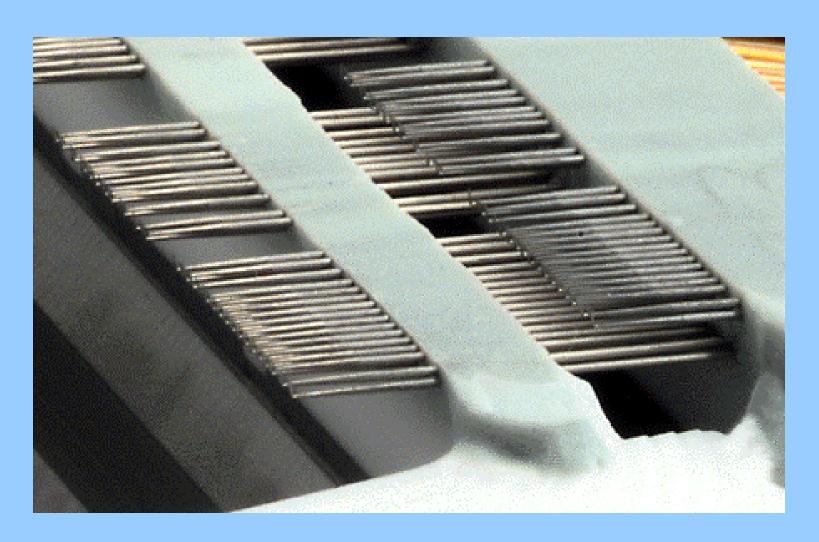

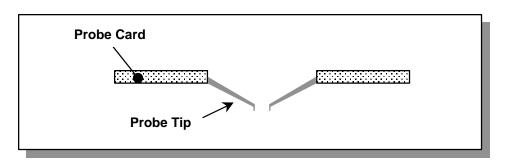

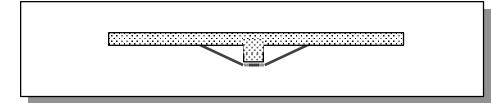

#### CROSS SECTION, CANTALEVER BEAM

Figure 3: PCB and Epoxy Ring Assembly

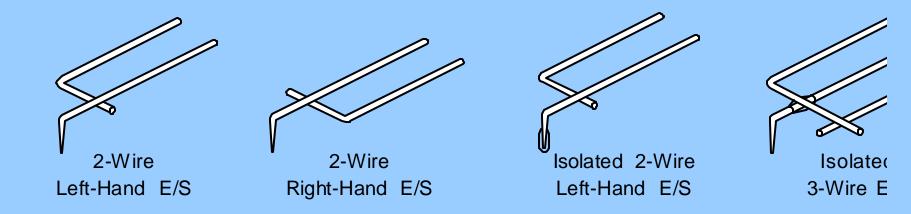

#### **EDGE SENSOR TYPES**

Figure 4: Edge Sensors

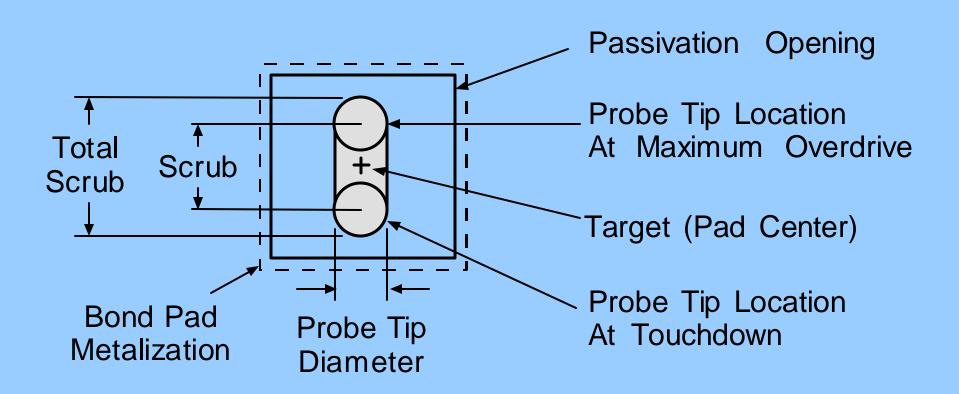

#### PROBE TO PAD POSITIONING

#### PROBE FANOUT ANGLE

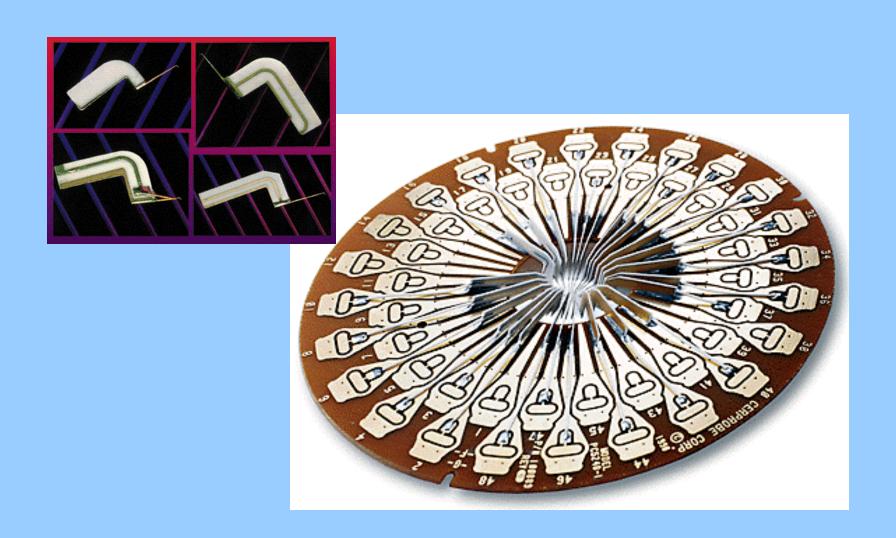

#### Wire Bend

#### Wire Bend - Replacement Probes

# Ring Build & Fixture

Integrated Technology Corporation Copyright 1998

## Ring Assembly

# Ring Assembly

Integrated Technology Corporation Copyright 1998

## Ring Removal

Integrated Technology Corporation Copyright 1998

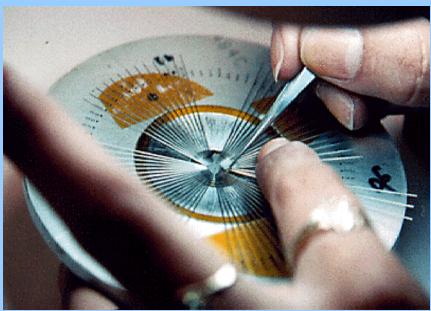

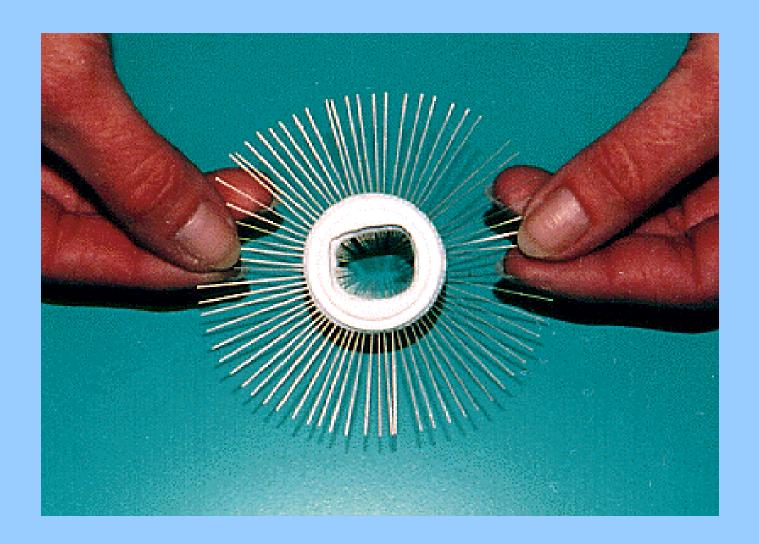

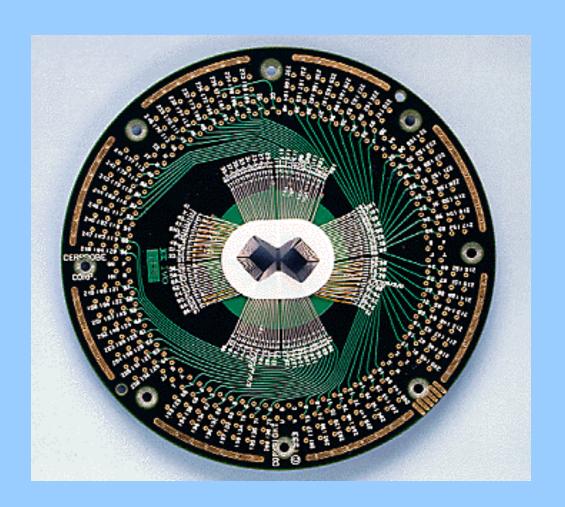

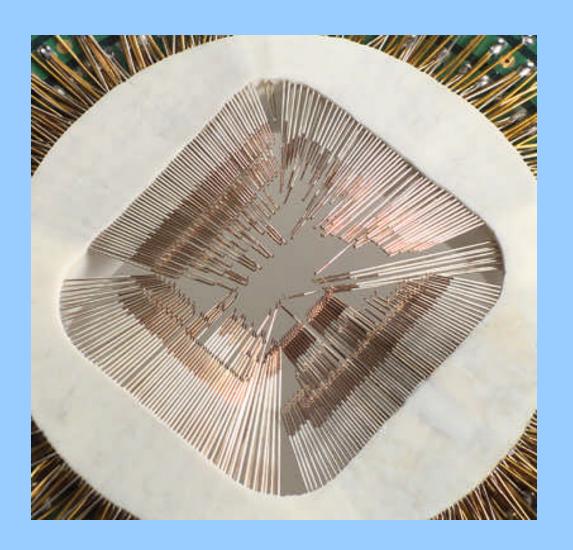

## COMPLETED PROBE RING

## **Completed Probe Ring**

## Multi Layer Ceramic Ring

## **Measuring Contact Force**

#### **PCB** Counterbore

# **Trimming**

## **Isolative Sleeving**

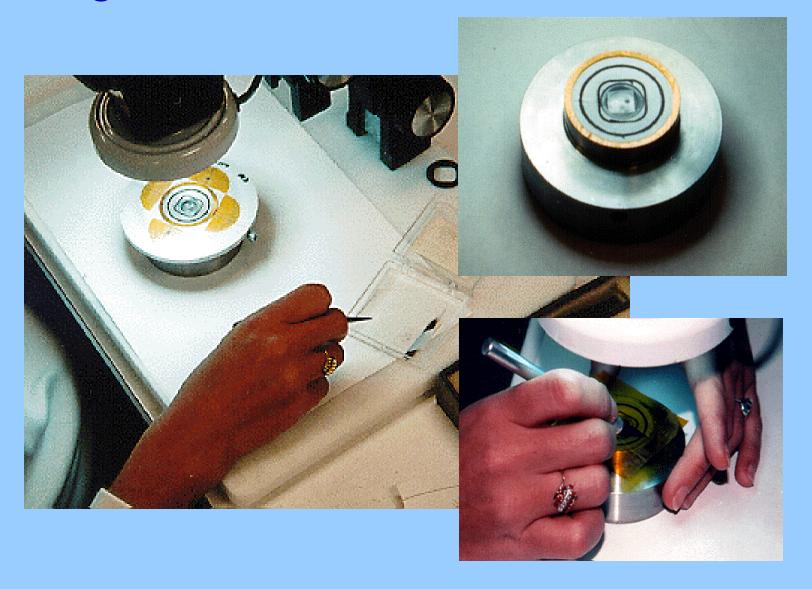

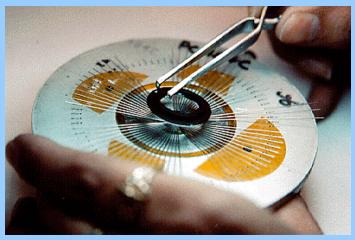

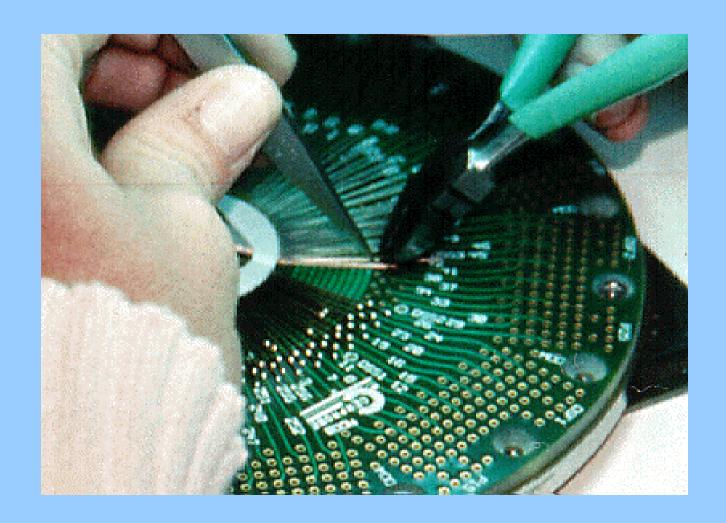

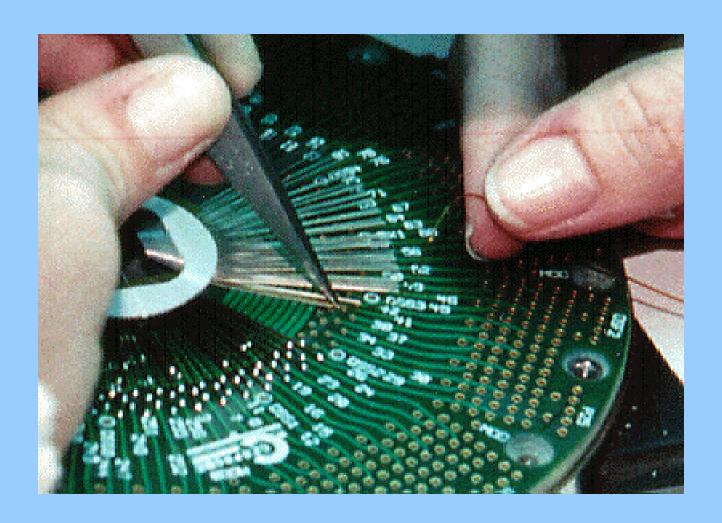

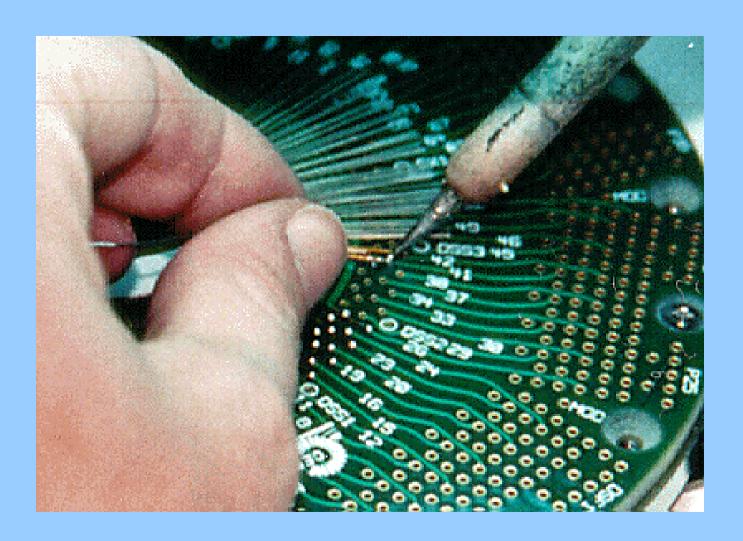

## **Probe Attachment**

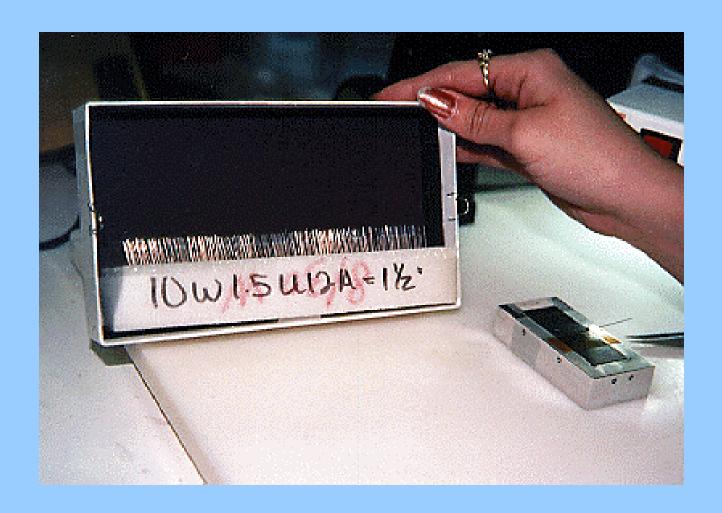

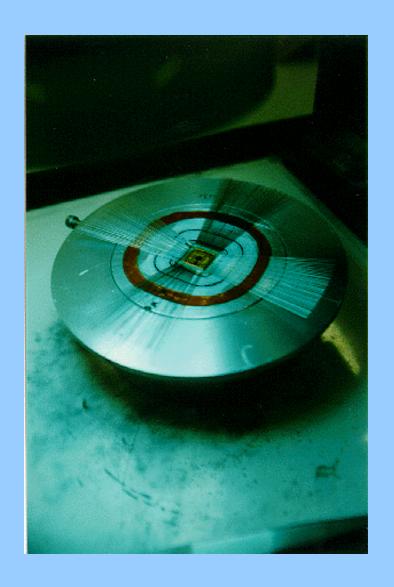

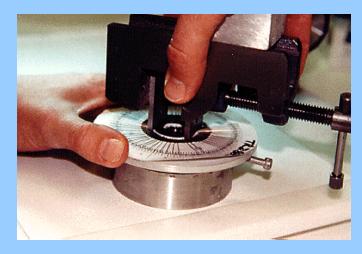

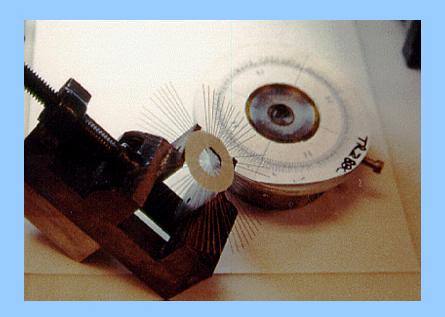

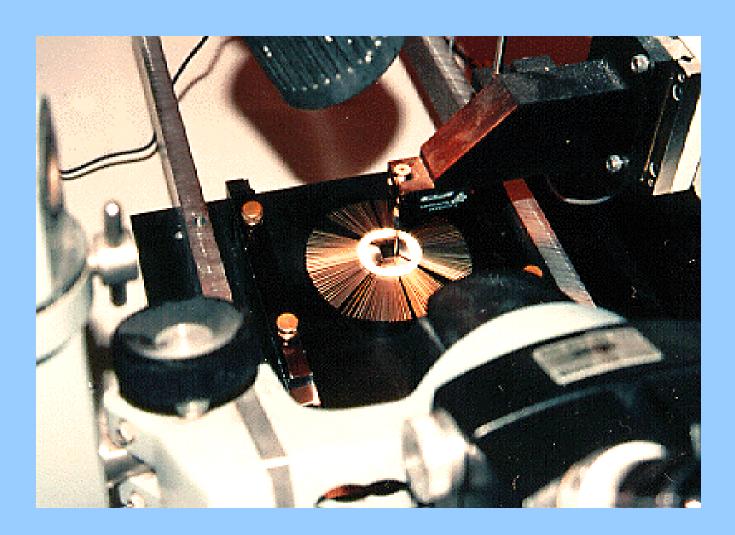

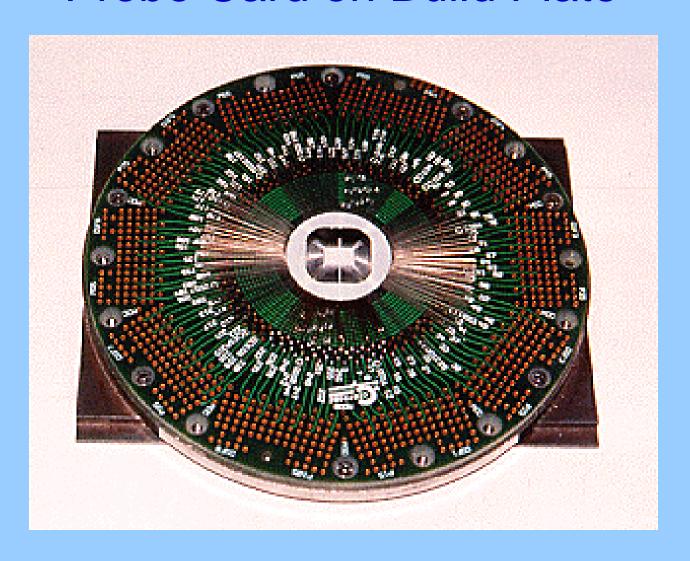

#### Probe Card on Build Plate

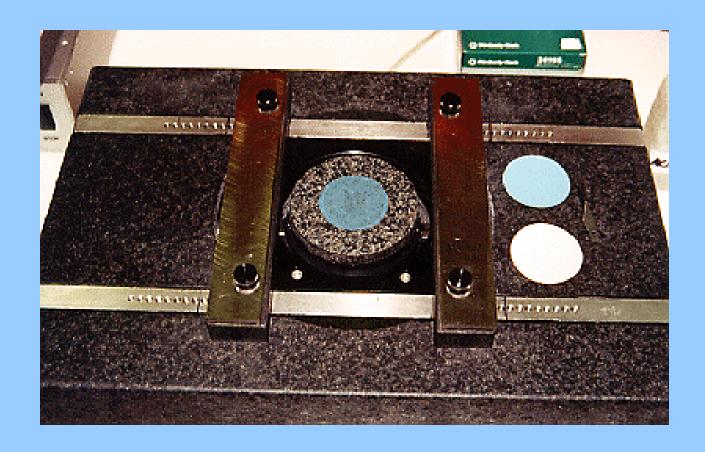

## **Probe Card Sanding Station**

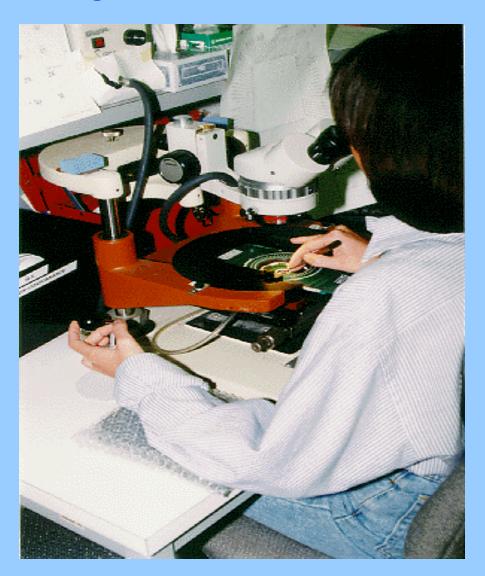

## Alignment to Wafer

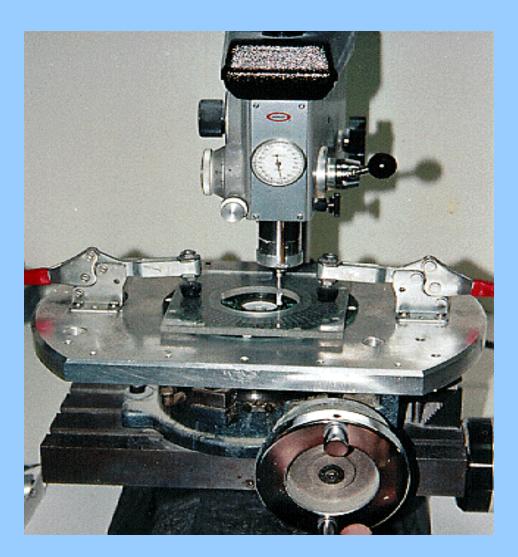

#### **Planarization**

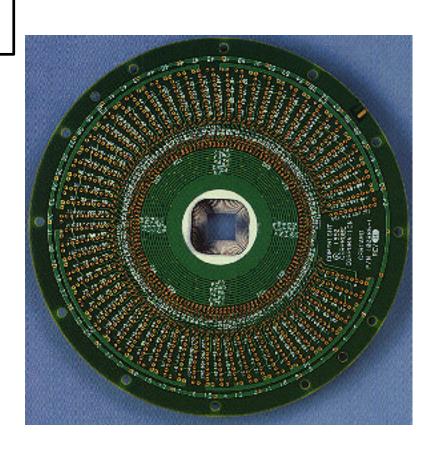

#### Finished Probe Card

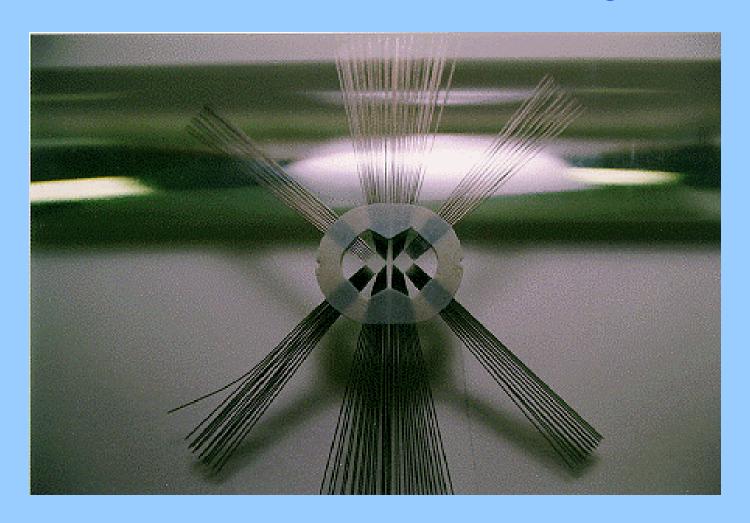

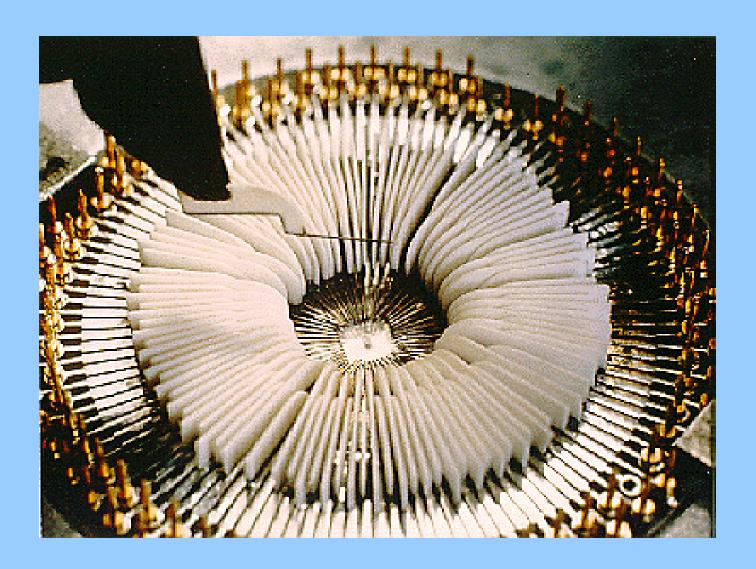

#### Multi-dut Probe Card

#### Multi-dut Probe Card

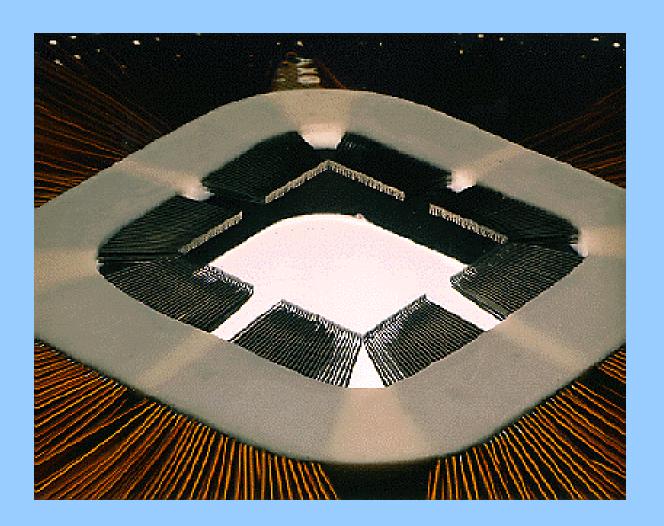

## Multiple Probe Layers

## Cantilever Area Array

# Area Array (top)

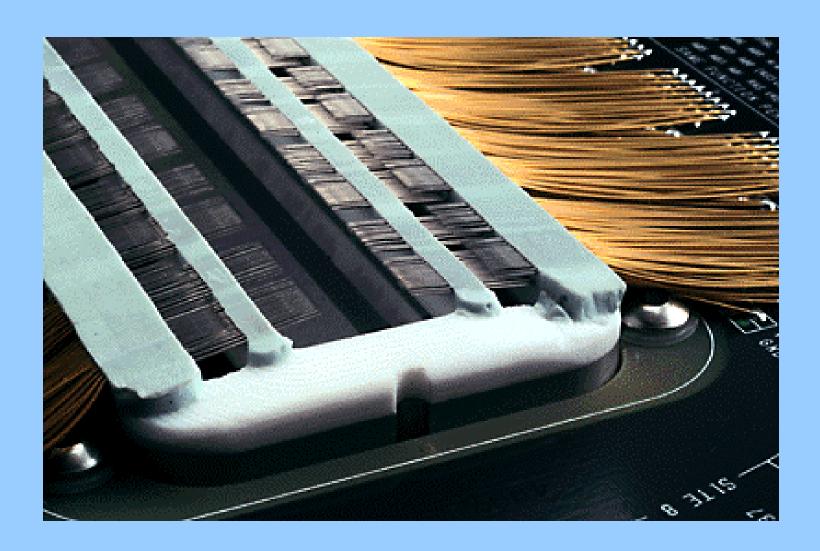

#### Ceramic Blade Probe Card

## Building a Blade Card

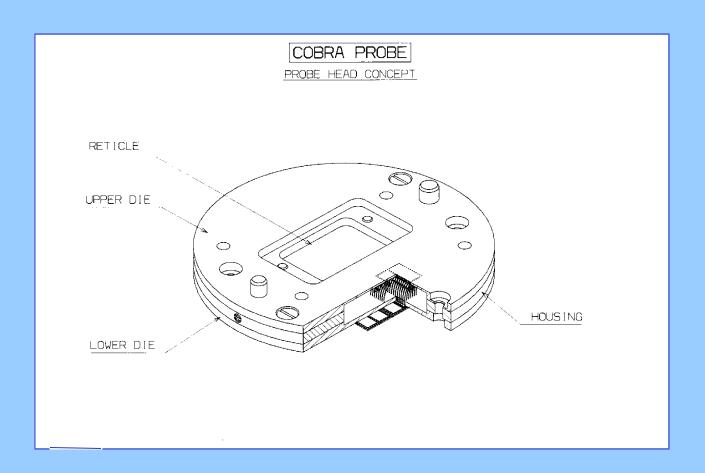

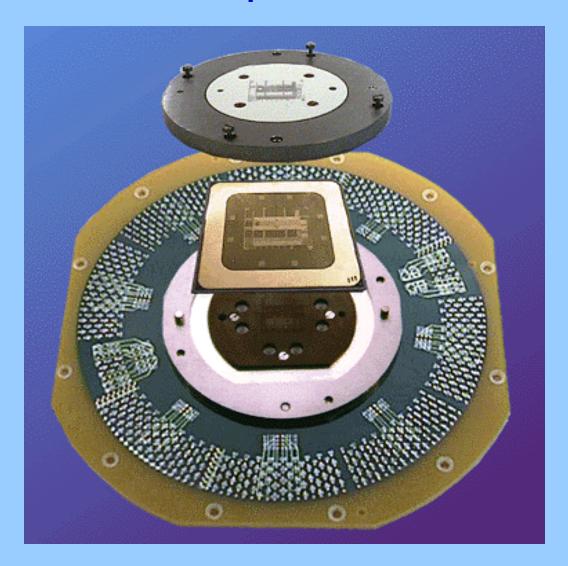

#### Cobra Probe Card

## Cobra probe card

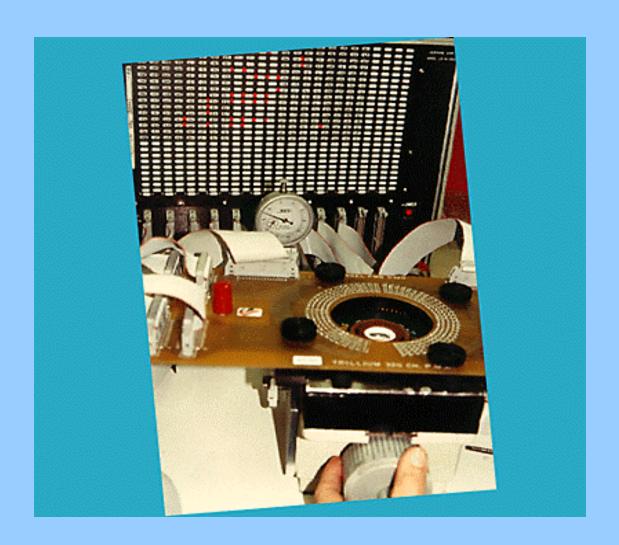

## PB3000 PROBE CARD ANALYZER

## PROBILT PB3000 MOTHERBOARD

#### PURPOSE OF TESTING

- SCREEN TO SPECIFICATION LIMITS

- ESTABLISH SPC

- ESTABLISH LIFETIME GUIDELINES

- ESTABLISH REPAIR CYCLES

- IDENTIFY POTENTIAL PROBLEMS

- IDENTIFY POTENTIAL IMPROVEMENTS

#### TEST PARAMETERS

ALIGNMENT TIP PLANARITY

DIAMETER

GRAM CONTACT

FORCE RESISTANCE

EXTERNAL EXTERNAL LEAKAGE

RESISTOR

**CURRENT**

CAPACITOR

## ALIGNMENT & TIP DIAMETER

- INSURE PAD CONTACT

- INSURE NO PASSIVATION DAMAGE

- ALLOW MAX. SET-UP TOLERANCE

- AGING MONITOR

- LIMIT FORCE/UNIT AREA

## **ALIGNMENT TO PAD**

#### TIP DIAMETER

- LIFETIME INDICATOR

- "TRUE POSITION" TOLERANCING

ELIMINATES NEED FOR MAXIMUM

LIMIT, EXCEPT FOR EOL

- FORCE / UNIT AREA

#### **PLANARIZATION**

- INSURE GOOD CONTACT

- LIMIT SCRUB LENGTH (BENDING BEAMS)

- CONTROL SCRUB DEPTH

- LIMIT TIP FORCE

#### CONTACT RESISTANCE

- LIMIT RMAX FOR DC PATHS

- LIMIT SWITCHING TIME CONSTANTS

- CHECK FOR CONTAMINATION

- CHECK PATH RESISTANCE

- CR (W) TYP 300 to 500 mOHMS

- CR (BeCu) TYP 100 TO 300 mOHMS

#### LEAKAGE CURRENT

- ADDS TO CIRCUIT LEAKAGE

- DETECTION OF SHORTS

- AFFECTS SWITCHING TIMES

- GENERAL CONTAMINATION DETECTION

#### CONTACT FORCE

- CONTACT RESISTANCE

- SCRUB DEPTH CONTROL

- FORCE PER UNIT AREA

- GENERAL QUALITY CONTROL

- AGING MONITOR

- PROBE GEOMETRY MONITOR

- PROBE RETENTION MONITOR

#### COMPONENTS

- VERIFY PRESENCE/ABSENCE

- VERIFY COMPONENT VALUE

- DETECT AGING

- DETECT OTHER CHANGES

## PROBER OVERDRIVE REFERENCE

- FIRST CONTACT

- EDGE SENSOR

- PROFILER

- VISUAL

## Wafer Probe

## **Equipment**

Prober

Test System

Interface

**Probe Card**

Wafer Handling

**Product**

Metalized Wafers

## "Probing": Checking for the Good & Bad

#### In-Process (Parametric Testing):

- When wafers are being built

- Checking for possible problems

#### At the End (Etest, Sorting):

- When wafers are done

- Etest checks test patterns

- Process Parameters

- Sort identifies good/bad parts

- Functional Test

- Parametric Test

- Clock Speed, Temperature, etc.

#### **Probe Cards**

#### Shapes

Square toRound

#### Sizes

- 4" to 16"

#### **Probe Tips**

VariousMetalurgy,Types andSizes

## Probe Tips

#### **Types**

- Cantilever

- Vertical

- Membrane

#### Size

-.8 to 4 mils

#### Quantity

- 10 to 2000

#### **Materials**

- Tungsten

- WR

- Paliney

## Wafer Contact Point

#### Chips may have Different Contact Points

Al pads

Au pads

Solder bumps

Tabs or Tape

Critical Parameters

Alignment

Contact Resistance

Pad Damage

## Probe Technology Selection

#### Dependent on Contact Point Technology

Cantilever Beam Probes

Peripheral Pads

Al or Au Pads

Solder Bumps (Limited)

Tabs or Tape

Vertical (Cobra)

Array Patterns

Solder Bumps (Flat Tips)

Al or Au Pads (Pointed Tips)

## Pretty Close !!!

## Q: How close do we need to put the probe in the pad?

A: Within +/- 10 microns in x and y directions

Q: How small is a micron?

A: If an inch was football field, a micron would be a blade of grass.

## Types of Testers

#### Configured for Specific Technology

Memory, uProcessor, Linear, etc.

Clock Speeds >100 MHz

Rise Times <250 pS

Parallel Testing of Memory Devices (8-32 Chips)

Every Interface is Different - NO STANDARDS!

Test Head Configurations

Direct Dock

**Cabled**

## Test Head Docking

#### Cabled Interface

Drive/Sense Electronics in Tester Mainframe Cables (COAX or Shielded Linear) to pogos Test Interface is only pogo pins to Probe Card Slower (Clock Rate) than Direct Docking

#### **Direct Docking**

Drive/Sense Electronics in Test Head

Test Head sits Directly on the Interface

Soft or Hard Docking - Force/Weight

Highest Speeds Available

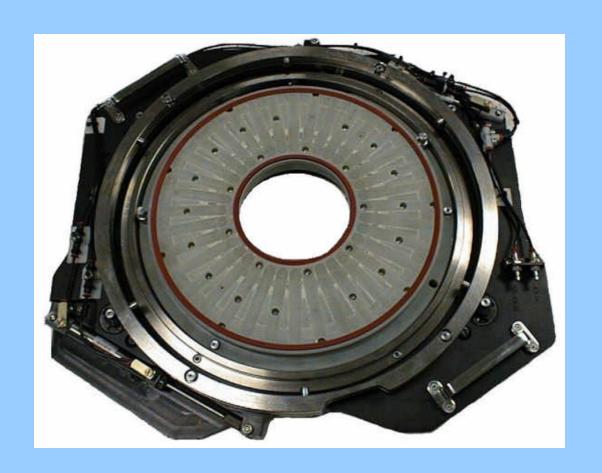

# Direct Docking to Tester (Courtesy Cerprobe Corporation)

Michael George (408) 727-6500 x6244 electroglas

## Wafer Handling

Loading may be Manual or Automatic Manual Loading

Use Tweezer or Vacuum Wand

Possible Damage or Breakage

Cleanliness (Particles, Contamination)

Very Slow

**Automatic Loading**

Cassette Wafer Holders

One or Multiple Cassettes

Wafer Automatically Transferred to Chuck

Faster, Cleaner, Safer

electroglas

## Wafer Alignment (1)

#### Align Probe Tips to Pads

X,Y Position

Theta (Rotation)

Overdrive (Z Axis)

#### Manual Alignment

Rotate Chuck/Wafer to be on Prober X,Y Axes

Rotate Probe Card (if required)

Position Probe Tips to Touch Down on Pads

Set Overdrive to 1.0 to 4.0 mils (Type Dependent)

## Wafer Alignment (2)

#### Automatic Alignment

Prober Aligns Wafer Using Targets

Probe Card Theta not Usually Required

Wafer Loader Aligns Wafer from Cassette

Upward Looking Camera to see Probe Tips

Downward Looking Camera to see Pads

Can Readjust Alignment During Probing