IEEE SW Test Workshop

Semiconductor Wafer Test Workshop

Haydee Barajas and Al Wegleitner

Texas Instruments

# Low Yield Response (LYR) in High Volume Production

June 3-6, 2007 San Diego, CA USA

## Agenda

- Background

- Problem Statement

- Objective

- Methodology

- Results

- Conclusions

- Acknowledgments

## Background

Probe operations have to battle with yield related Issues on a daily basis – how do you minimize lost time?

## **Problem Statement**

How do you effectively diagnose, evaluate and recover from yield related problems?

- No standard troubleshooting procedures –replace boards, pc, - shotgun approach

- Communication gaps/delays between different parties involved (Mfg Engineering Business)

- No problem traceability to close process and system gaps.

## **Objective**

To provide a process flow that allows for effective evaluation and troubleshooting of yield related problems driving to root cause solutions. Low Yield Response or LYR methodology creation provides these decisions.

## Methodology

DATA CHECK = Troubleshooting Trigger

#### **LYR General Procedure**:

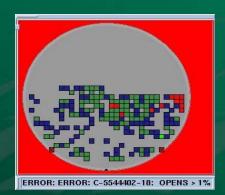

A data check stops the testers to evaluate potential test issues. This triggers a LYR which uses a variable process elimination to find root cause which includes the escalation procedure between the different groups involved: mfg, EE, PE, and Apps.

June 3-6, 2007

**IEEE SW Test Workshop**

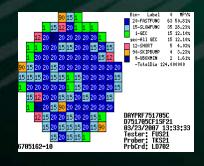

## **Methodology** Yield Data Hierarchy

Bin Sum

T2T

**Alerts**

Calculated after 2 wafers probed on 2 testers. Monitors yield deltas between testers.

#### S2S Alerts

Calculation done at wafer end. Monitors yield deltas between probe card sites.

#### **Data Checks**

Monitor Bin Counts and Percentages as wafer is probing

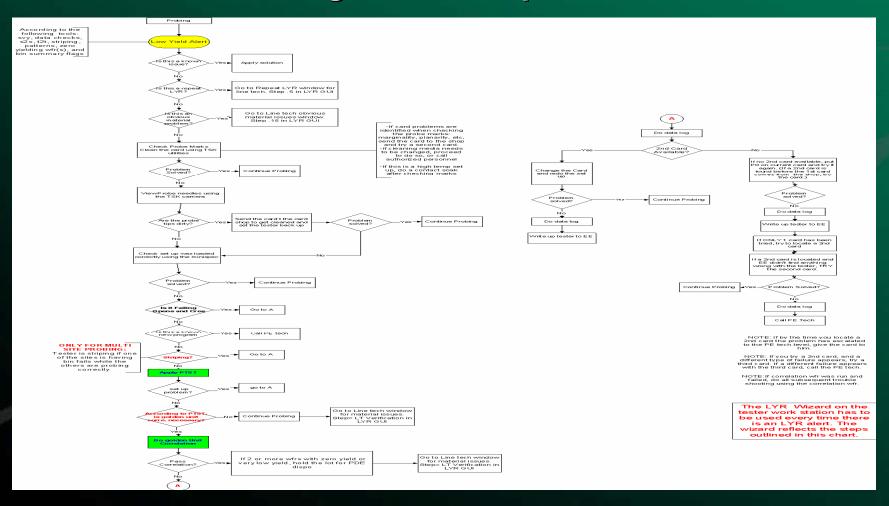

## Methodology LYR process Flow

- Each group involved has an automated troubleshooting flow. The different flows interact with each other.

- There is an LYR GUI access from the tester that guides the user through the troubleshooting decision process and escalations.

## Methodology

### **Mfg Flow Example**

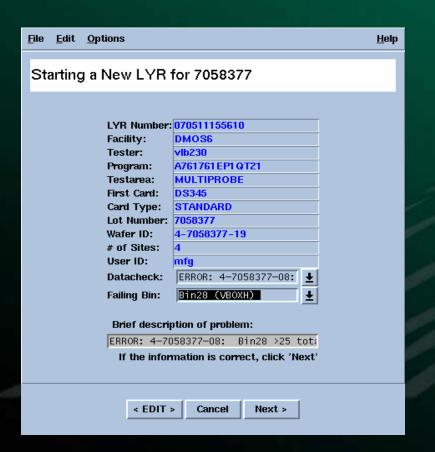

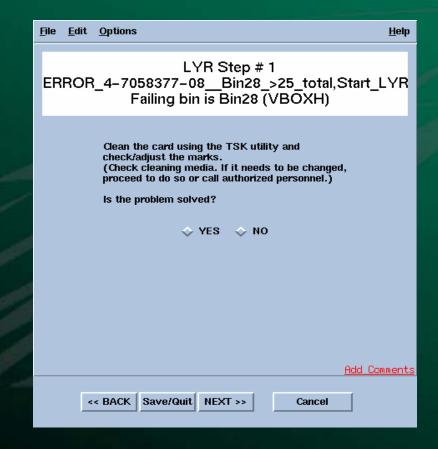

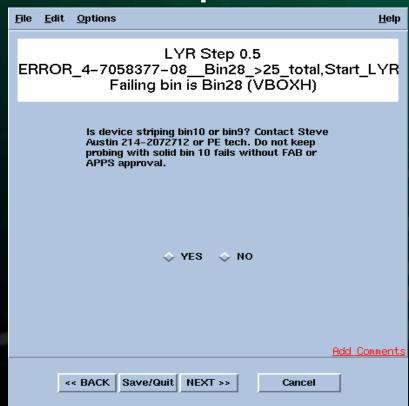

# Methodology The LYR GUI

# Methodology The Known Issues Data Base

- This is used in the LYR when we do not want to go through the normal troubleshooting process, some examples are:

- Lot(s) affected by a fab excursion.

- Known program issues, awaiting fix.

- Engineer wants to be called to work on the tool for a specific problem.

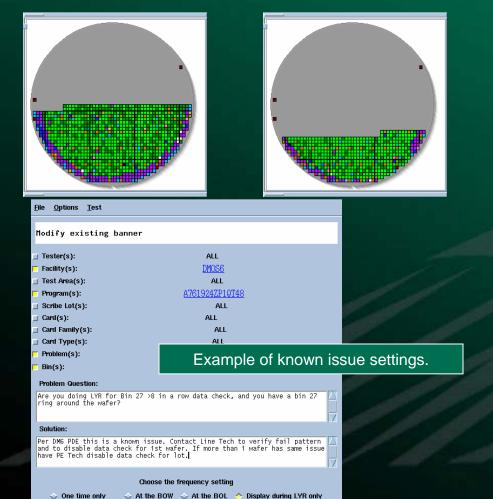

# Methodology The Known Issues Data Base

#### **Example**

Known issues can be entered using different combinations: lots, probe cards, programs, testers, log points, etc.

# **Methodology Known Issue Example**

#### **Automated Banner Response**

Problem:

Are you doing LYR for Bin 27 >8 in a row data check, and you have a bin 27 ring around the wafer?

Example of known issue pop-up window.

Solution:

Per DM6 PDE this is a known issue. Contact Line Tech to verify fail pattern and to disable data check for 1st wafer. If more than 1 wafer has same issue have PE Tech disable data check for lot.

Close

## Methodology

### **LYR Verification Process**

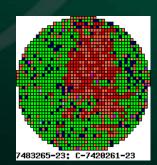

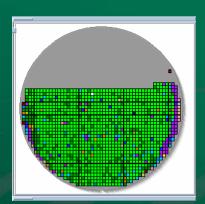

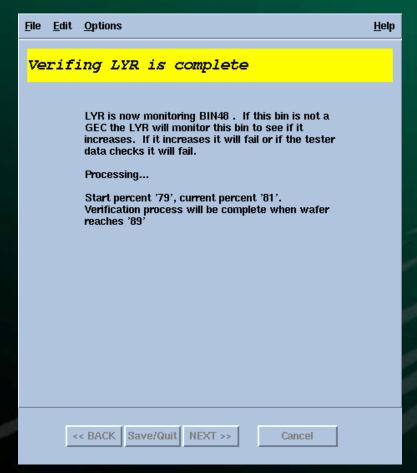

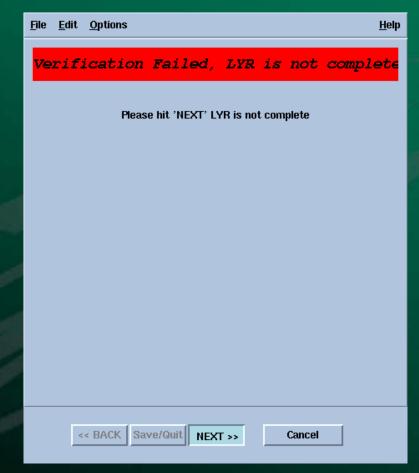

After Mfg, EE or PE finish the troubleshooting process. The LYR performs an automated check to verify that the yield issue has been resolved. If the failing bin percentage increases or there are further data checks, then it reopens to continue with the next troubleshooting steps.

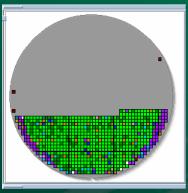

# Methodology LYR Verification Process

## Methodology

### LYR Lot History Documentation

SMS/370 LOT/MACHINE COMMENT LIST SMW2ØDE3 SDLØ1 REQUEST: (LST.DEL) LOGPT: 9450 FACILITY: DMOS6 OPN: 5140903 LOT: SEL LP OPN 9450 8760 DATE: WED SEP 7 090050 CDT 2005 LYR UERSION:2.0 LYR NUMBER: 050907090012 TESTER NAME: ULB235 NAME: A 751501 EP1ST15 NUMBER:5140903 FIRST WAFER:4-5140903-14 USER NAME: OPERATOR INITIAL DESCRIPTION: FAILING HIGH BIN 46 AND BIN 13... NEXT TRAN DEST =SMWA@@15 PRESS <ENTER> KEY FOR CONTINUATION 05/09/07 15:59:32 F6:RETURN TO MENU F10:M13 MACH STATUS F11:M17 START WORK F12:M22 MISTI MENU TCW 735 03 12 A ADLIMA

# Methodology LYR Documentation- Search Utility

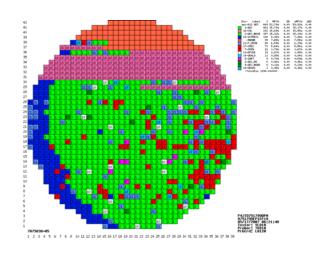

# LYR troubleshooting Example

UserID=a0869436 - Operator Shift=D Date=Wed May 16 23:25:24 CDT 2007 LYR\_Version=3.0 LYR Number=070516232421 Tester\_Name=vlb10 Facility=DMOS6 Testarea=MULTIPROBE Program\_Name=A751799EP1DT19 Lot Number=7075838 Chuck\_Temp=30 First\_Wafer=4-7075838-05 User\_Name=Operator Initial\_Description=stripping\_bin\_16\_on\_site\_1 Automatic\_Description=OTHER First\_Card=LB120 Card\_Type=STANDARD Number\_Of\_Sites=2 Status=EEcomplete Is\_This\_Flash\_Material=NO Was\_The\_LYR\_Filled\_Out\_Correctly=New\_LYR MFG Obvious Material Problem=NO Did\_Cleaning\_Card\_Checking\_Marks\_Fixed\_Problem=NO Did\_Probe\_Tips\_Look\_Dirty=NO Did\_Matching\_The\_Setup\_To\_The\_Minispec\_Fixed\_Problem=NO Is\_Tester\_Probing\_Opens\_Or\_CRES=NO Is\_This\_a\_New\_Program=NO Number\_Of\_Lots\_Under\_Program=64 Is\_Tester\_Striping=YES Is\_There\_A\_Second\_Card\_Available=YES Did\_Second\_Card\_Fix\_Problem=NO Second\_Card\_Name=LB112 Was\_Second\_Card\_Failing\_The\_Same\_Way\_As\_The\_First=YES Escalated\_To=EE,Two\_Cards\_Failed\_The\_Same\_Way UserID=a0215297 - EE

Verified\_Failing\_Same\_On\_Both\_Attempts=YES What\_ls\_The\_Tester\_Failing=solid\_bin\_\_\_16\_fallout\_after\_having\_run\_good What\_Site\_Is\_Failing=single\_site Did\_Probe\_Card\_Have\_History\_Failing\_The\_Same\_Fail=NO Any\_Problems\_Found\_During\_Visual\_Check=NO ls\_There\_Any\_Tester\_Trends=NO Verified\_Tester\_Is\_Failing\_Opens\_Or\_Cres=NO Are\_Power\_Supplies\_OK=NO Are\_Power\_Supplies\_OK\_Comment=-86\_v\_psa\_was\_reading\_out\_of\_tolerance\_at\_1.8v\_adjsuted\_to\_.9v\_ Pwr\_Supplies\_Failed=-86v\_reading\_1.8v\_over\_tolerance..adjusted\_to\_.9v\_well\_withing\_tolerance^ Did\_Diags\_Pass=NO Did\_Diags\_Pass\_Comment=failed\_sys32io,sys32ioplus\_for\_quad1\_pincrd\_5\_ Diags\_Failed=replaced\_32io++\_in\_slot5\_with\_new\_and\_now\_passes\_failed\_diags..recald\_system\_also\_failed\_to UserID=x0039937 - EE Redo\_Setup\_Is\_Problem\_Fixed=YES Solution Found=Diags Failed

Is\_This\_Problem\_A\_Known\_Issue\_EE=NO

Two Cards Used=YES

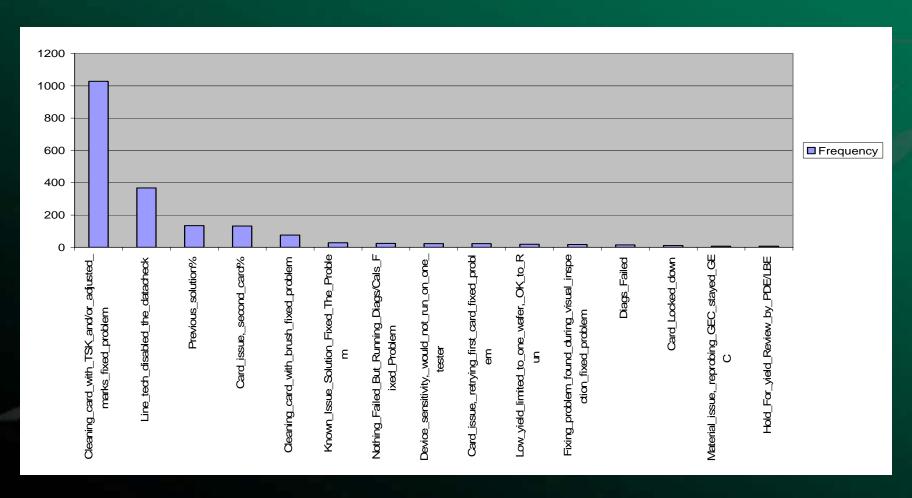

### Results

### **Using LYR Solutions to Drive Process Changes**

## Results

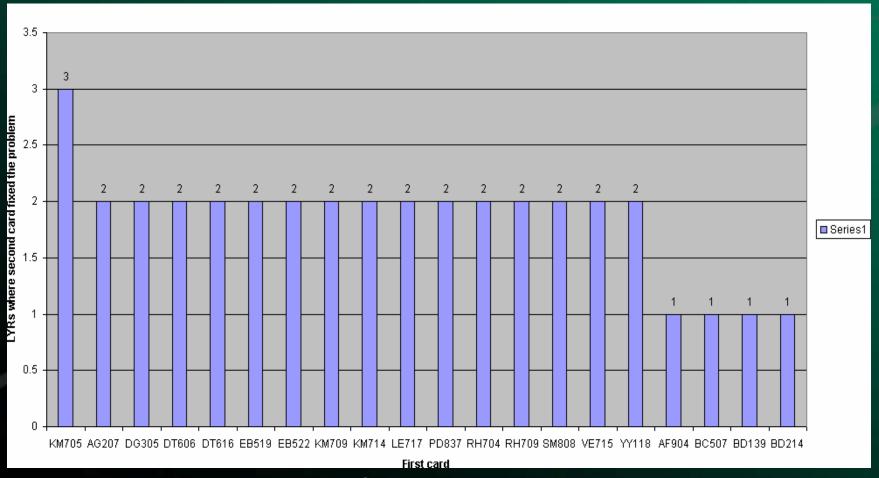

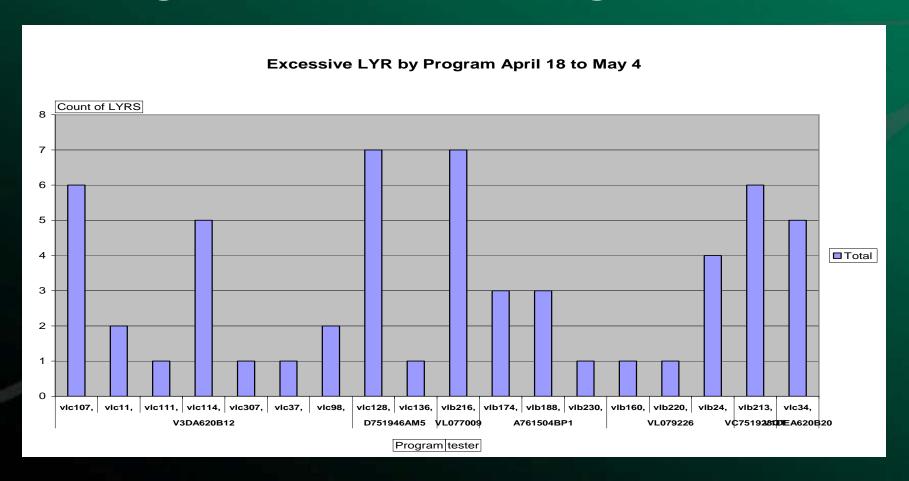

### **Using LYR to Identify Problematic Cards**

### Results

### Using LYR to Resolve Program Issues

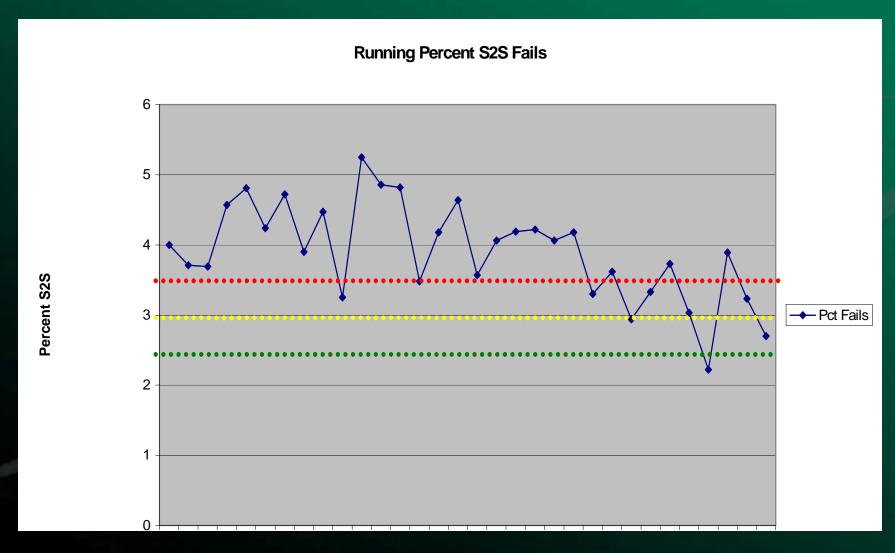

## Site to Site Results

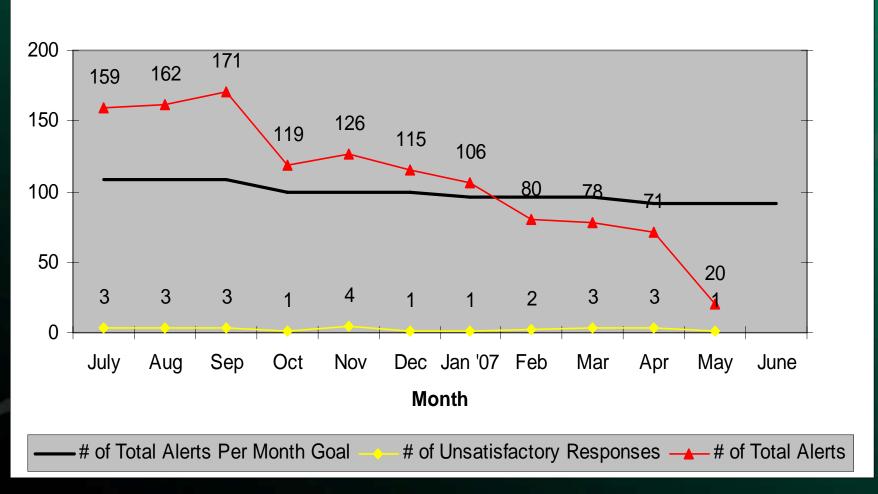

### **Tester to Tester Results**

#### EBT T2T Monthly Alerts & Responses 3Q 06 - 2007 YTD

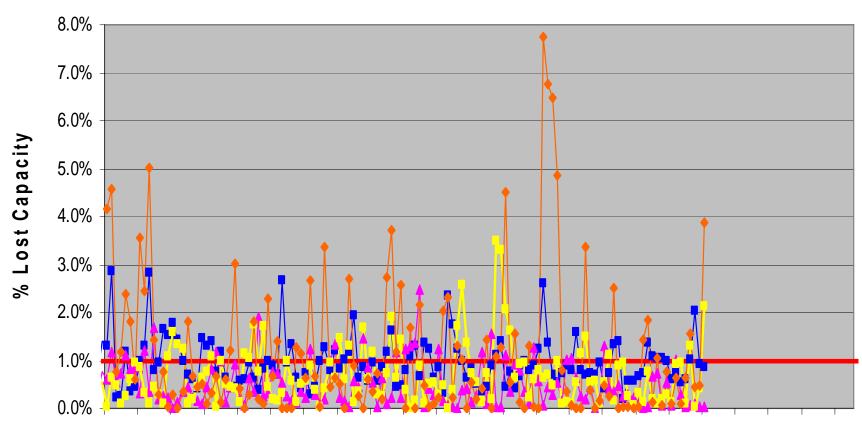

## Retest Results

### Conclusions

- The Low Yield Response provides a standardized process to troubleshoot yield related issues that deals with the interaction between the different parties involved.

- LYR analysis results provide the basis to drive process/system changes that help the factory run better.

## Acknowledgments

- Thomas Vaughan

- Francisco Tort

- Gary Grayson

- Shelbron Barnes

- Bruce Murray

- Trey Barton

## **Thanks For Listening**

Questions?

Contact a-wegleitner@ti.com