# IEEE SW Test Workshop Semiconductor Wafer Test Workshop

John Hite

Texas Instruments

# Standardizing WSP-Wafer Socket Pogo Pin-Probe Cards

June 6 to 9, 2010 San Diego, CA USA

# Agenda

- Introduction

- WLCSP and WSP Probing

- WSP Standardization

- Standard Alignment / Mounting Ring

- FEATURES

- PROCEDURES

- Summary

- Next Steps

- Acknowledgements

## Introduction

- Recent growth of WLCSP-Wafer Level Chip Size Package probing created an opportunity for probe card hardware standardization on new WSP probe card technology.

- A majority of WSP socket vendors did not have established design parameters for probe heads and probe cards.

- As a result, standard probe head and assembly hardware were developed to drive 2 main objectives:

- Provide TI Business Units and Test Floors a competitive WSP probe technology based on multiple-supplier sources, rather than custom solutions.

- Provide an opportunity to Probe Card suppliers to enter and compete directly in terms of their probe head technology and manufacturing strengths.

### **WLCSP** and **WSP**

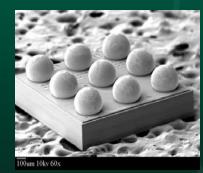

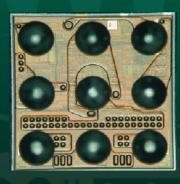

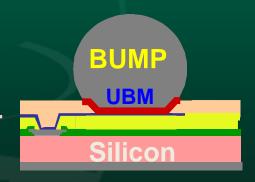

Texas Instruments has been successfully integrating WSP-Wafer Socket Probe technology; primarily for WLCSP-Wafer Level Chip "Size" Packages using solder bump interconnections into TI and Sub-Con Test Floors.

400 µm pitch

RDL

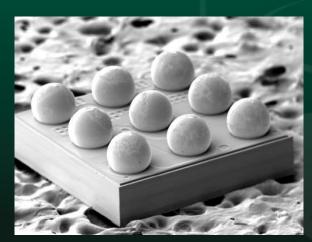

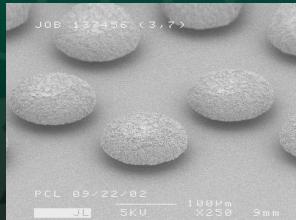

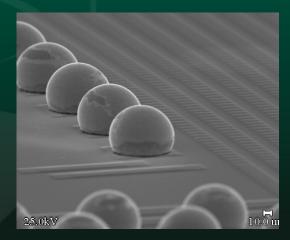

WSP is categorized into (4) major wafer-level probing applications, from 400 to 150µm pitch on 250 to 75µm diameter solder bumps and Al pads.

- RF-Radio Frequency

- NRF-Non RF

- NRF-Non RF w/ Kelvin

- FC-Flip Chip

# **WLCSP Probing Technologies**

#### **Cantilever**

### **Vertical Probe Card**

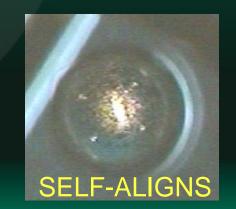

## **WSP Major Attributes**

- Self-Aligning 4 pts

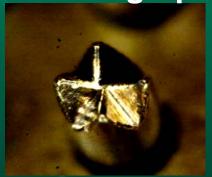

- Bump Damage < VPC</li>

- No Reflow Required

- Hand-Test Capable

- Lifetime > 3 M TDs

- PC Analyzer Not Req'd.

- Single-pin repairable

- CRes < VPC</li>

- Cost ~85% of VPC

- Cleaning < VPC</li>

- Kelvin Capable 400um

- Deflection > VPC

- Force < VPC</li>

- Interchangeable

## **Problem Statement**

- No consistency across existing designs, sizes or shapes; Each requires a <u>custom</u> design.

- Inability to exchange heads from one vendor to another or transfer to another PCB design.

## **WSP Standardization Attributes**

- INTERCHANGEABILITY: Incorporates precise alignment features and assembly hardware enabling both WSP Probe Head exchanges and overall hardware reusability.

- REDUCES PROBE CARD COSTS: A new PCB design is not required when a WSP probe head is changed. WSP Probe Heads from multiple vendors can be utilized on the same card allowing for multiple sourcing.

- SIMPLIFIES PROBE CARD DESIGN: Design of the probe card is simplified by having a single layout based on the size of the array and the X, Y coordinates of each probed pad. <u>The</u> <u>layout allows the probe head to be vendor manufacturingindependent.</u>

# **Collaborative Approach**

- Reviewed conventional C-VPC and prototype WSP probe heads designs to develop a standard PCB to WSP probe head interconnection across various WLCSP array patterns, sizes, multi-sites, component space and PCB footprint requirements.

- Collaborated with TI Probe Technologists, Business Unit Test Engineers, Test Floor Operations and WSP Socket Vendors to arrive at a standard that all could support.

## **WSP Standardization Features**

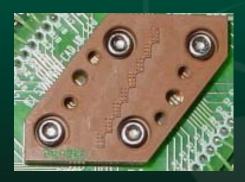

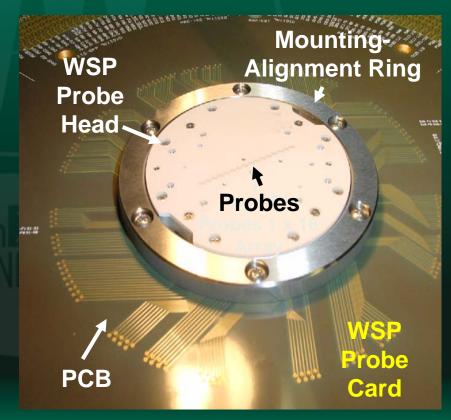

#### WSP Probe Head

- Outline / Orientation

- Probe head to probe card alignment

- Component Cavities

- Pogo Length

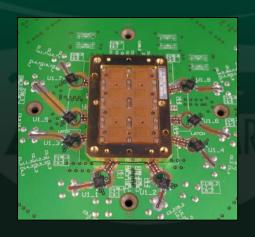

#### PCB Layout

- Multisite Layout

- Pogo Pad size

- Mounting holes

- Alignment holes

- Pad/Pin Alignment

- Keep-Out Areas

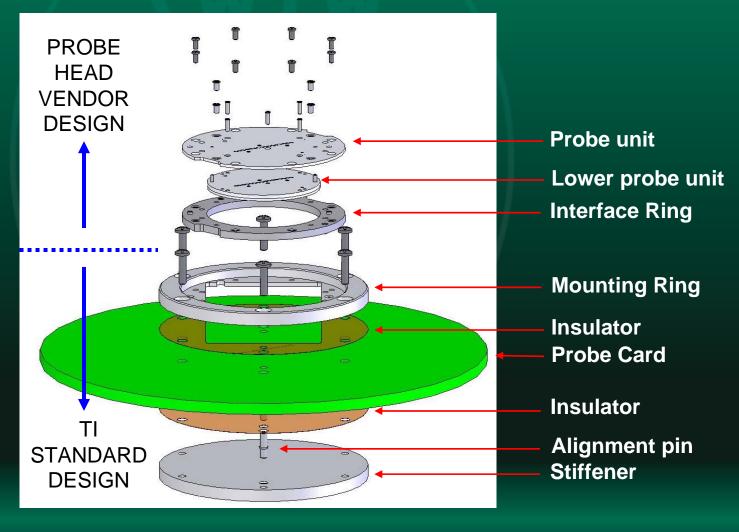

## **Standard Design Basis**

- WSP standard was based on current C-VPC Heads

- Outer mounting ring with inner probe head

- Well understood on TI test floors and w/supplier base

- Three (3) mounting ring sizes selected to accommodate most WLCSP footprints, while allowing for component space and test-cell requirements.

- Both mechanical and visual (ocular) alignment features were used based upon the pitch of the device.

## **WSP Mounting Ring Sizes**

- 3.2" Standard

- Maximum Array Sizes up to 42mm x 42mm

- 2.25" Standard

- Maximum Array Sizes up to 28mm x 28mm

- 1.25" Standard

- Maximum Array Sizes up to 17mm x 17mm

NOTE: A STANDARD STIFFENER IS ALSO PART OF THE HARDWARE CONFIGURATION ACROSS EACH OF THESE MOUNTING RINGS.

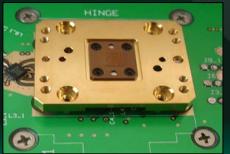

### **WSP Standard Mounting / Alignment Features**

3.2" Standard

Mounting Ledge for the Probe Head

(2) Holes for Alignment Pins for Mounting Ring (thru)

> Hole for Alignment Pin for Probe Head (thru)

(6) Screw Holes for Mounting Ring-(tap)

Pin Array Space

$\bigcirc$

0

0

(8) Screw Holes for Probe Head (tap)

Hole for Alignment Pin for Probe Head (slotted)

(4) Screw Holes for Test Lid Attachment (thru)

0

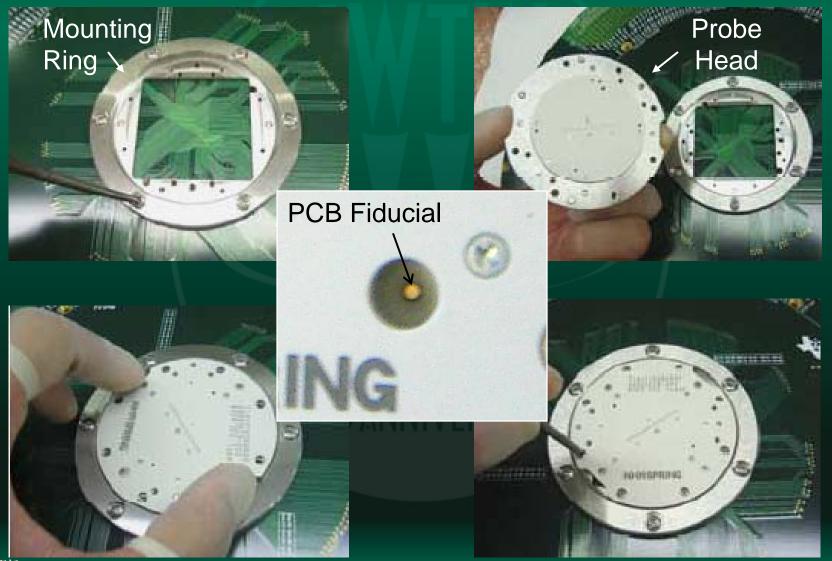

# WSP Probe Head to Mounting / Alignment Ring Exploded View

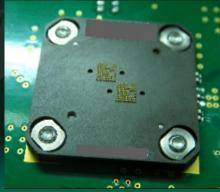

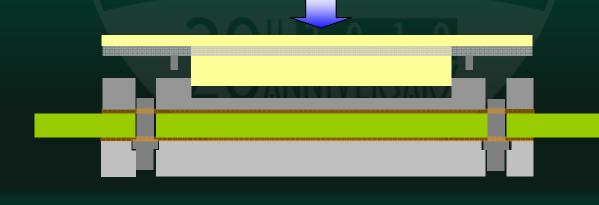

# Mechanical Standard Alignment when pitch is > 400um.

- Mounting ring pinned to PCB

- Probe head pinned to mounting ring

- Relies on pin-to-hole tolerances

- No specialized assembly

- Attach and go

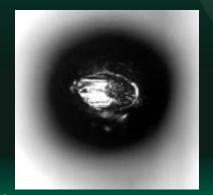

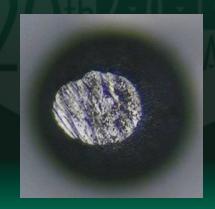

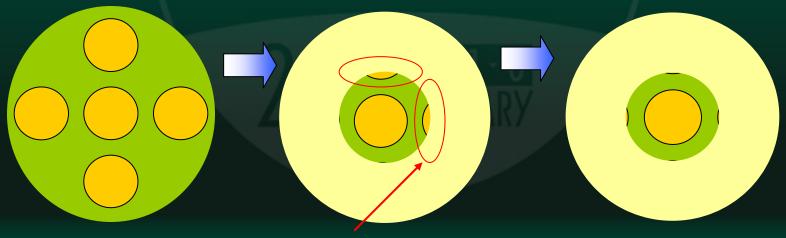

# Visual "Ocular" Standard Alignment when pitch is ≤ 300um.

- PCB uses fiducials

- Visual site holes in probe head

- Requires trained assembler

- Once procedure is completed, both the probe head and mounting ring is aligned to the PCB pad footprint.

- Any probe head for the same device can be exchanged with no further adjustment to the mounting required.

**5 Fiducial Pads on PCB**

**Looking through Probe Head Site Hole**

**Probe Head + Mounting ring misaligned**

**Both Aligned to PCB**

## **WSP Mounting / Alignment Ring Assembly**

## **SUMMARY**

Standardization has enabled TI to better integrate WSP probe card technology and multiple probe head suppliers on to TI test floors.

As a result, standardization of mounting/alignment and assembly hardware has improved WSP Probe Card COO-cost of ownership in terms of:

- PCB Single Design (facilitated re-orders)

- Probe Head Cost (multi-source competition)

- Test Floor Operations (interchangeability)

#### **NEXT STEPS**

Standardization is expected to be further deployed across more device applications requiring wafer-level probing of both Bump and Pad test point features, not only for WSP, but also for conventional and advanced probe head technologies.

WLCSP 400um Pitch, 250um Dia. Spherical Bump

FLIP CHIP 150um Pitch, 130um Dia. Mushroom Bump

FLIP CHIP 150um Pitch, 75 um Dia. Spherical Bump

### **ACKNOWLEDGEMENTS**

Norman Armendariz

James Tong

John Wolfe

Rich Lewis

Minette Ohmart

Michelle Gephart\*

Mike Korson