# Cu-Pillar Bump Probing: Utilizing a 50µm Pitch Fine Pitch Vertical Probe Card Technology

Senthil Theppakuttai, Ph.D.

**SV Probe**

**Todd Tsao**

**ASE Global**

IEEE SW Test Workshop

Semiconductor Wafer Test Workshop

June 10 - 13, 2012 | San Diego, California

#### **Outline**

- Introduction to Fine Pitch Copper Pillar Bumps

- Testing/Probing Requirements

- Test Vehicle Design

- Probe Card Challenges

- Test Data

- Summary

#### Introduction

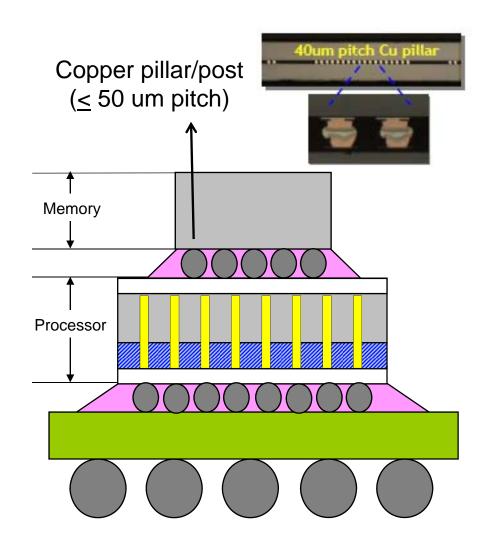

- Next Generation Flip Chip Interconnects

- 2.5, 3D Integration Process

- Electroplated Copper Pillars with Solder Caps

- Advantages

- Fine Pitch Capability

- Increased I/O Density

- Improved Electrical & Thermal Performance

- Superior Electro-Migration

- Higher Reliability at Lower Cost

#### 3D IC Test Challenges

- Wafer Probing

- · Thinned wafer handling

- ◆ Grinding before/after test

- Assembly flow vs. Test

- TSV test

- TSV defect

- Double-sided wafer probing?

- Die/wafer contact interface material

- Bond pads/ micro bumps/ TSV

- Cu pillars

- Contact force of high I/O number vs wafer thickness

- ◆ Probe Force

- Probe material

- Fine Pitch

- Area array pitch < 50um</li>

- > 1000 contacts

Fundamental Study Capability Is Required Jointly between Assembly and Test

# **Testing/Probing challenges**

- Probe Card Requirements

- P/C Required at 50μm & Below in Array

Configuration

- Small Bump Diameter

- Need Very Low Probing Force

- Need Very Good Tip Alignment

- Need Probe Compliance to Accommodate Bump to Bump Variation Across Wafer

## Goals/Objective

#### Evaluation Objective/Scope

- Probe Card Feasibility at 50μm Array

- Copper Pillar Bump Probing Evaluation

- Bump Damage Assessment

- Electrical, Thermal & Mechanical Characterization

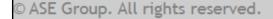

#### Test Equipment

- Test Chip by ASE

- LT50 Probe Card by SV Probe

- P-12 XLn Prober, HP93000 Tester

- Microscope, SEM, Veeco Profilometer

# **Equipment Utilized**

# **Test Chip Design**

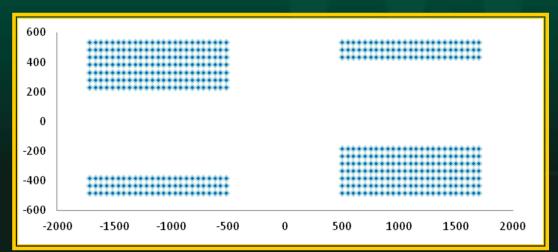

- Test Chip Design Details

- 50μm Pitch

- Array Configuration, 4 Groups, 500 Points Total

- Daisy-chain Resistance Measurement

#### **Array Layout**

#### **Optical Picture**

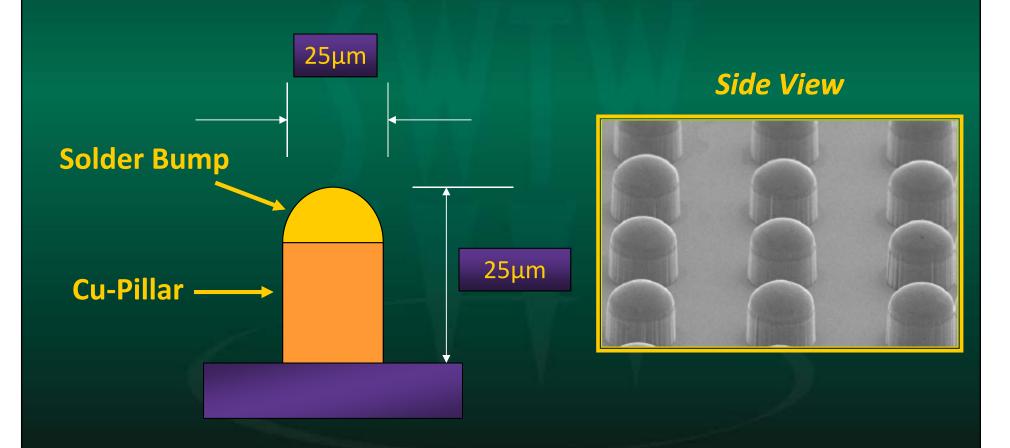

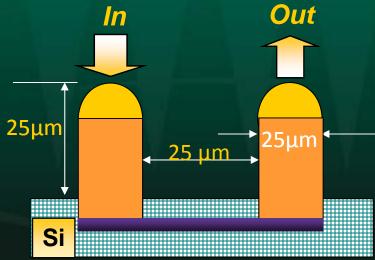

## **Cu-Pillar Structure**

*Initial Bump Height: ~25 +/-3μm*

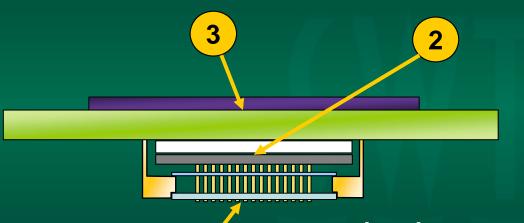

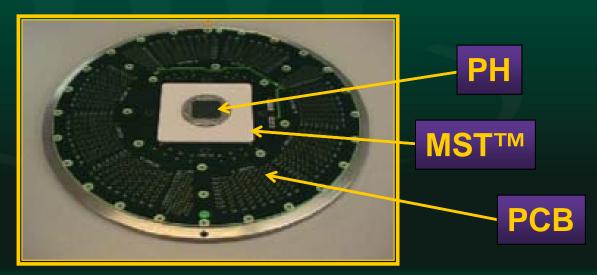

## LogicTouch<sup>TM</sup> Vertical Probing Technology

- 1. Probes / PH

- 2. Space Transformer

- 3. PCB

- Technology Capable of Probing 50μm Arrays

- Technology Scalable to 40μm Pitch

## **PROBE CARD CHALLENGES**

## **Scalability Challenges**

- Space Transformer Availability at 50μm Pitch Array

- Based on Standard Thin Film Technology Capability, Difficult to Achieve Escapement Required for Routing

- Need Pad on Via at Pitch & Hence MLC/MLO not Feasible for Array Configurations at 50µm Pitch

- New Type of Interconnect was Developed Internally the Modular Space Transformer or MST<sup>TM</sup>

# **Scalability Challenges**

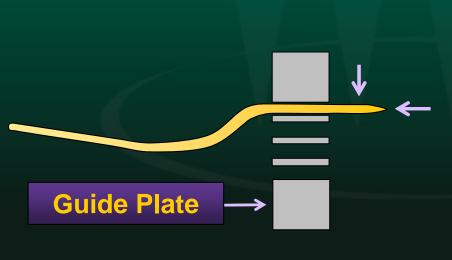

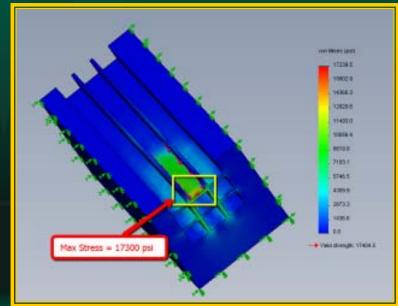

#### Guide Plate Wall Strength

- Reduced Wall Strength due to Reduced Wall Thickness due to the Spatial Constraints at 50µm Pitch

- Probes Designed to Minimize Loading on Guide Plate (FEA)

- Stress/Life Tests at Max OT to Ensure Wall Integrity

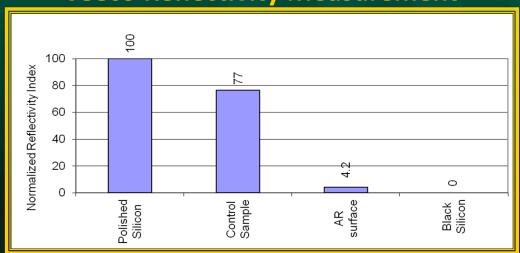

# **Guide Plate Reflectivity**

- The MEMS Guide-plates Used in LT50 Probe Cards have a Smooth & Polished Surface Finish

- Lighting Adjustments may be Required During Probe Card Setup at PCA & Prober

- Various Anti-reflective Surface Treatments were Evaluated to Reduce Normal Reflection

- Surface Scattering (Textured/Engineered Surface)

- Interference (Thin Films/Coatings)

**Veeco Reflectivity Measurement**

P-12 Prober

P-12 Prober Pictures: High Mag, Light Level 120, Focused 7-8 mils above Die Surface

## PROBE CARD DATA

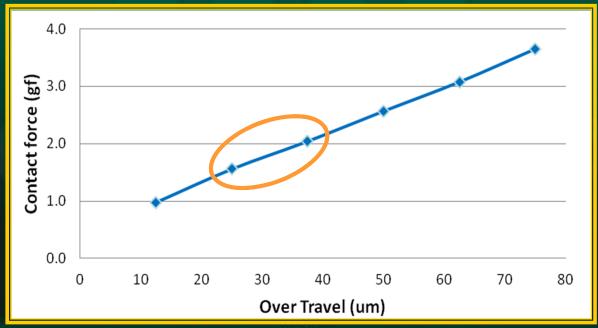

## **Probe Force**

- Contact Force of 2.5 gf @ 50μm OT

- - Minimize Bump Damage

- Accommodate Bump Co-planarity Across Wafer

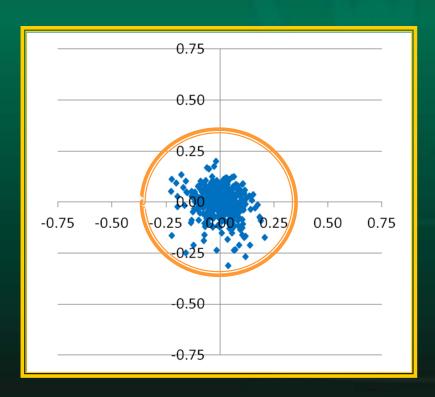

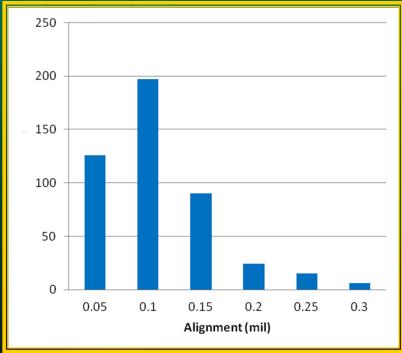

# **Tip Alignment**

Probe Tip Alignment – 0.3 mil Radial

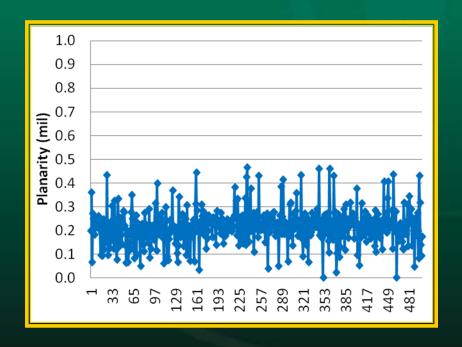

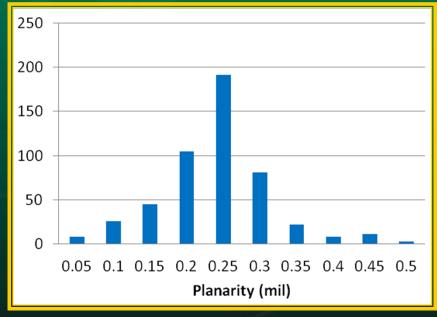

# **Planarity**

• Probe Planarity < 0.5 mil (12μm)

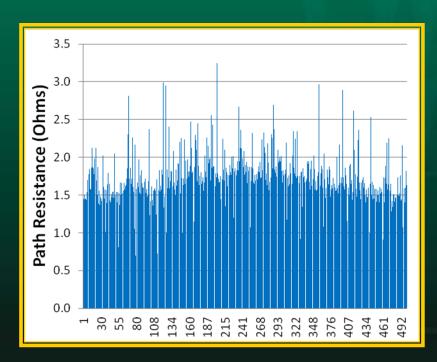

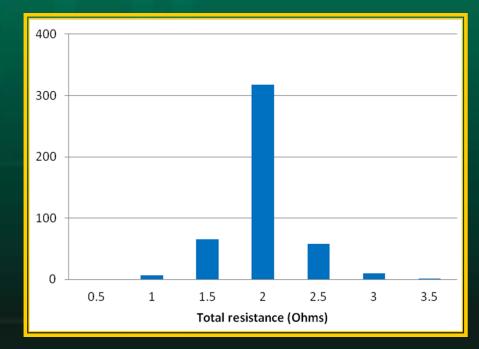

### Resistance on Gold

Max Total Resistance is 3.2 Ohms (includes Cres & Path Resistance through PH, ST & PCB)

## **COPPER PILLAR BUMP PROBING**

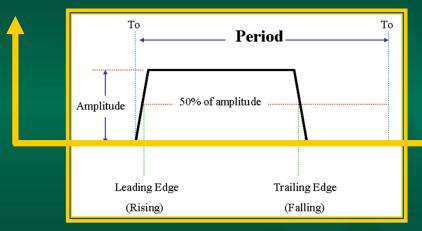

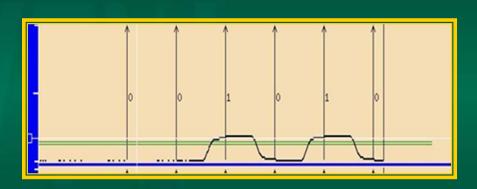

## **Test Method**

**Daisy Chain Bump Structure**

June 10 - 13, 2012

IEEE Workshop

## **Probe Mark**

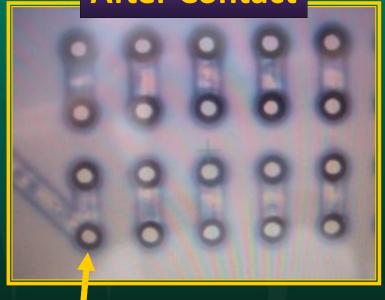

#### **After Contact**

\*Over-Drive: 40μm

# probing: 2 TDs

**Probe Mark Area Under 30%**

#### **Tests in Process**

#### Electrical Tests

Cres, Leakage Characterization vs. OT, # TD

#### Mechanical

- Probe Mark Size Characterization vs. OT, # TD

- Bump Damage Assessment vs. OT, # TD

#### Thermal

- Effect of Temperature (Hot, Room & Cold) on:

- Probe Card Performance (e.g. Cres Stability, Cleaning etc.)

- Probe Mark / Bump Damage

# **Summary / Conclusion**

- To Address Test Challenges Associated with Fine Pitch Copper Pillar Bump Probing

- A Test Chip with 25μm Pillar Bumps at 50μm Pitch Array was Designed & Fabricated

- An LT50 Probe Card at 50μm Pitch Array was Designed & Built with SV Probe's Proprietary ST Technology

- Test / Evaluation

- Probe Card Feasibility at 50µm Array Verified

- Good Probe Card Tip Alignment & Planarity

- Max Total Resistance through P/C was 3.2 Ohms, avg 1.7 Ohms

- P/C Passed Opens/Continuity Test on Copper Pillar Bumps

- Probe Mark was < 30% of Bump Area at 40μm OT at 2 TDs</li>

- Successful Collaboration between ASE & SV Probe & the Preliminary Evaluation Results to Date have been Positive