## IEEE SW Test Workshop

Semiconductor Wafer Test Workshop

June 9 - 12, 2013 | San Diego, California

# Probing Study of Fine-pitch Copper Pillars

**Alexander Wittig (Globalfoundries)**

Amy Leong, Tin Nguyen, Andrew McFarland, Mike Slessor (Form Factor)

**Darko Hulic (Nikad)**

## **Overview**

- Cu Pillar Market Trends

- Cu Pillar Probing Key Questions

- Experiment Set-up

- Cu Pillar Evaluation Results

- Conclusions

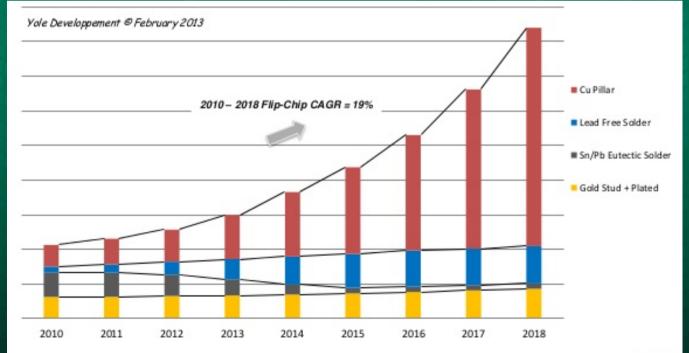

### Cu Pillars Surpass Solder Bumping by 2014

- Cu Pillar is expected to grow at CAGR(2010-18) of 35%, driven by

- CMOS 28nm IC (and beyond), including App Processors, Base Band for mobile phones

- Next generation of DDR memories (DDR3 and DDR4)

- 3D/2.5D interposer using CuP (ubumping)

- By 2014, > 50% of bumped wafers for flip-chip will be Cu Pillars

Source: Q1 2013

June 9 - 12, 2013 IEEE Workshop

### Why Copper Pillars for Flip Chip?

"Pillars" of copper are typically plated on the chip in wafer form through photolithography techniques. Solder bumps have fixed aspect ratios lower than one, whereas copper pillars offer aspect ratio flexibility, and therefore can increase I/O bump densities for many applications in addition to other advantages...

- Pitch limited to 150µm min, 120µm at best, due to spherical aspect and need for sufficient zheight gap for underfill flow

- Risks of electrical shorts by bridging

- Limited spacing between adjacent bumps for signal routing

- Limited spacing between adjacent bumps prevents the underfill from flowing causing underfill voids

- Reduced pitch leads to lower bump height (due to 1:1.3 aspect ratio) causing

- Reliability issue by lack of bump elasticity

- Reduced stand-off height making it more difficult for the underfill to flow.

to copper pillars

- Finer pitches possible down to 20µm

- Reduced risk of shorts between adjacent bumps

- Larger spacing between adjacent bumps for signal routing and easier underfill flow

- High bump aspect ratio (→ easier underfill flow)

- Copper pillars are a reliable lead-free bumping option

- Copper offers higher electrical conductivity than solder: 25% lower resistance than SnPb

- Higher current density capability (better resistance to electromigration)

- But higher elastic modulus (stress during attach process)

## **Cu Pillar Probing Key Questions**

- Probe Force -- To probe these fine Cu pillar structures, how low shall the probe force be to minimize solder cap damage and downstream packaging reliability risks?

- Contact Resistance -- How will contact resistance behave when probing at a very low contact force?

- Pitch Scalability -- How scalable is vertical probe card technology for sub-100um pitch?

## **Experiment Set-up**

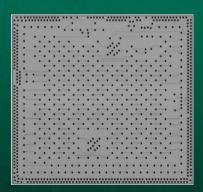

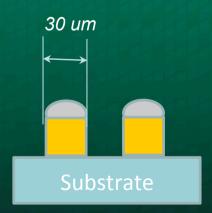

#### **Test Wafer Descriptions**

- Cu Pillar test wafers with daisy chains + fully shorted version

- 110um minimum pitch

#### **Probe Card Used**

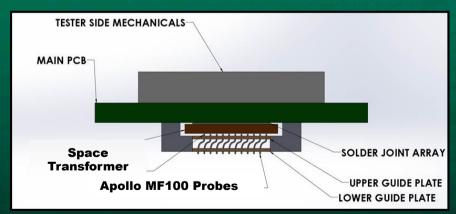

- FormFactor Apollo™ Probe Card

- MF100 Vertical MEMS Probe

#### **Measurement Conditions**

V93k PS400 12" Pogo Tower Tester:

– Prober: **TEL Precio**

Apollo™ MF100 Cu Pillar Probe Card

Test chip Map

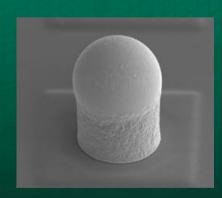

Cu Pillar with SnAg Caps 48 um Diameter

### **Measurement Details**

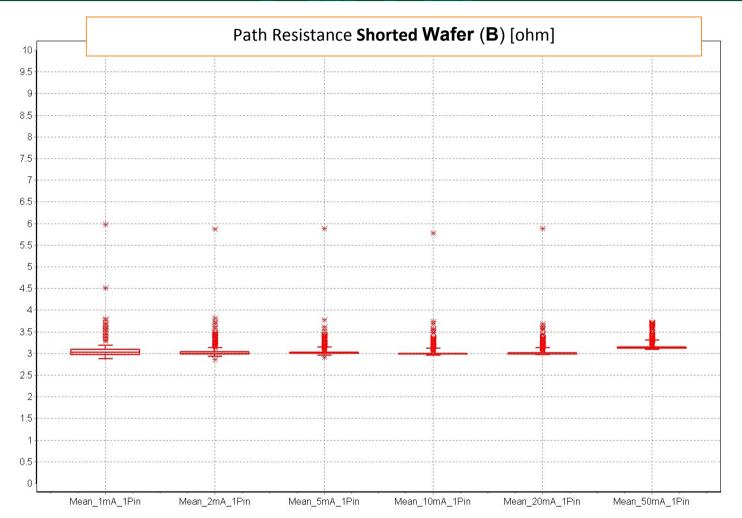

#### • Two different pillar shorting schemes are available

A: several single Bridges on Wafer -> measure single bridges 1-by-1 / daisy chains

B: Wafer shorted completely using non-patterned UBM

- -> The probes are triggered in a serial mode and each remaining probe is set to GND

- -> Backward current ~0 ohm due to parallelism

#### Measurement principles

- Force Current (I) -> Measure Voltage (U) -> Calculate Resistence (R)

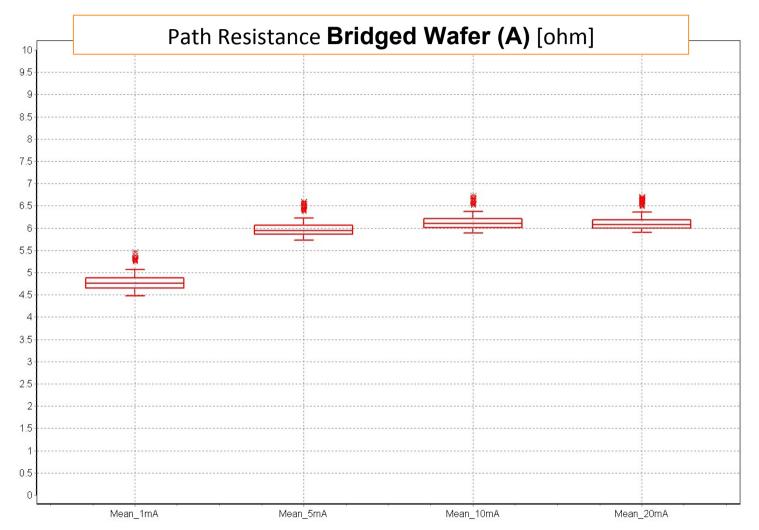

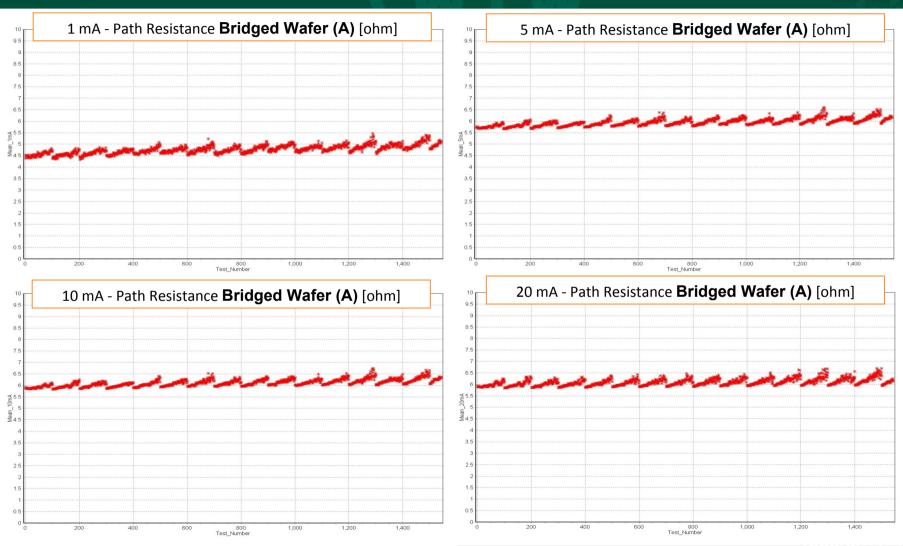

- Path Resistance using bridges (A):  $\geq$  5 ... 7 Ω

- Path Resistance using full UBM shorts (B):  $\geq$  2.5 ... 3.5 Ω

- Current Classes used:

A:

$$I = 1 - 5 - 10 - 20 \text{ mA}$$

B:

$$I = 1 - 2 - 5 - 10 - 20 - 50$$

mA

**Test Head Wiring**

Tester DUT Board

Pogo Tower

Probe PCB / ST

Probe Pin

Probe CRES

Pillar (Cu+SnAg)

Traces / UBM

June 9 - 12, 2013 IEEE Workshop

### **Apollo<sup>TM</sup> Vertical MEMS Probe Options**

Ideally matched to advanced grid-array and Cu pillar applications and roadmaps

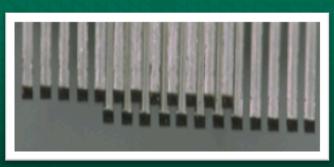

- <u>Vertical MEMS</u> designs for 100um grid-array pitch and below

- Extension of established Apollo<sup>™</sup> vertical product with MEMS precision

- Established worldwide service/repair infrastructures and skills

- Application-specific probe options for targeted Cu Pillar structures

- Product design is optimized through probe geometry & material choices

- Composite (multi-material) vertical probes, lithographically fabricated

- Low-force probing to minimize damages on Cu pillars with SnAg caps

- < 3 grams contact force/ probe at production overdrive</p>

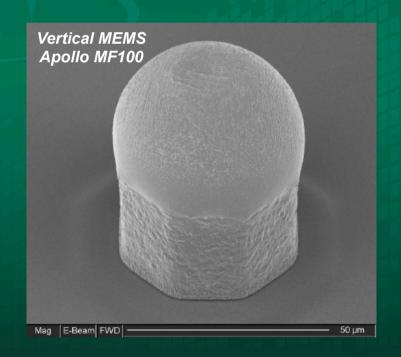

Apollo™ MF100 MEMS Probes

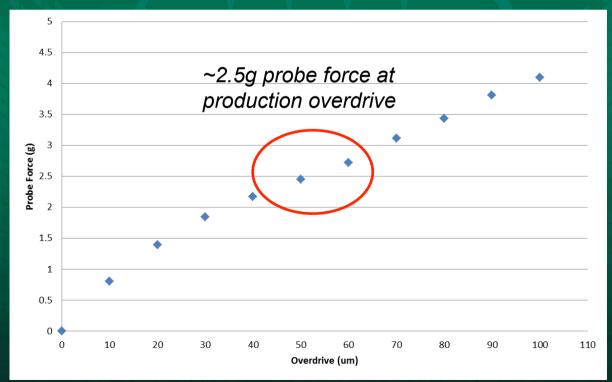

### Apollo<sup>TM</sup> MF100 Vertical MEMS Probe Force

- Apollo<sup>TM</sup> low-force MF100 MEMS probes were used to minimize probe damage to thin SnAg caps on Cu Pillar

- At an over-drive of 2 mil, MF100 probe offers ~2.5g probe force

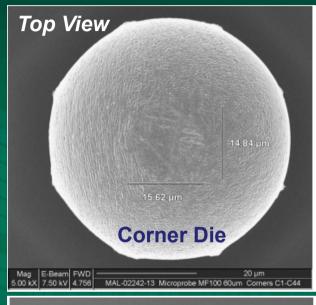

## **Probe Mark Optical Inspection**

- All probe marks passed outgoing inspection criteria

- Probe mark area (a) is < 50% of pillar cross sectional area (A) post probing

- Probe mark area increases with higher OD and probe force

- At 60um OD, 15-20% probe mark area ratio (a/A) was observed

Probe Marks @ 5 µm Overdrive

Probe Marks @ 60 µm Overdrive

June 9 - 12, 2013 IEEE Workshop

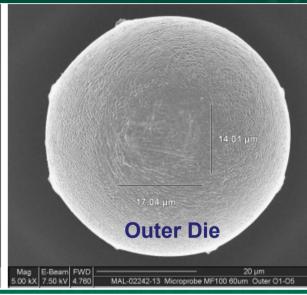

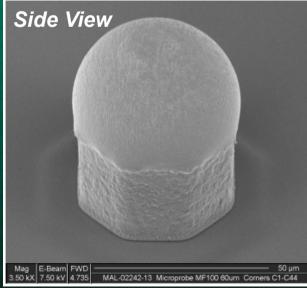

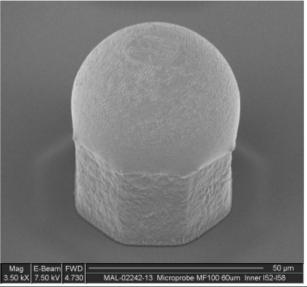

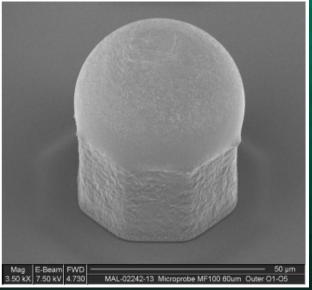

## **Probe Mark SEM Analysis**

**Consistent and Light Scrub Marks Were Observed Across the Wafer**

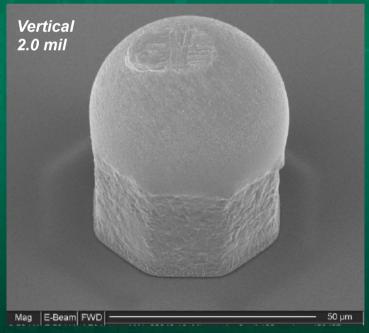

# Probe Mark Comparison Vertical MEMS MF100 vs. Vertical 2.0mil

- Low-impact probing was demonstrated with Apollo MF100

- Minimal solder material displacement on the surface

- Apollo MF100 shows better scalability for smaller Cu Pillar dimensions

- More even force at pillar footing for better packaging reliability

# Stable Contact Resistance Observed Bridge A Measurement -- Mean Whisker Plot

# Stable Contact Resistance Observed Bridge A Measurement -- Detailed Data Plot

# Stable Contact Resistance Observed Bridge B Measurement -- Mean Whisker Plot

# Stable Contact Resistance Observed Bridge B Measurement -- Detailed Data Plot

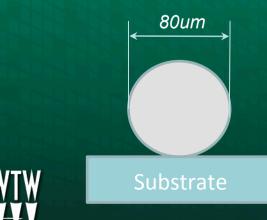

# 80um Pitch Node Further Reduces Cu Pillar Diameter and Height

- 80um Pitch Cu Pillar Advantages

- Smaller pillar diameter increases I/O density => More features/functions on mobile devices

- Shorter pillar reduces packaging height => Thinner smart phones/tablets

- How will probe card performance change for 80um pitch?

|               | Solder Bump | Cu Pillar Dimension Roadmap* |         |         |         |

|---------------|-------------|------------------------------|---------|---------|---------|

| Pitch (um)    | 150um       | 130um                        | 100um   | 80um    | 60um    |

| Diameter (um) | 80 um       | 60-70um                      | 40-50um | 25-30um | 20-25um |

| Height (um)   | 80 um       | 75 um                        | 60 um   | 50 um   | 40 um   |

June 9 - 12, 2013 IEEE Workshop

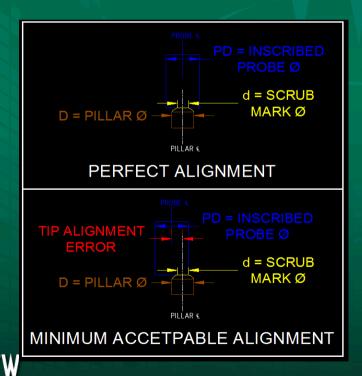

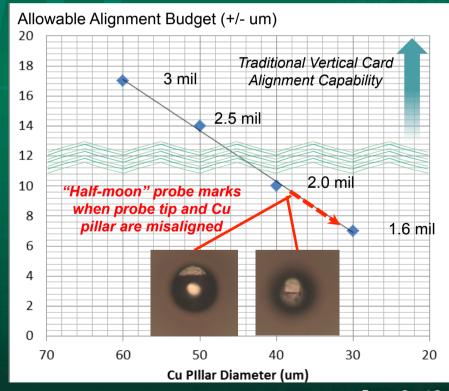

#### MEMS Precision is Critical For 80um Pitch and Below

- Allowable alignment budget between probe tip and Cu Pillar decreases as pitch and pillar diameter shrink

- Vertical MEMS probe fabrication and alignment precision is critical for 80um pitch/30um pillar diameter and below

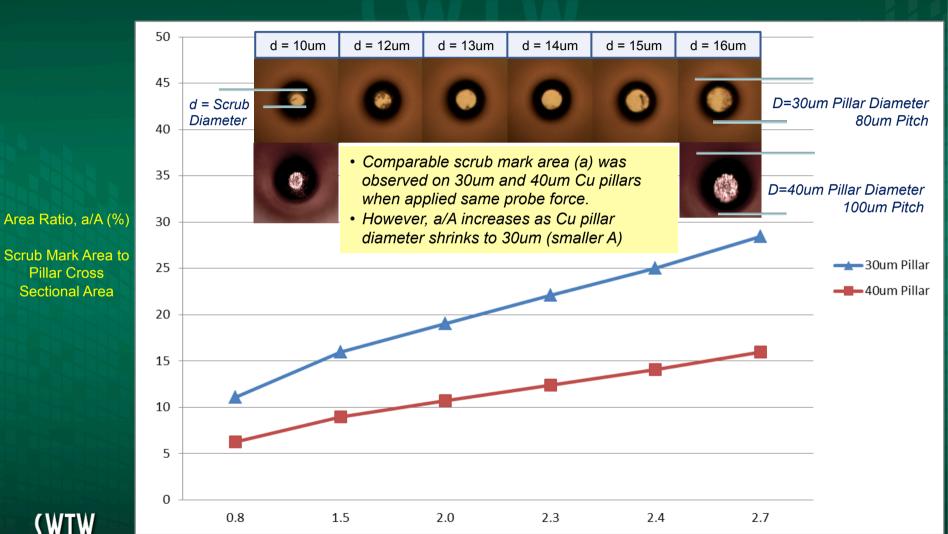

### Scrub Mark Area Correlation to Probe Force

Comparable (or Lower) Probe force as MF100 Workable with 80um Pitch Cu Pillars

Scrub Mark Area to Pillar Cross Sectional Area

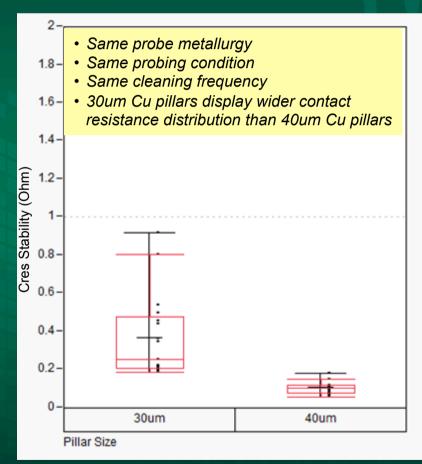

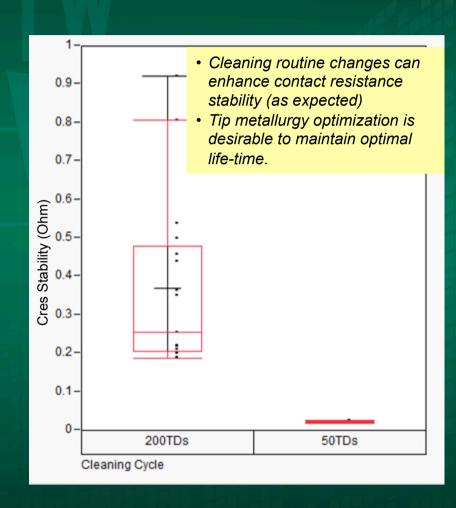

### **Contact Resistance Comparison**

## Optimization on probe Metallurgy and Probing Condition Are Desirable for 30um Cu Pillars

## **Next Steps & Future Work**

- Apollo<sup>TM</sup> MF100 Production Monitoring

- Yield stability

- Life-time

- Apollo<sup>TM</sup> MF80 Probe Qualification

- 80um grid-array pitch

- Lower probe force for 25-30um pillars

- New probe metallurgy (PM3) to enhance Current Carrying

Capability and Life-time @ 80um pitch

### Conclusions

- As Cu pillar packaging pitch shrink to 100um and below, FormFactor's high precision & low-force vertical MEMS technology has been qualified as a preferred configuration

- Technology scalability to support Cu pillar pitch shrink to 80um

- Apollo<sup>™</sup> MF100 product has demonstrated robust performance on 100um grid-array pitch Cu pillar for:

- Low impact/force probing

- Contact stability

- Alignment consistency and scalability

- Future work

- Monitor Apollo MF100 performance in production

- Qualify Apollo MF80 for 80um grid-array pitch