## IEEE SW Test Workshop

Semiconductor Wafer Test Workshop

June 9 - 12, 2013 | San Diego, California

# Accurate Probe Positioning by Using Low CTE Ceramic Substrate for 12 " Testing

Joonyeon Kim

Samsung Electronics

Jooyong Kim, Yunhwi Park

Samsung Electro-Mechanics

#### Overview

- 12" Test Trend and Challenge

- Goal of Study

- Selection of proper CTE and Temperature of Ceramic

- 12" accurate probing using LTCC ceramic

- Summary

#### **Test Trend**

• Higher pin count, smaller pad size, larger wafer test

## Accurate pin positioning Issue

- Hot/Cold electrical die sorting is needed

- There is expansion discrepancy between Si wafer and MEMS pin on ceramic of probe card

- And more, temperature difference exists

- So, accurate pin positioning becomes more difficult, as pad size decrease, hot/cold temperature differences increase, and wafer size increase

- Many probe card makers feels hurdle of it

#### **Goal of Study**

- Suggest the guideline to select CTE and temperature of ceramic STF to meet the need of small pad probing

- Consider the main parameters affecting temperature of ceramic

- Summarize various ceramics suitable for STF

- Show the field test result of the accurate pin positioning using low CTE LTCC ceramic

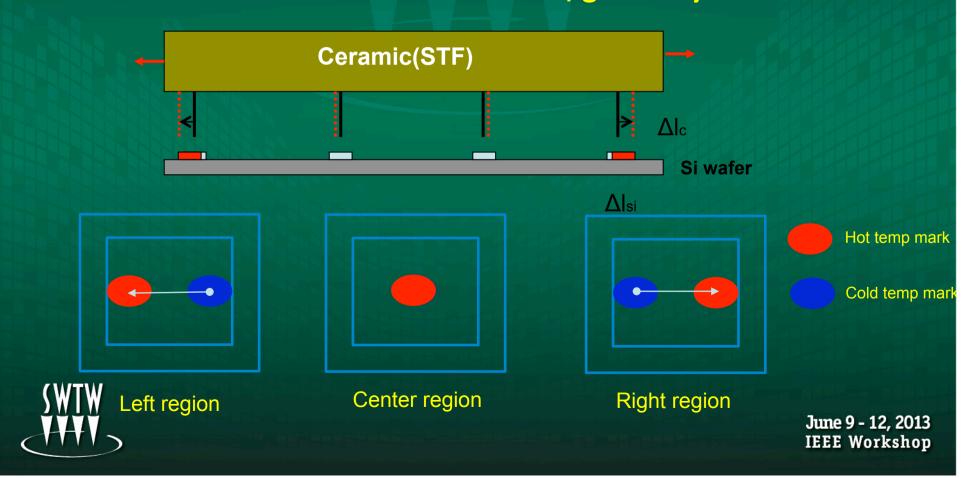

## Scrub mark movement Analysis

- MEMS Pin scrub mark moves as test temperature changes

- Almost ceramic has higher CTE than Si wafer, so hot temp mark moves out relative to cold scrub mark, generally.

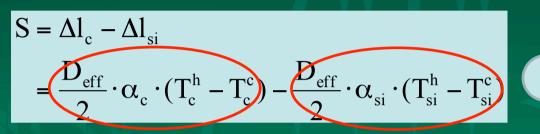

## **Moving Distance of Scrub Mark**

Scrub mark's moving distance(S) from cold to hot temp.

Ceramic expansion

Wafer expansion

**Bonding Pad**

Deff: diameter of active test pad region

$\Delta l_c$

$\Delta l_{ci}$

$\alpha_{\rm c}$

$\alpha_{si}$

ceramic expansion

wafer expansion

CTE of ceramic

CTE of Si wafer

Ceramic temp @ hot test

Ceramic temp @ cold test

Wafer temp @ hot test

Wafer temp @ cold test

Deff

Wafer

June 9 - 12, 2013 IEEE Workshop

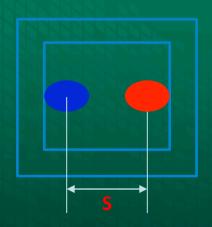

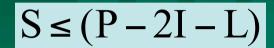

To position hot and cold mark in bonding pad, following condition must be met

S: Scrub mark movement

P: Bonding pad size

I: Bonding margin

L: Scrub mark size

**Bonding Pad**

Deff: diameter of active test pad region

For 60um pad with 15um bonding margin and 10um scrub mark size, moving distance(S) must be kept below 20um only !!

After summarizing above equations(1,2), following condition is derived for safe positioning.

$$\left( T_c^h - T_c^c \right) \leq \frac{K}{\alpha_c} \quad \text{where,} \quad K = (P - 2I - L) \cdot \left( \frac{2}{D_{\text{eff}}} \right) + \alpha_{\text{si}} \cdot \Delta T_{\text{si}}$$

- There are two variables to control probe mark position for determined hot/cold test temperature

- (1) Temperature of ceramic: T<sub>c</sub>

- (2) CTE of ceramic

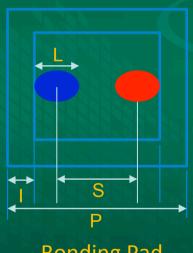

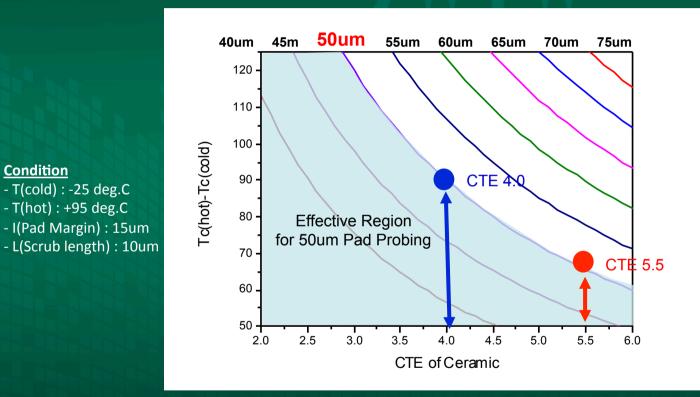

For various bonding pad size, we can draw the line for safe positioning of probe mark as below

Condition

- T(cold): -25 deg.C - T(hot): +95 deg.C

$$\left(T_c^h - T_c^c\right) \le \frac{K}{\alpha_c}$$

**IEEE Workshop**

1st Case: For 50um probing with ceramic CTE 5.5, ceramic temp difference below 65 deg.C is needed. But, for ceramic CTE 4.0, this number can be eleased to 90 deg.C → It is easier to be accomplished June 9 - 12, 2013

- 2<sup>nd</sup> Case: For determined CTE of ceramic, we can adjust probe position by changing temperature of ceramic

- → For ceramic with CTE 4.0ppm/k, 45um pad probing is possible by reducing ceramic temperature difference from 90 to 70deg.C

- → Important point for controlling scrub mark positioning

- T(cold): -25 deg.C

- T(hot): +95 deg.C

- I(Pad Margin): 15um

- L(Scrub length): 10um

$$\left(T_{c}^{h} - T_{c}^{c}\right) \leq \frac{K}{\alpha_{c}}$$

June 9 - 12, 2013 IEEE Workshop

## How we can control ceramic temp??

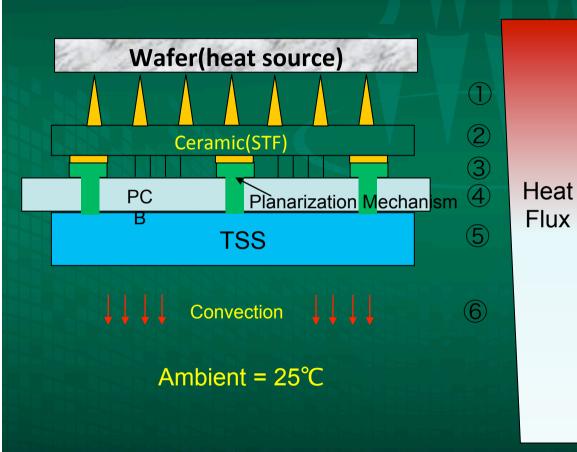

System overview

**Constant Temp(Wafer)**

- ① Air/MEMS Pin

- **2** Ceramic Substrate

- 3 Bond/Solder/Interposer

- 4 PCB/Planarization Mech.

- **5** TSS

- **6** TSS to Chamber

**Const. Temp(Ambient)**

TSS: Tester Side Stiffner

June 9 - 12, 2013 IEEE Workshop

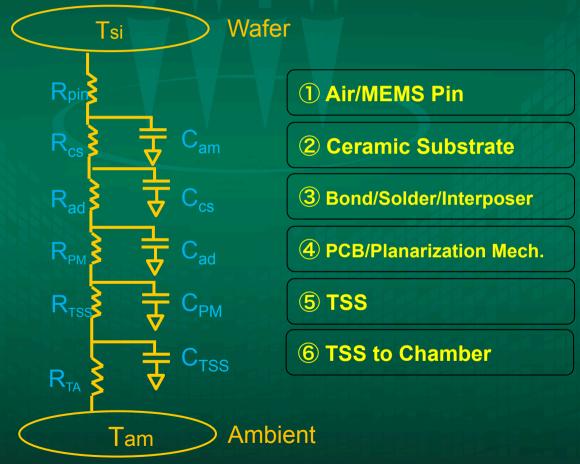

- Heat transfer can be analyzed by RC thermal equivalent circuit

- Constant voltage(temperature) condition

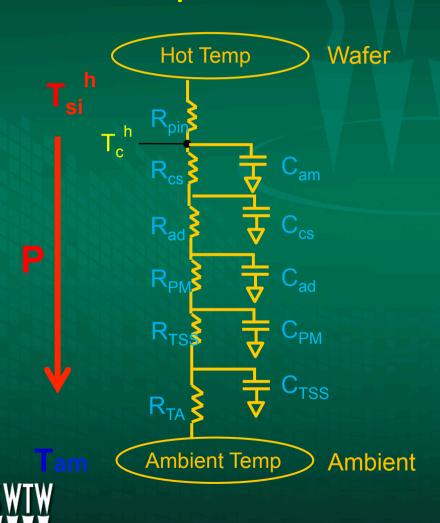

Derivation of equation for ceramic temperature at hot test condition

**Heat flux(P)**

= (Temp. Difference) / (Thermal Resistance)

$$P = \frac{T_{si} - T_{am}}{R_{th}}$$

$$R_{th} = R_{pin} + R_{cs} + R_{ad} + R_{PM} + R_{TSS} + R_{TA}$$

$$= R_{pin} + R_{other}$$

**Ceramic Temp(Tc)**

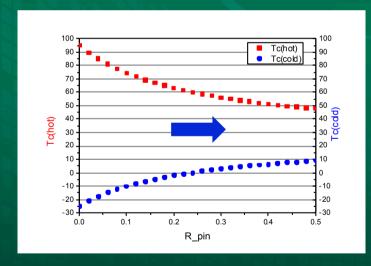

$$T_c^h = T_{si}^h - \frac{R_{pin}}{R_{th}} \cdot (T_{si}^h - T_{am})$$

$$\rightarrow$$

$T_c^h = f'n(R_{pin}, R_{th})$

→ To decrease T<sub>c</sub><sup>h</sup>, Rpin ↑ or Rth ↓

June 9 - 12, 2013 IEEE Workshop

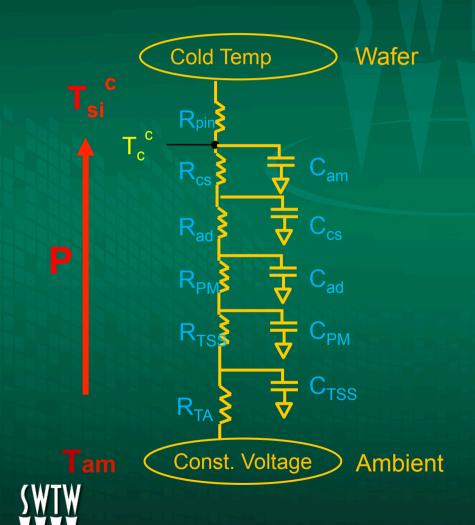

**Derivation of equation for ceramic temperature : (2)** condition

$$P = \frac{T_{am} - T_{si}}{R_{th}}$$

$$R_{th} = R_{pin} + R_{cs} + R_{ad} + R_{PM} + R_{TSS} + R_{TA}$$

$$= R_{pin} + R_{other}$$

$$T_c^c = T_{si}^c - \frac{R_{pin}}{R_{th}} \cdot (T_{si}^c - T_{am})$$

$\rightarrow$  To increase  $T_c^c$ ,  $R_{pin} \uparrow or R_{th} \downarrow$

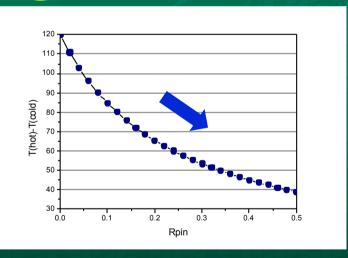

1st Method to control the ceramic temperature - pin height increasing

$$R_{other} = R_{cs} + R_{ad} + R_{PM} + R_{TSS} + R_{TA}$$

→ As pin height increases, ceramic temperature difference is decreased 1st way to get a accurate positioning for finer bonding pad

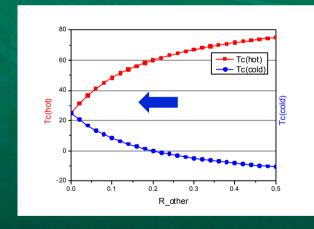

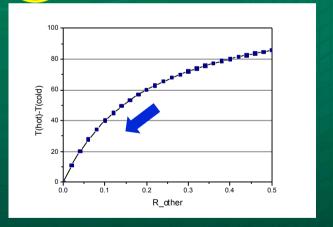

2<sup>nd</sup> method to control the ceramic temperature – reducing thermal resistance of system from ceramic to TSS

As Rother decreases, ceramic temperature difference is decreased

(WTW; high thermal conductivity material, # of PM increase, etc.

2nd way to get a accurate positioning for finer bonding pad June 9 - 12, 2013

IEEE Workshop

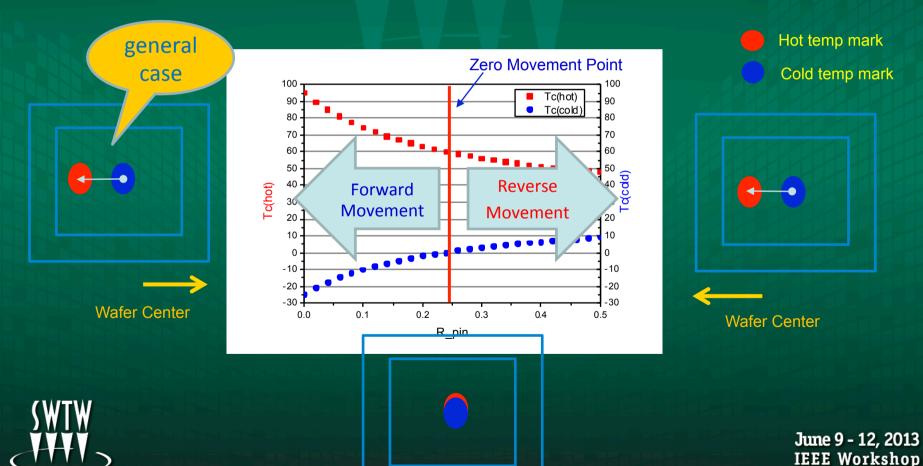

#### **Condition for Zero Movement**

Let's remind the scrub mark movement equation

$$S = \frac{D_{eff}}{2} \cdot \alpha_c \cdot (T_c^h - T_c^c) - \frac{D_{eff}}{2} \cdot \alpha_{si} \cdot (T_{si}^h - T_{si}^c)$$

If S = 0, there is no mark movement during hot/cold test

$$T_c^h - T_c^c = \frac{\alpha_{si}}{\alpha_c} (T_{si}^h - T_{si}^c)$$

Ex) CTE(ceramic) = 4.3 ppm/K, CTE(Si) = 3.0 ppm/K,  $T_{si}(hot) = 95 \text{ deg.C}, T_{si}(cold) = -25 \text{ deg.C}$

$$\rightarrow$$

Tc(h) - Tc(c) = (3/4.3) \* (95 + 25) = 83 deg.C

#### **Movement Direction**

We can look strange behavior of probe mark movement, if ceramic temperature difference is decreased over "0" movement point

→ S < 0 : reverse movement of scrub mark between cold & hot condition

#### **Ceramic for STF**

- Ceramic for STF must have following properties

- low CTE, via position accuracy, strength, chemical endurance etc

- LTCC may be good candidate material for its low CTE and accurate via position

| N.                          | LTCC                     | НТСС    |              |

|-----------------------------|--------------------------|---------|--------------|

|                             |                          | Alumina | Mullite      |

| Composition                 | Glass+Al2O3              | Al2O3   | 3Al2O3-2SiO2 |

| CTE(ppm/K)                  | 3.5~5.0                  | 5.5~6.0 | 2.5~4.0      |

| Thermal conductivity( W/mK) | 3                        | 15      | 6            |

| Heat capacity(J/gK)         | 0.96                     | 0.88    | 0.98         |

| Bending Strength(Mpa )      | 200                      | 350     | 300          |

| Young's Modulus(GPa)        | 130                      | 300     | 230          |

| Conductor                   | Ag                       | W/Mo    | W/Mo         |

| Via position Accuracy( %)   | 0.05%<br>(Non-Shrinkage) | 0.2%    | 0.2%<br>June |

| 20 1666                     |                          |         |              |

SWTW TTT

9 - 12, 2013 Workshor

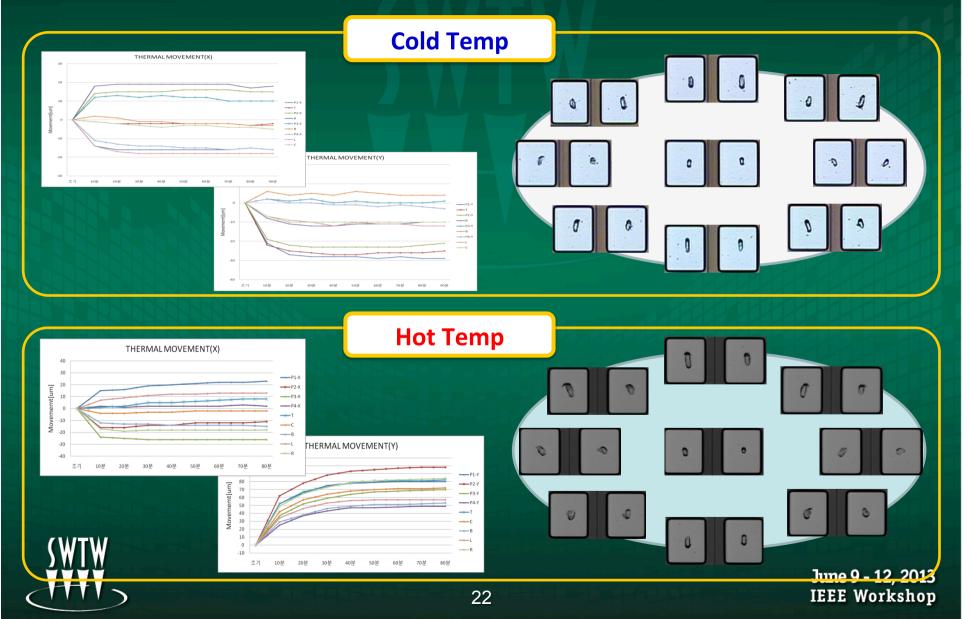

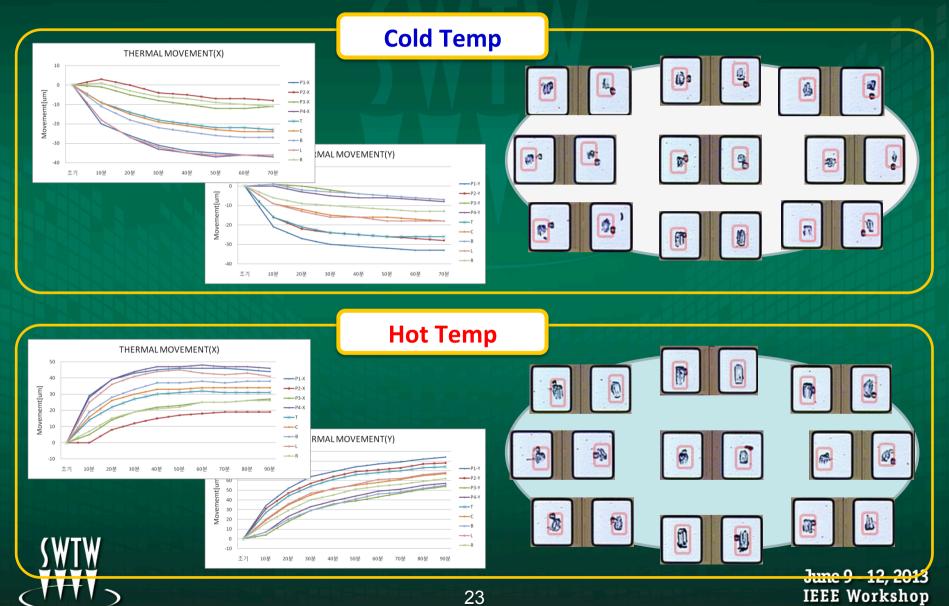

## **Probe Card using LTCC**

- Test condition is

- Hot temp =100°C. Cold temp = -25°C

- $CTE_{wafer}$  =3.0 ppm/K ,  $CTE_{LTCC}$  = 4.3 ppm/K

- "Zero movement" condition is as follows

$$T_c^h - T_c^c = \frac{\alpha_{si}}{\alpha_c} (T_{si}^h - T_{si}^c) = \frac{3.0}{4.3} (100 - (-25)) = 87^{\circ} C$$

- If temp difference is near 87°C, scrub movement is minimized

- If temp difference is smaller than 87°C, reverse movement occurs

- 2 kind of probe card were fabricated and tested

- First card shows very small scrub mark movement during hot/cold test

- Second card shows reverse movement

# Scrub Mark Test (Probe type 1)

## Scrub Mark Test (Probe type 2)

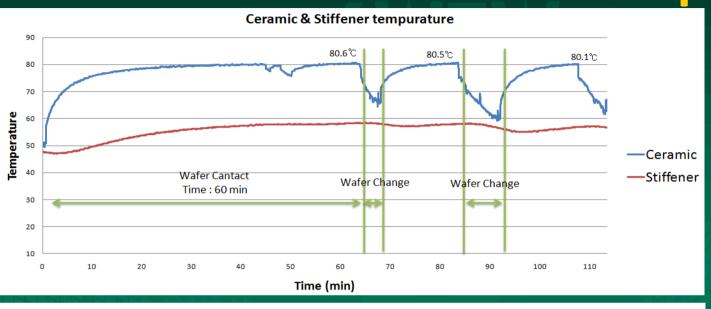

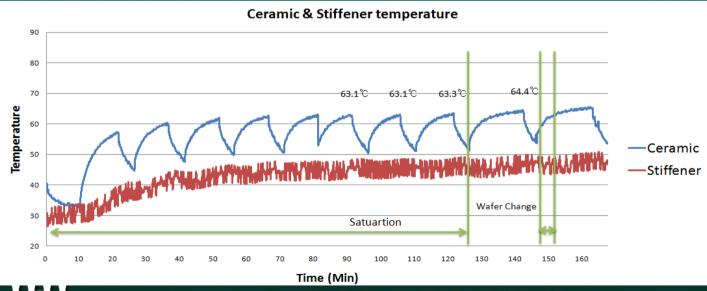

## Probe substrate temp

Probe type1

Probe type2

June 9 - 12, 2013 IEEE Workshop

#### Summary

- Probe mark position can be controlled by CTE and temperature of ceramic STF

- Guide line to select proper CTE and temperature for various pad size was derived

- Main factors to control ceramic temperature and its effects was analyzed

- Probe mark movement direction can be estimated by ceramic temperature

- Probe card for 60um pad test was fabricated using LTCC, and its performance is presented

#### Acknowledgements

- Jae-won Kim

- Ji-ho Jung

- Su-kyung Choi

- Sang-kyu Yoo

- Jung-yeop Kim

- Seung-bae Ahn

- Tae-yeop Oh

SAMSUNG ELECTRO-MECHANICS

- Soo-hyun Yoo

- Gyu-man Hwang

- Sung-mo Kang

- Yong-ho Cho