## SW Test Workshop

Semiconductor Wafer Test Workshop

June 7 - 10, 2015 | San Diego, California

## WLP Probing Technology Opportunity and Challenge

**Clark Liu**

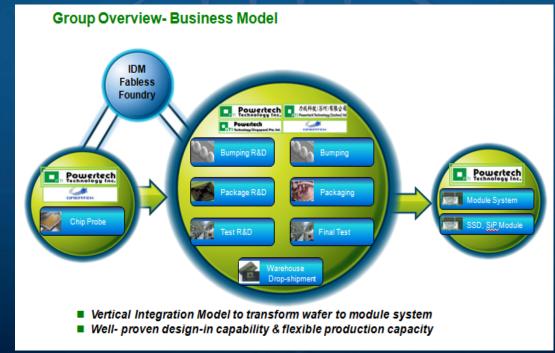

#### **PTI Group Overview**

■ Founded : May/15/97'

■ Capital : USD 246 Millions

■ Total Assets : USD 2.2B

■ Employees : 11,100 (Greatek included)

■ Major Services : Chip Probing, Bumping,

■ Packaging, Final Test & Module Assembly

■ IPO : 4/3/03' in Taiwan

### **Group Overview- Global Network**

**Chung-Li Plant**

**Customer Success!!**

#### Put more resource for next technology!

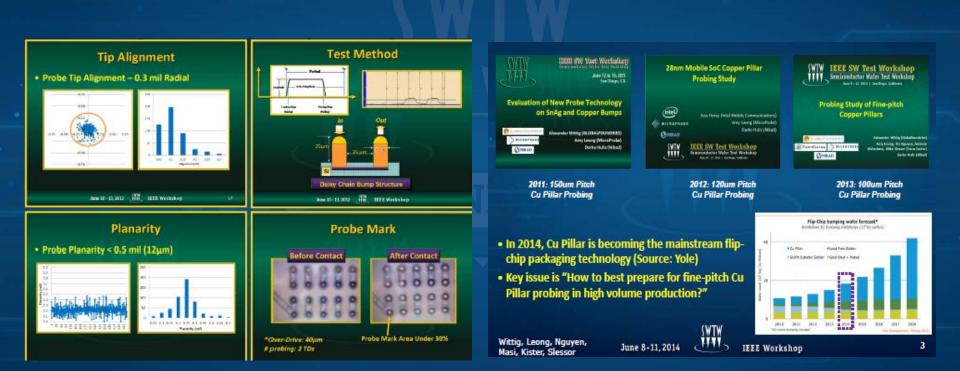

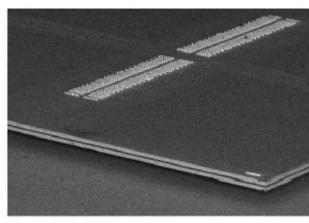

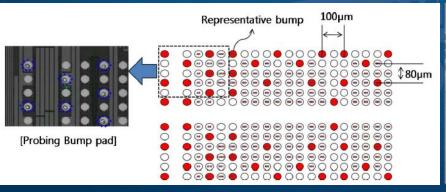

2012 SWTW ASE\_SV 50um Pitch Array

2014 SWTW FFI 80um Pitch CPB

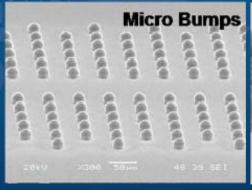

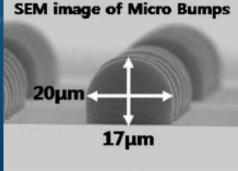

#### Probing at 2G Wide I/O Bump Pad

Source: 2011 IEEE \_ Samsung

Clark Liu

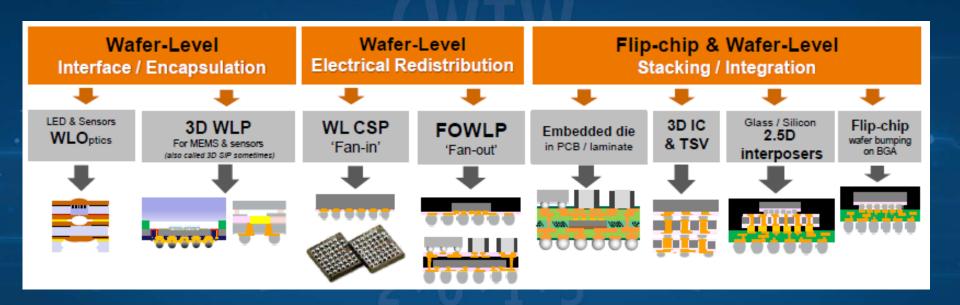

#### WLP(Wafer Level Packages)

Wafer-level-packages have emerged in many different varieties that can be categorized into different advanced packaging technology platforms

Source: 2013 SEMI \_ Yole

#### Map of WLP manufacturing companies

Source: 2015 Yole

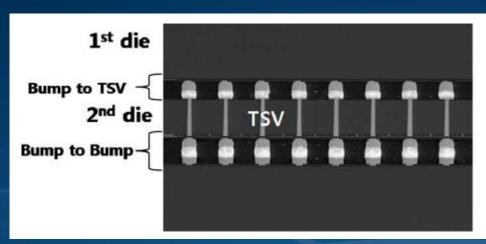

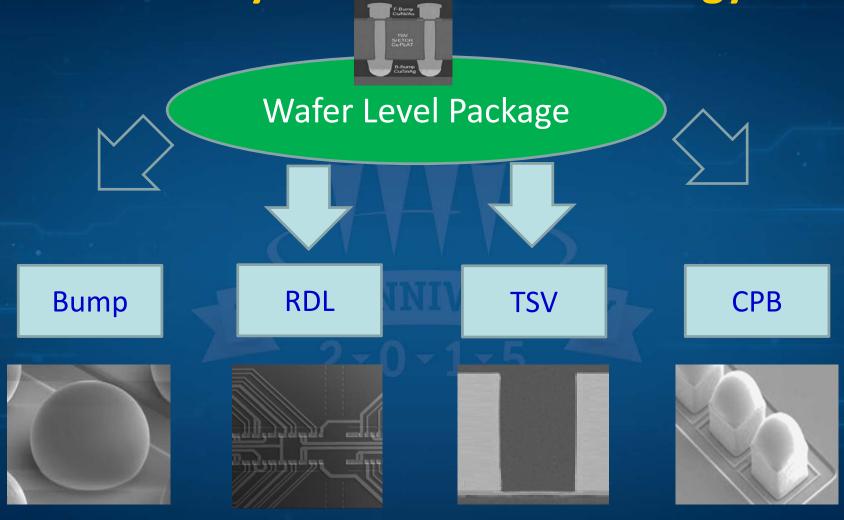

#### **WLP Key Connection Technology**

#### From Kid View!

Wafer Level Package

Bump like

RDL like

TSV like

CPB like

**SW Test Workshop**

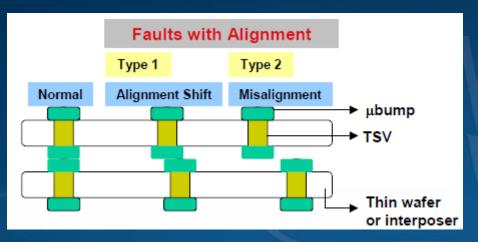

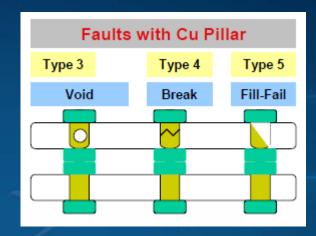

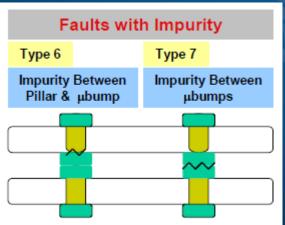

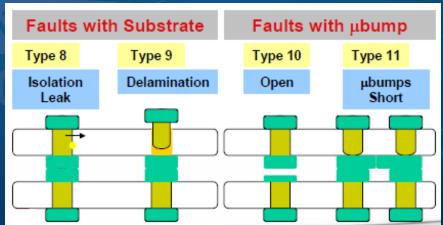

## **Electrical Tests for WLP Connectivity Fault Model**

Source: 2010 IEEE 3D IC Workshop \_TSMC

#### Fault Model for different test items

| Fault Detection of Test Items                        |                 |        |                    |        |        |          |        |           |        |            |         |

|------------------------------------------------------|-----------------|--------|--------------------|--------|--------|----------|--------|-----------|--------|------------|---------|

|                                                      |                 |        |                    |        |        |          |        |           |        |            |         |

|                                                      | Fault Detection |        |                    |        |        |          |        |           |        |            |         |

|                                                      |                 |        |                    |        |        |          |        |           |        |            |         |

|                                                      | Misalignment    |        | Abnormal Cu pillar |        |        | Impurity |        | Substrate |        | micro-bump |         |

|                                                      |                 |        |                    |        |        |          |        |           |        |            |         |

| Test Item                                            | Type 1          | Type 2 | Type 3             | Type 4 | Type 5 | Туреб    | Type 7 | Type 8    | Type 9 | Type 10    | Type 11 |

| Continuity test                                      |                 | v      | 27.300             | v      |        |          |        |           | v      | v          |         |

| Resistance test                                      | *V              | v      | *V                 | v      | *V     | *V       | *V     | v         | V      | v          | *V      |

| Capacitance test                                     | *V              | V      | *V                 | v      | *V     | *V       | *V     | V         | v      | V          | *V      |

| Leakage test                                         | *V              | v      | *V                 | v      | *V     | *V       | *V     | v         | v      | v          | *V      |

| AC test                                              | v               | v      | v                  | v      | v      | v        | v      | v         | v      | v          | v       |

| * means need high resolution measurement tool/method |                 |        |                    |        |        |          |        |           |        |            |         |

|                                                      |                 |        |                    |        |        |          |        |           |        |            |         |

Source: 2010 IEEE 3D IC Workshop \_TSMC

## WoW!

Source : Taipei 101

**Challenge?**

**Opportunity?**

Cost?

**Technology?**

**New Model?**

**Cooperation?**

Source: NTHU

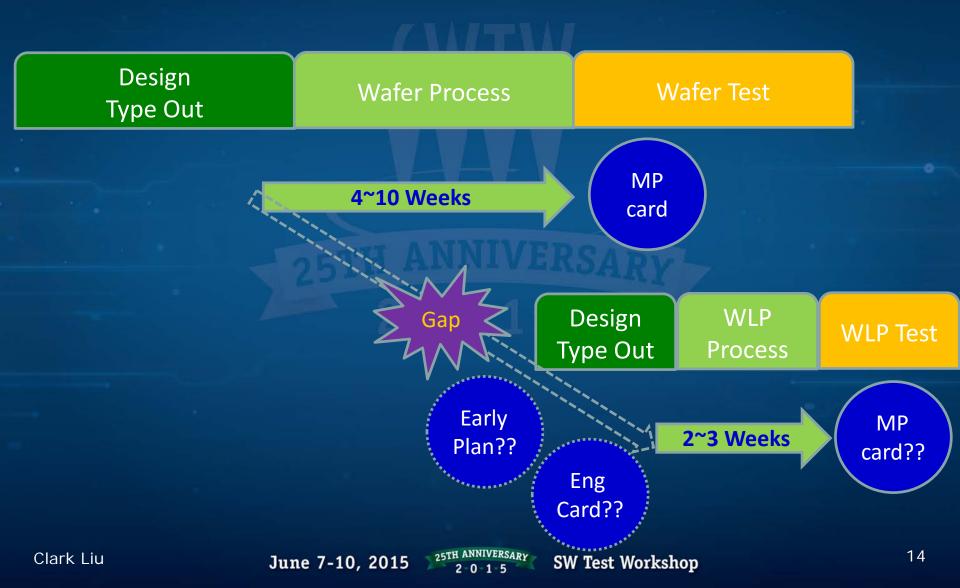

#### **Case1: Tools Short Delivery Cycle Time?**

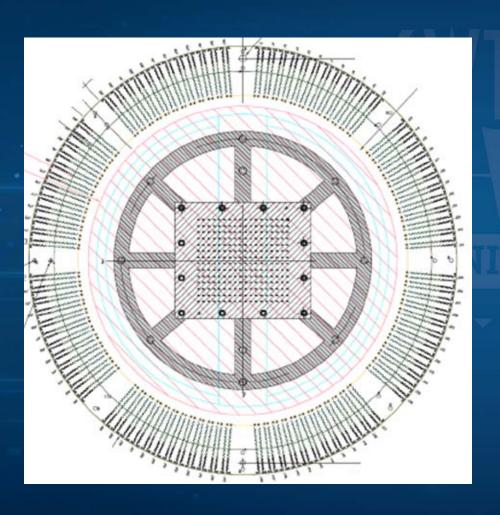

#### [Ex] WLCSP 256DUT Probe card

#### Bump Type: WLCSP

- a. Diameter: 300um

- b. Height: 170um ± 10%.

- c. Pitch: 500um

- d. TD: 10

- f. Total Pin Count 2560 Pins

**Delivery Time 8 Weeks**

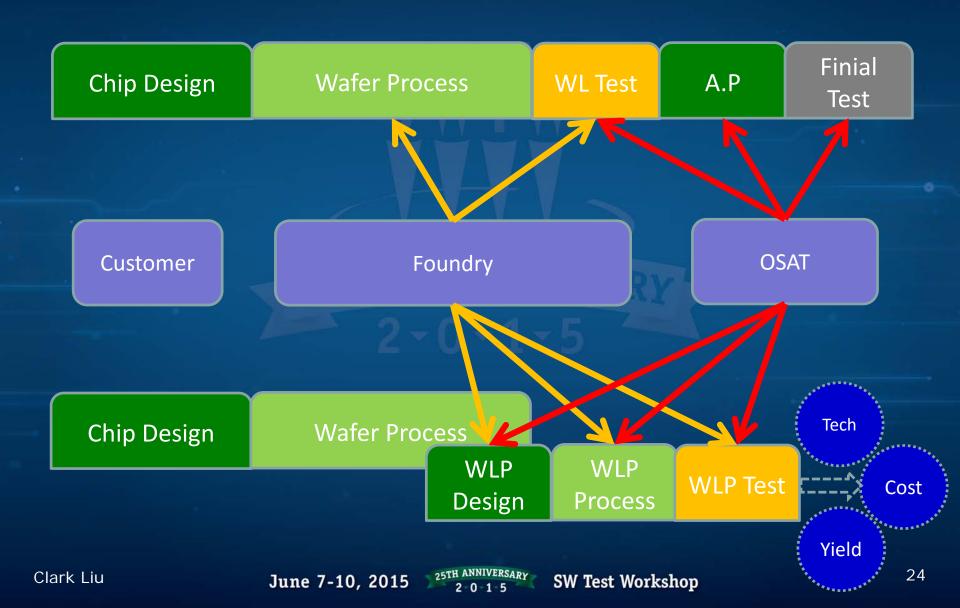

# Case2: Process Change for more Chip Probing?

Exist Process

Wafer Process

Wafer Test

**Assembly**

**Finial Test**

**Process X**

Wafer Process

Wafer Test(KGD)

**WLP**

**WLP Test**

**Assembly**

**Process Y**

Wafer Process

WLP

WLP Test (KGD)

**Assembly**

#### **More WLP Test or More Finial Test?**

WLP Test **Finial Test Fine Pitch Pitch Limit** Clean/10K **Contact Force** Cleanness **Silicon Base Package Base** um mm

Pictures Source : Mitsubishi

17

## **Wafer Test or Finial Test Vender** @ WLP Testing?

Wafer Test Vender

Finial Test Vender

- **Cycle Time Challenge**

- **Cost Challenge**

Clark Liu

**New Process Challenge**

- **Cooperation Model Challenge**

- **Wafer Level Requirement and** Quality

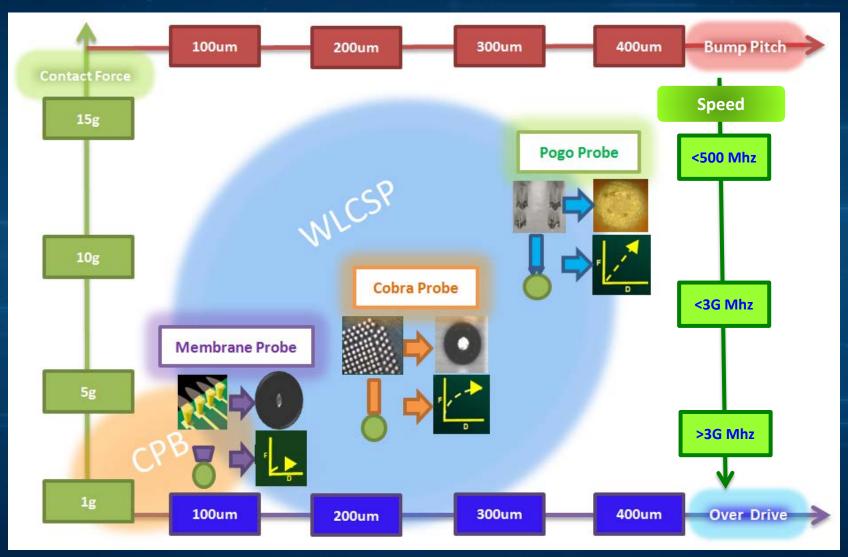

### **WLCSP / WLCPB Probe Card**

Source: SWTW

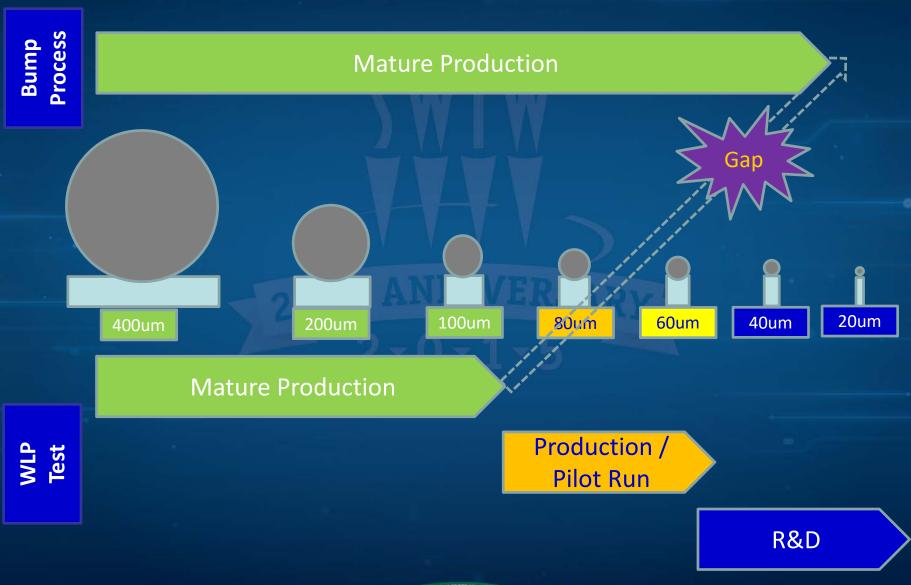

#### **Bump Process & WLP Probing Roadmap**

# Ideal Probe Force v.s Over Drive @ WLP Probing

**Probe Force Depend on Material Low Force Keep Electrical** No Damage **All Pass Point Over Drive Slope Depend on Material**

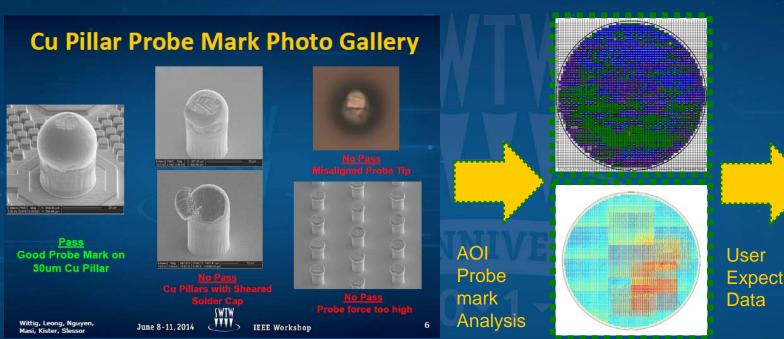

#### **Case 3: Probe mark analysis Technology**

**AOI Probe Mark Analysis Challenge** Different -ayer **RDL** Bump **CPB**

#### What Expect data from those Probe mark?

Data Mining:

(1) ProberPerformance(2)Probe cardPerformance

[Keep Under Development]

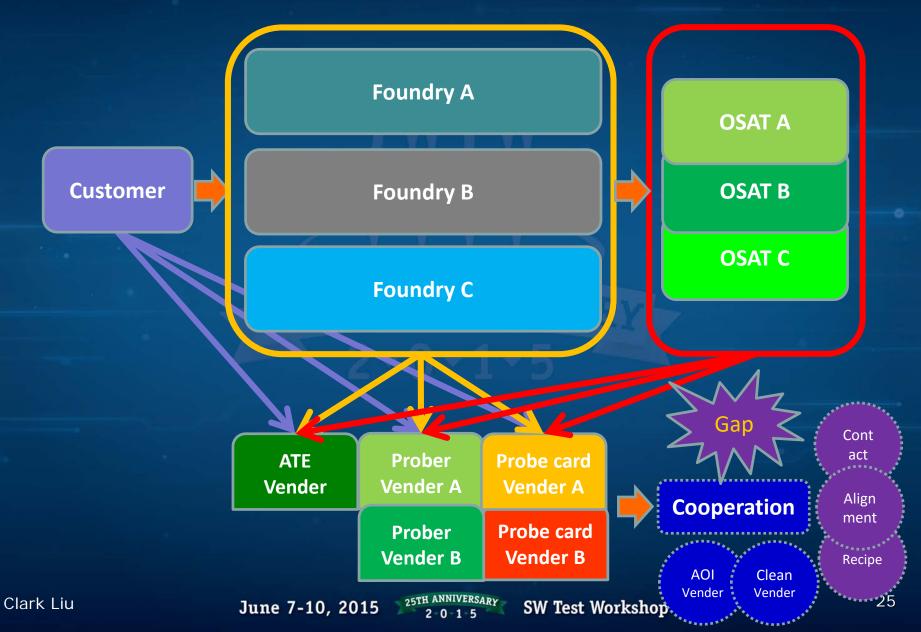

#### Case 4: Business or Process Change?

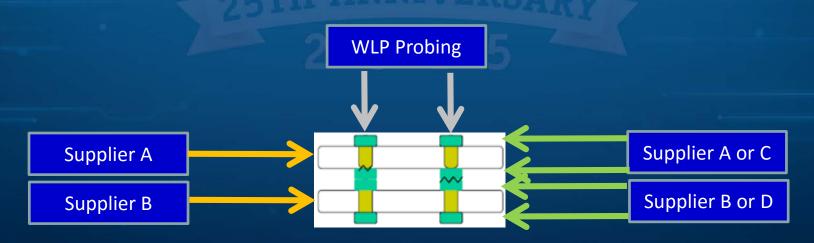

#### Same Issue but different site?

#### Conclusion

- Cooperation from

Customer to Supplier

(Design House

/Foundry/OSAT/Vender).

- New opportunity for Wafer/Finial Test I/F vender.

- The Evolution Business

Model will start change something.