# Automotive, the Roadmap of Technologies and their Influences on Testing

### **Davide APPELLO**

### **Automotive Digital Solutions Macro-Division**

### Automotive & Discrete Group

STMicroelectronics

An apparently invisible revolution is crisscrossing the semiconductor industry developing components targeted to the automotive market. Until recent days, this industry usually behaved unadventurously, adopting technology and solution previously experimented by other industry applications. The sudden increase of the required performances pushed to the adoption of very advanced technology nodes.

We expect that all these will also have an impact on the methods and solutions applied during production test. The talk will develop some of the factors proposed in the remainder of this abstract together with other elements.

A very popular topic is **functional safety (FuSa)** whose requirements are nowadays pervading the majority of new designs. FuSa is indeed an innovative element of our industry essential to the actual development of autonomous driving. It is already a consolidated solution present in many safety applications including for example braking, steering and passive safety devices. Test engineer welcomed the introduction of FuSa. Many advanced testability features became part of the functionalities offered to the customer and therefore no more seen as overhead for the SoC implementation. Nonetheless, other criticalities and additional factors are present.

Two additional key factors, though not orthogonal each other, might drive changes to the traditional test practices:

- The correlation of performances between functional activation and test is progressively loosening •

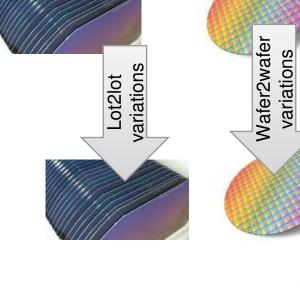

- Parametric variations linked with new advanced technologies like FdSOI and FinFET are breaching typical test paradigm (e.g. divide and conquer or implication test)

Finally, we shall concentrate on the role and the weight of assembly technologies. The complexity of packages needed by high-power digital SoC is huge if compared with consolidated packages used in automotive like QFPs. A combination of reliability pitfalls is implicit with advanced packages because of the mix of materials, processing technologies, mechanical and thermal factors they are featuring. These are samples of the signs arising from the quiet revolution running in our SoCs for automotive, which will be further discussed

along with possible implications with usual test steps at wafer, package and system level.

# Outline

- STMicroelectronics introduction

- Business data and products

### **Digital products**

- Smart driving, autonomous driving, safety, connected vehicles

- Architectures, relevance of data processing

- Automotive transformation

News

- Automotive roadmap

- Impact on testing technologies: overview

- Effects on front-end testing

- Effects on back-end testing

- Equipment, DFT and testing flows

# STMicroelectronics 4

- Among the world's largest semiconductor companies

- Serving over 100,000 customers across the globe

- 2018 revenues of \$9.66B, with year-on-year growth of 15.8%

- Listed: NYSE, Euronext Paris and Borsa Italiana, Milan

- Signatory of the United Nations Global Compact (UNGC), Member of the Responsible Business Alliance (RBA)

~46,000 employees worldwide

~ 7,400 people working in R&D

11 manufacturing sites

Over 80 sales & marketing offices

As of December 31, 2018

# Automotive and Technologies Trends

# Automotive Smart Driving **Megatrend Convergence**

### **Electric Vehicles**

10cent/Km as mobility cost target

40% Electrified Vehicles by 2021

-35% CO2 by 2030

Zero Emission by 2040 in City Zero Net Emission by 2050

Multiple vehicle configurations to support multiple mobility needs (Hybrid, Plug in, Electric, Fuel cells...)

New Digital Architecture to Enable Software Reconfigurable vehicles

Data enabled services are estimated to provide ~30% of Car Makers revenues by 2030

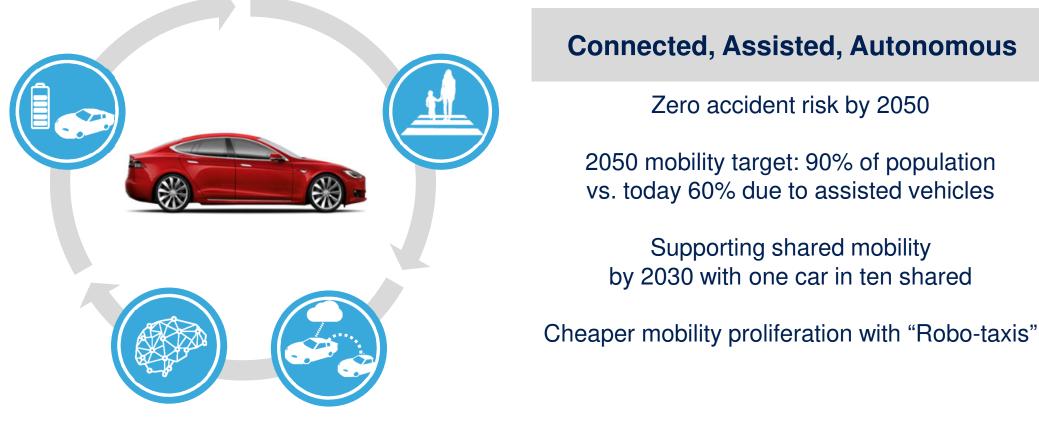

# Active Safety and Autonomous Driving Several Developments to Increase ST Silicon Content in ADAS Systems

EyeQ System delivered by Mobileye to WW OEMs

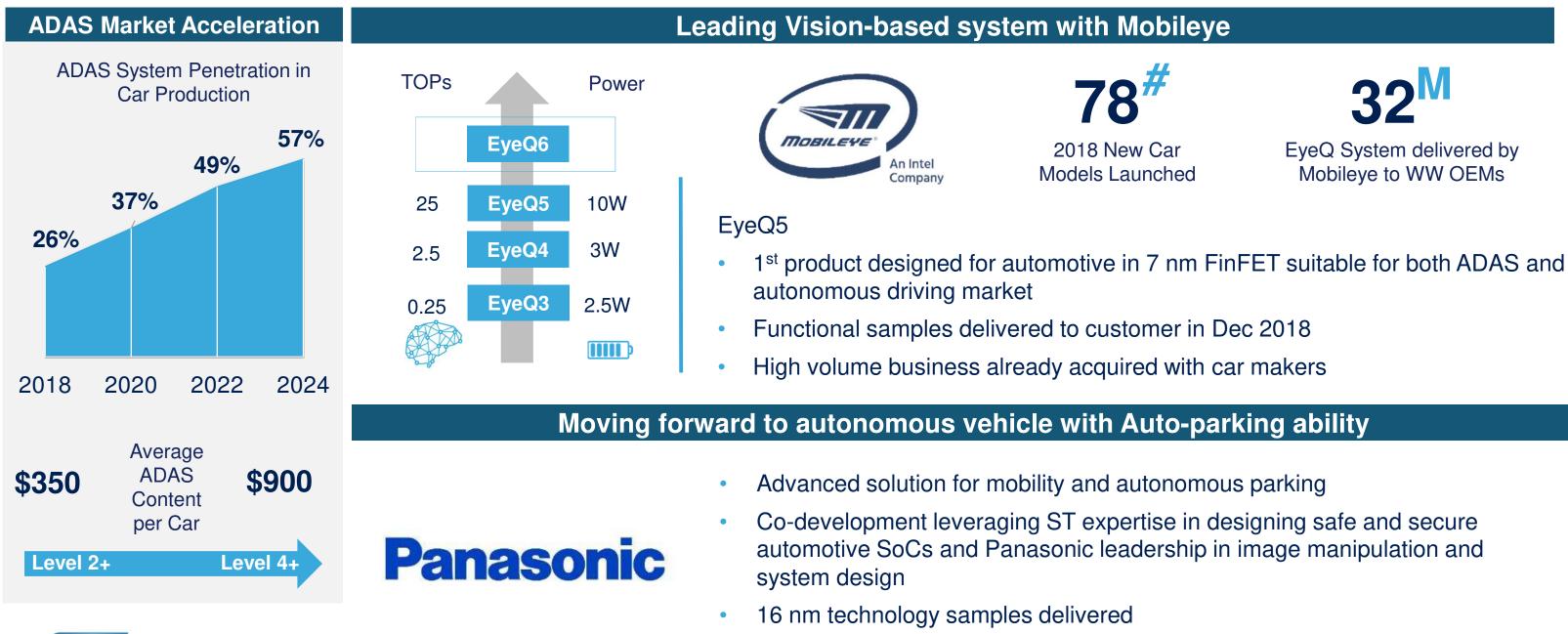

# **Connecting Vehicles** From Wi-Fi-based V2X to Dual Mode Wi-Fi & 5G -V2X

### Market 1<sup>st</sup> dual-mode V2X solution to enable multi-standard connectivity

Wi-Fi 11.p (for Automotive)

(Automotive low latency 5G)

### Market success of the partnership

### Autotalks solution awarded for mass-production:

- 4 of the top 10 automakers plan to deploy our V2X solution Over 10 Tier1s awarded the chipset Start of Production by 2020

### Car Digitalization: New Architectures 10 ...Software Accounting for 30% of Vehicle Value by 2030 ST Technology enablers: FD-SOI 28nm with embedded Phase-Change Memory (PCM)

### **Distributed Architecture: 9k DMIPs per Car**

- Local Control Units with up to 130 ECUs/Car (with 8-16-32-bit MCUs) •

- Limited connectivity and in-vehicle data-flow (up to 10 Mbit/s) ٠

- Heavy and expensive harness ٠

- Extremely complex car Software management

- No car functionalities upgrade •

### Integrated Real-time Domain Architecture: 90kDMIPs per Car

- ~5 Domain-Control Units with higher power computation

- per second

- Architecture simplification, SW rationalization, harness drastic reduction

- Easy car functionality reconfiguration and SW upgrades

- High-speed in-vehicle communication

- Over-the-Air Software upgrade capability

• Stellar with multiple Arm® Cortex®-R52 cores embedded Phase-Change Memory (PCM)

• Autonomous Driving Super-computer (MPU ext. Memory) ~100 Trillion Operations

# Data Harvesting in Automotive

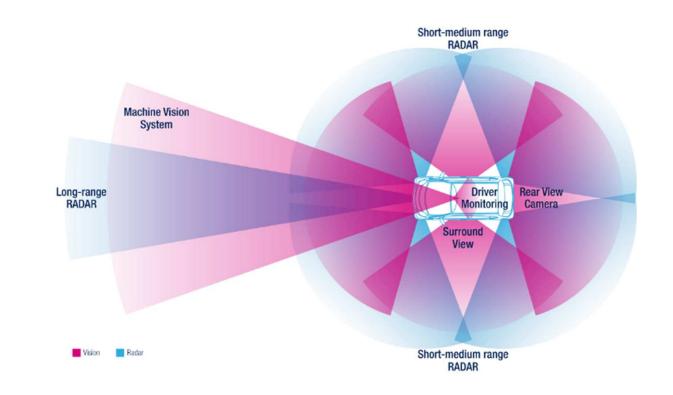

### Vehicle sensors for assisted driving

- High-definition cameras

- High-precision positioning

- Long-range Radar

- Time-of-Flight Lidar

life.auamented

Vehicle dynamics gyroscope & accelerometers

### What latest semiconductor sensor technology nodes bring

- Higher accuracy in sensing

- New sensor type capability at acceptable cost

- Higher performance

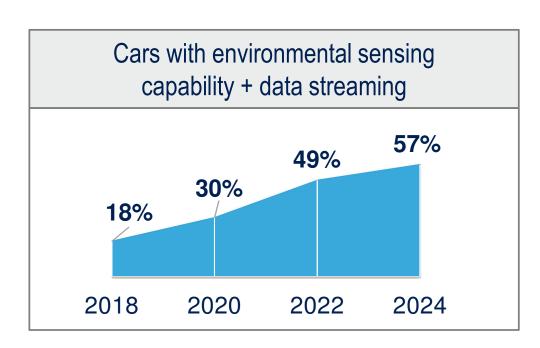

High performance digital processors with AI accelerators enable metadata extraction from raw data

To reduce data to transferred and make continuous streaming cost efficient

(\*) Strategy Analytics, internal data

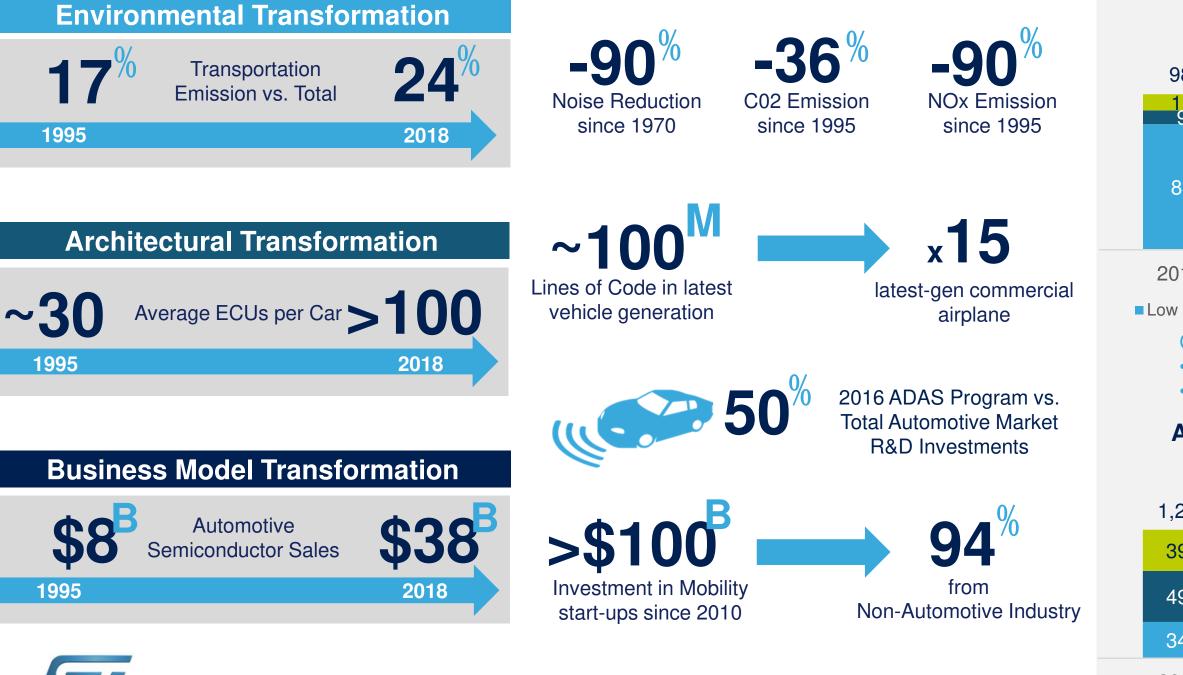

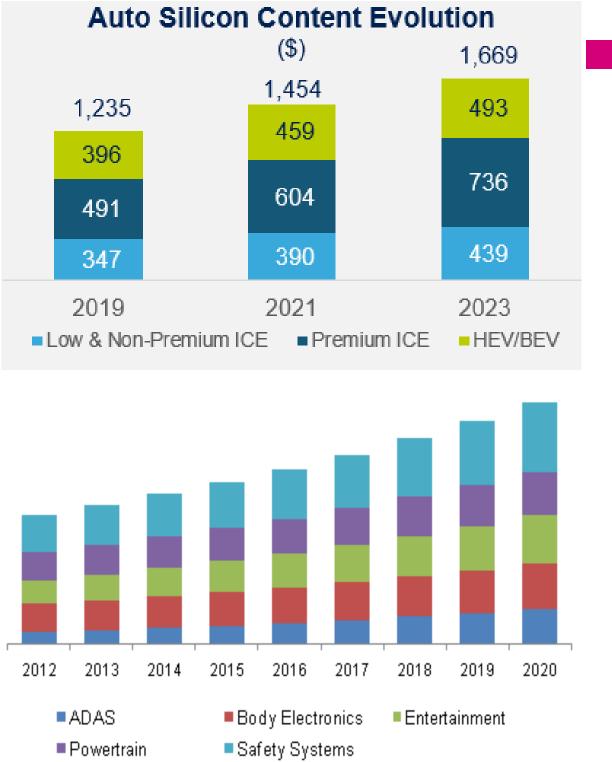

### Automotive Transformation 12 **Worldwide Car Production** (Million units) -36% 109 103 98 21 15 C02 Emission NO<sub>x</sub> Emission 8 8 since 1995 since 1995 80 80 80 ×15 2021 2019 2023 latest-gen commercial Low & Non-Premium ICE Premium ICE HEV/BEV airplane Content evolution driven by Electrified car volumes (24% CAGR) ADAS (16% CAGR) 2016 ADAS Program vs. **Total Automotive Market Auto Silicon Content Evolution R&D** Investments (\$) 1,669 1,454 493 1,235 459 396 736 604 from 491 Non-Automotive Industry 439 390 347 2019 2021 2023 ■ Low & Non-Premium ICE ■ Premium ICE HEV/BEV

Source: Automotive news, McKinsey center of future mobility, Strategy Analytics, ST Internal

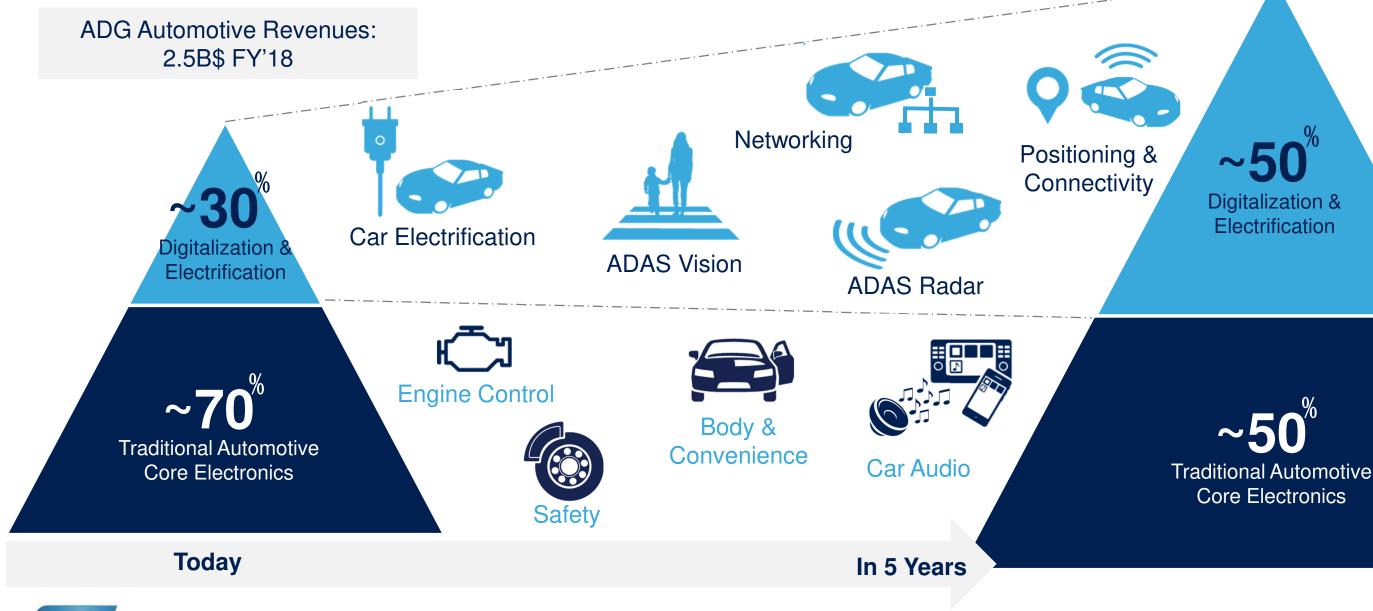

# **ADG Automotive Business Evolution Digitalization & Electrification Driving ADG Growth**

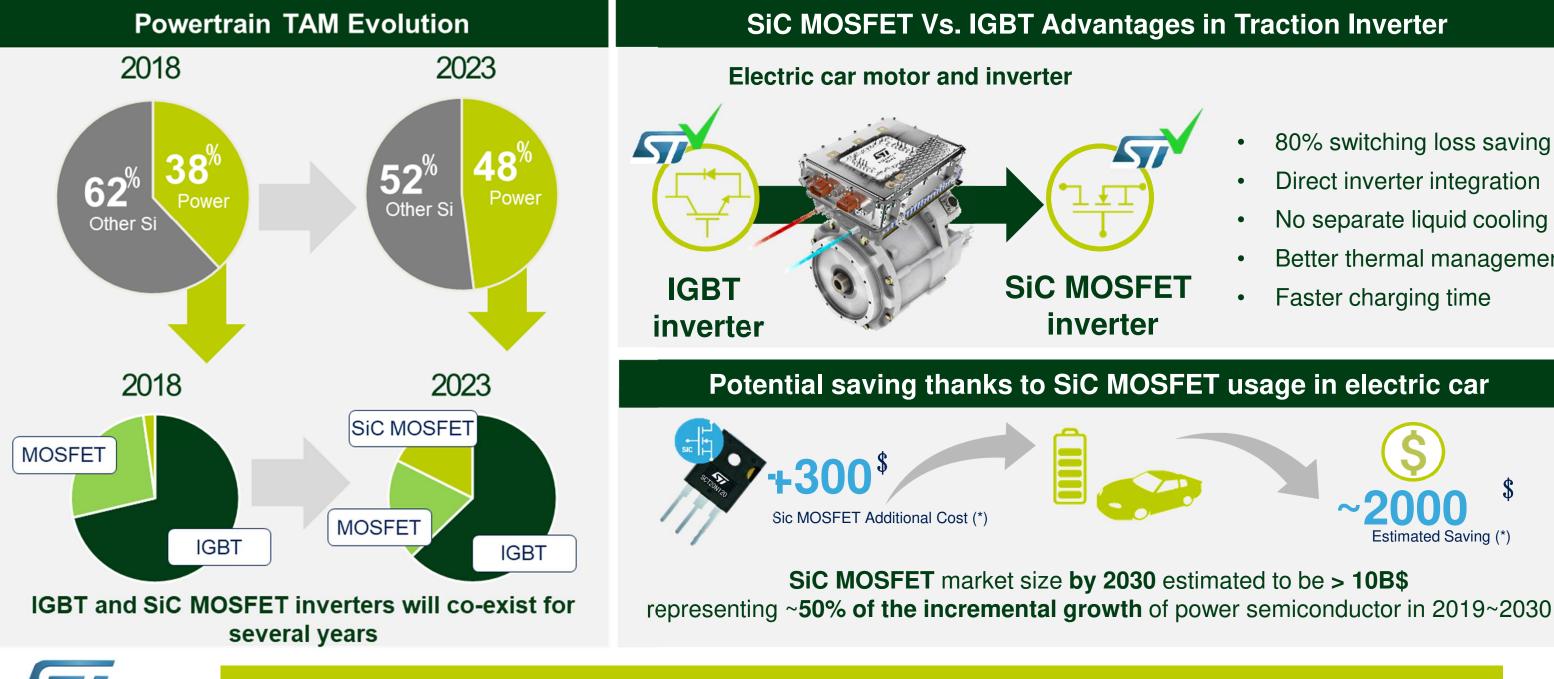

# Car Electrification Boosts Power Content

ST has the full technology and product offer to support the two solutions

(\*) Source: Goldman Sachs

- Direct inverter integration

- Better thermal management

life.augmented

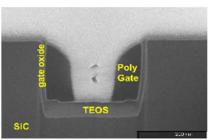

# **ST Silicon Carbide**

### **Next Gen**

### **Trench Technology**

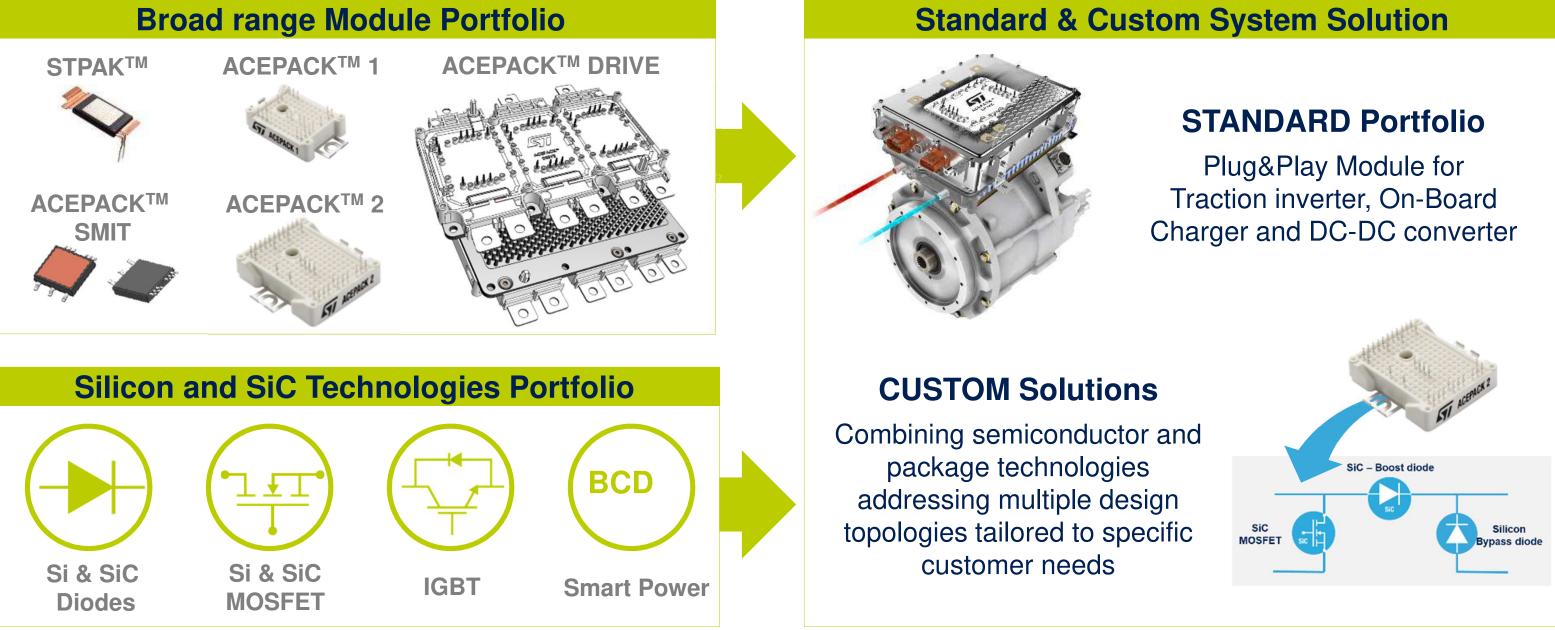

# **Power Modules**

# Standard & Custom Solutions Targeting Market Leadership

# Testing technology: Key factors from the roadmap

# Key Factors

- Functional Safety

- Security

- Increased silicon content

- Few premium ASP devices

- Access to very advanced technologies

- FinFet, PCM, advanced packaging

- High-speed interfaces and RF integration in SoC/SiP

# FE and BE

Wide temperature range Large probed area Small pad opening Small pitch

> Bonding complexity, electrical detectability of multiple wires,

High temperature, pad damaging, multiple touch, highparallelism

> Reliability of bump/substrate joint, material stack stability, warpage effects on large packages, white bumps

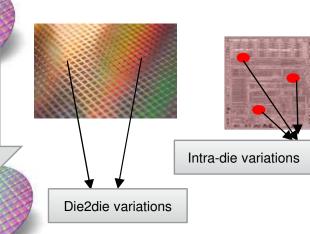

- Interaction performances between IP1 and IP2 may be un-predictably modulated in some PVT spots

- Performances of two IP1 instances in the SoC might be anomalously modulated by intra-die variations

# Electrical

# Economical

20

# Quality

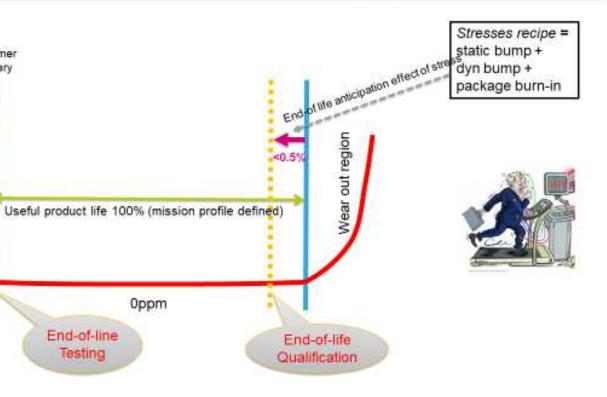

### **Extended Quality Paradigm**

- The level interaction between ICs of the same ecosystem increases the quality and safety challenges

- Key elements: IC level, system level diagnostic and software

### **Challenges:**

Early life fails

region

Stress

reope application

Ly/

Customer

delivery

EWS

ulletlithography reduction

End-of-line

Testing

0ppm

- •

- Early life fail assessment

# Reliability

### 21

### **Qualifying Stress Tests**

### Progressive relative reduction of overvoltage allowing device functionality along with

Complex evaluation of effects across PVT

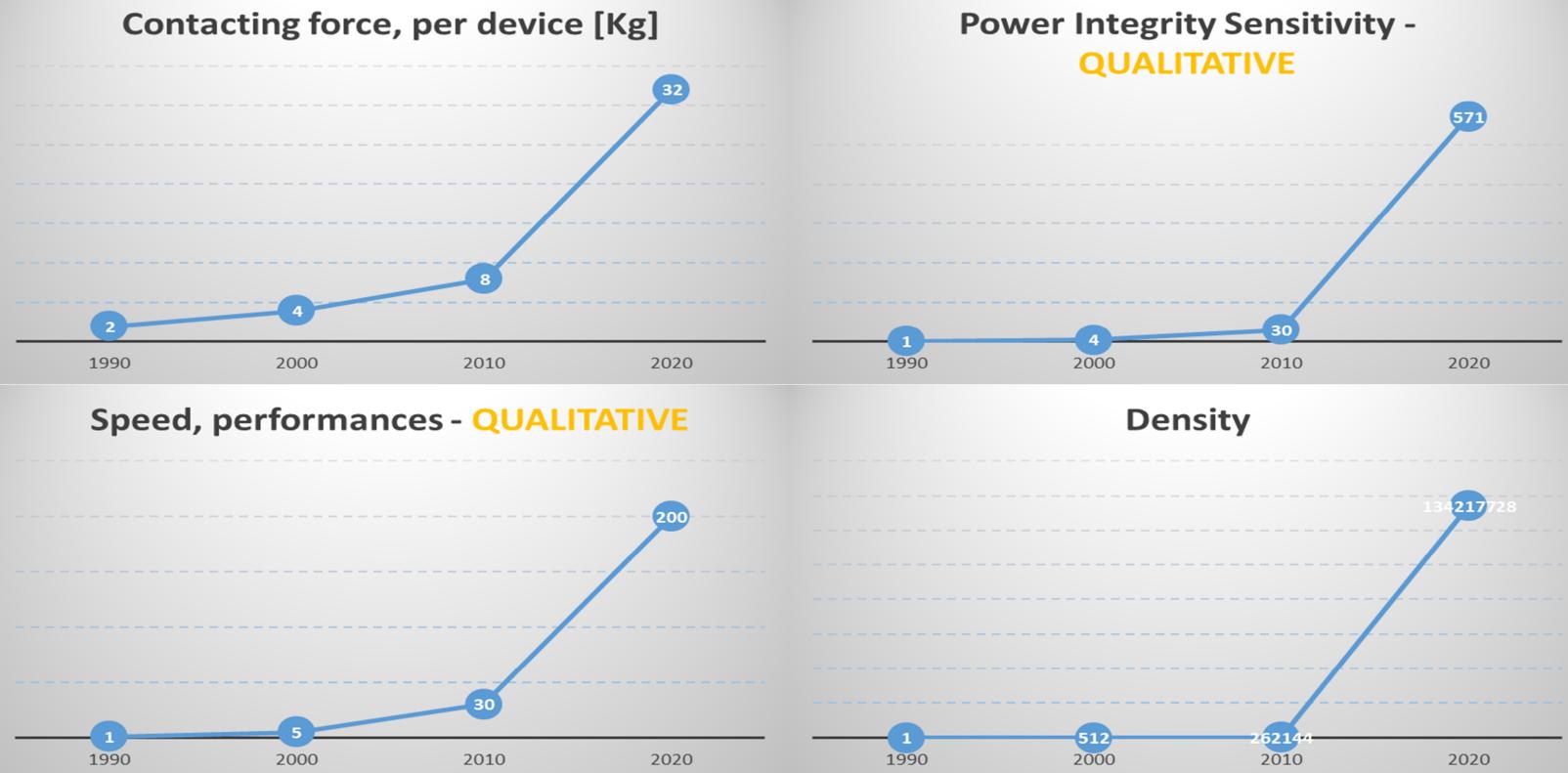

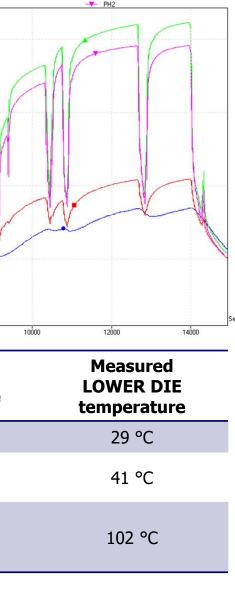

# Factors Trend

# Impacts examples

# Key factors

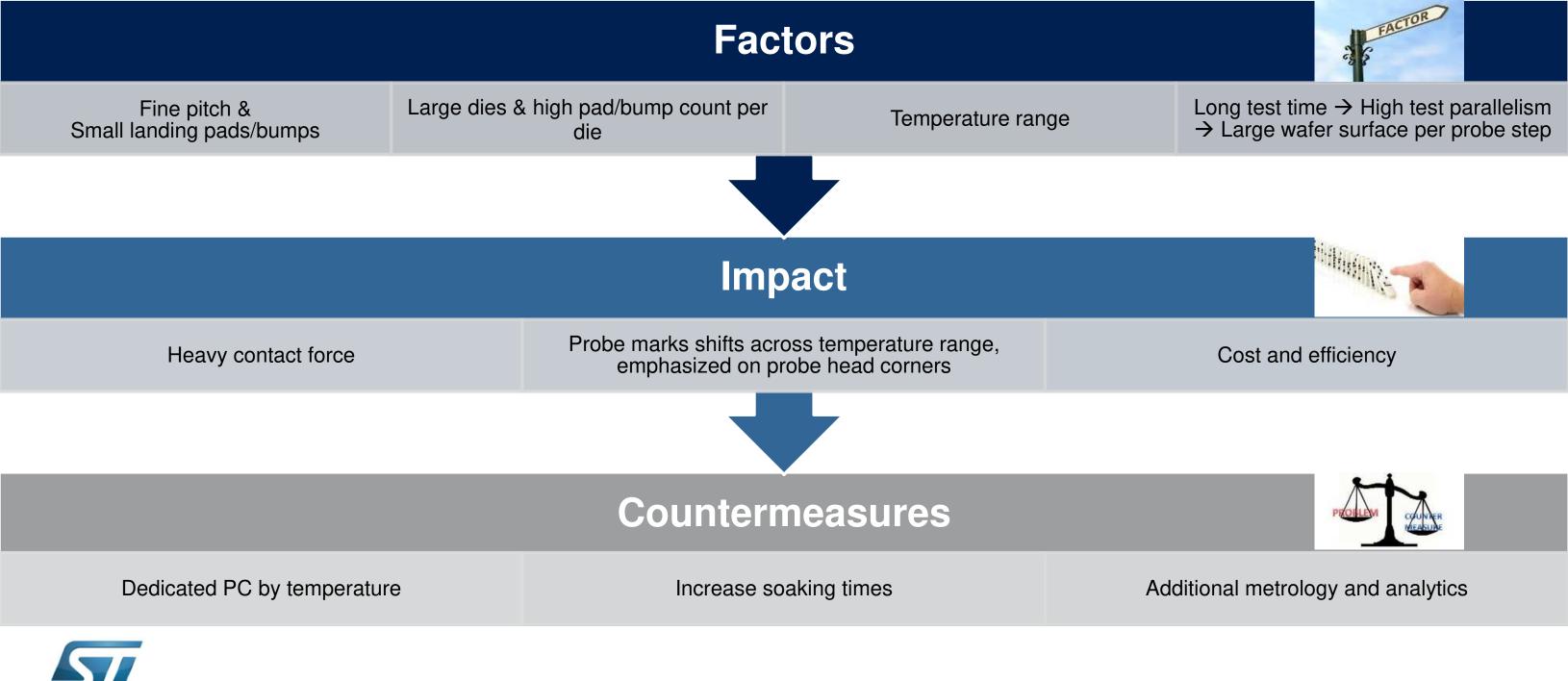

# Impact on front-end probe

- Challenge statement

- Automotive Customers are requiring more and more large array PHs to work over extended T ranges, from cold to hot.

- In case of small pad opening, probe marks shifts at the extreme corners of the array can become critical

INNOVATION BEGINS WITH US

ROBE HOLDING SpA. No part of this document may be copied, reprinted or reproduced in an or methods or tech efore must not be disclosed to any other person or company or entity

- Confidential

Source: Technoprobe, SpA with permission

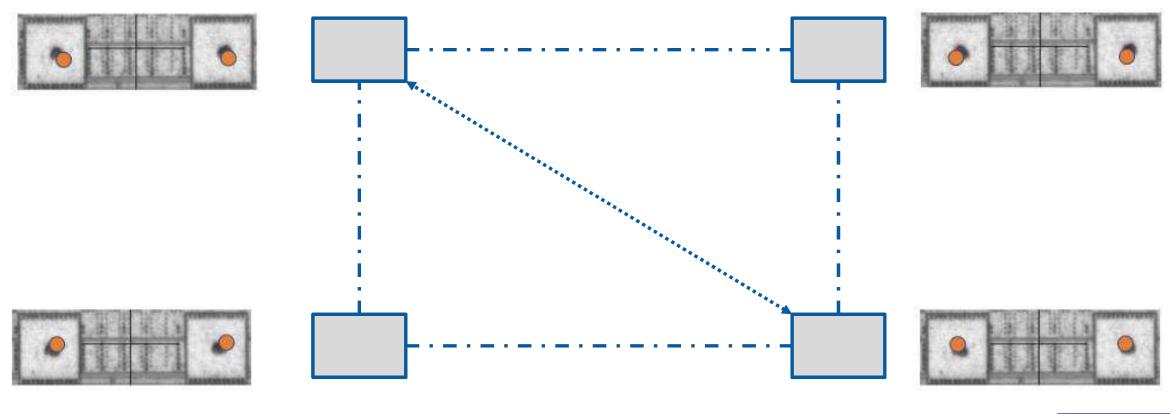

### High T Large Array for Automotive grade **Root cause analysis and problem mitigation**

- Probe marks shifts between cold and hot probing are mainly related to:

- Temperature mismatch between lower ceramic plate and wafer

- Thermal expansion coefficient (CTE) mismatch between lower ceramic plate and wafer

- Problem mitigation

- Temperature mismatch can be minimized by means of optimized soak time procedure

- Band guard should be modified in function of pad opening

- In case of PH active area with a diagonal above 100 mm typical solutions are:

- Dedicate a PC for cold/RT and one for RT/Hot, with corrected coordinates

- Evaluate new plate materials with higher CTE to cover the whole probing T range

No part of this document may be copied, reprinted or reproduced in

### - Confidentia

Source: Technoprobe, SpA with permission

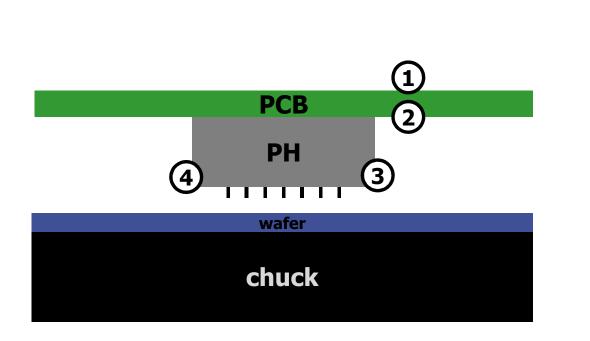

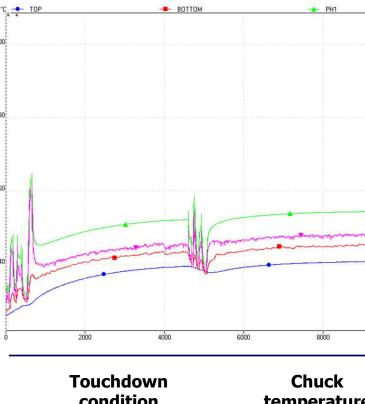

- Thermocouples are installed to monitor temperature:

- 1. Bottom PCB

- 2. Top PCB

- 3. PH @ lower die n°1

- 4. PH @ lower die n°2

| condition               | temperature |  |  |

|-------------------------|-------------|--|--|

| RT                      | 30 °C       |  |  |

| HT<br>Without soak time | 135 °C      |  |  |

| HT<br>With soak time    | 135 °C      |  |  |

INNOVATION BEGINS WITH US All rights reserved. The COPYRIGHT of this document is property of TECHNOPROBE HOLDING SpA. No part of this document may be copied, reprinted or reproduct or methods or techniques contained herein are CONFIDENTIAL, therefore must not be disclosed to any other person or company or entity.

### - Confidential

Source: Technoprobe, SpA with permission

# Impact on back-end manufacturing test

life.augmented

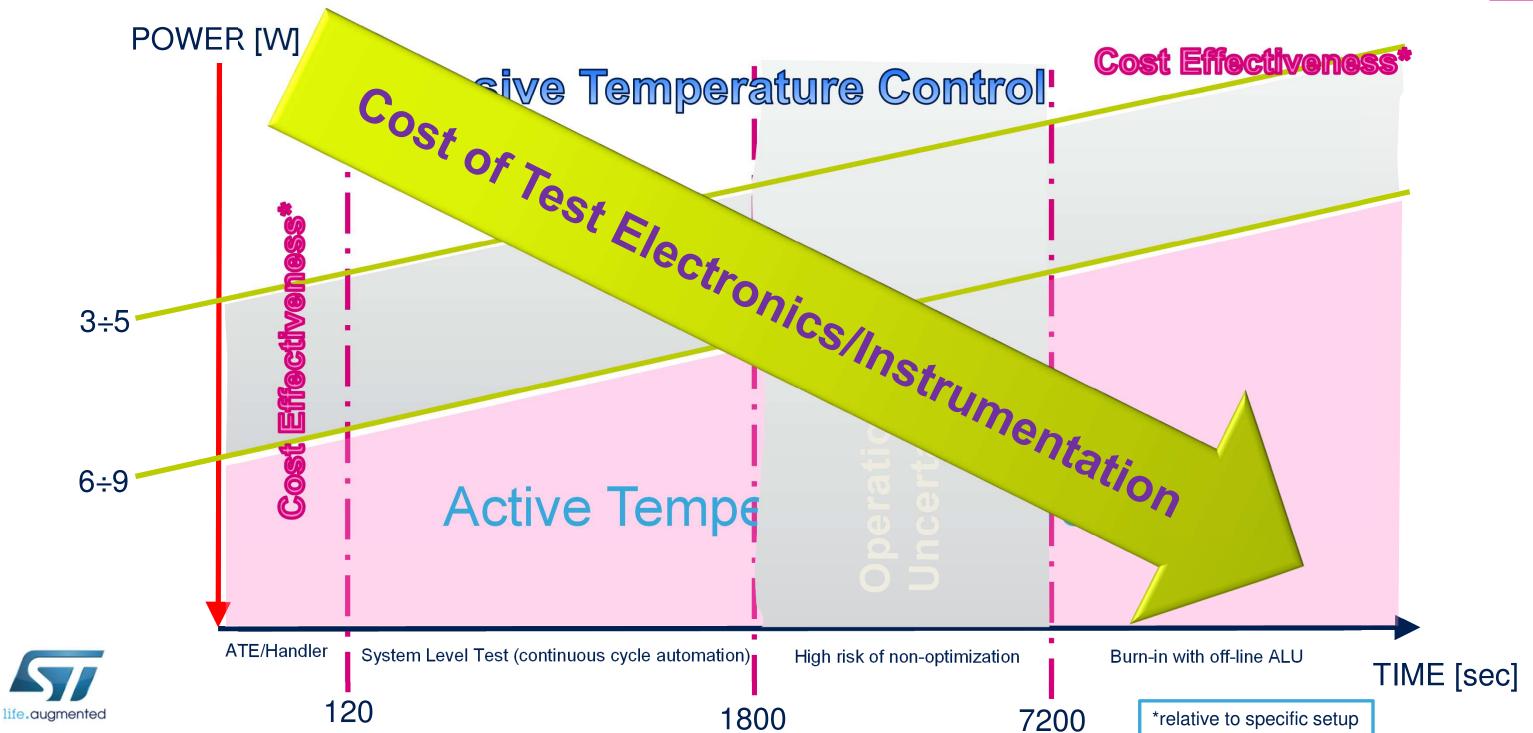

# Power Vs test time: choosing the best equipment

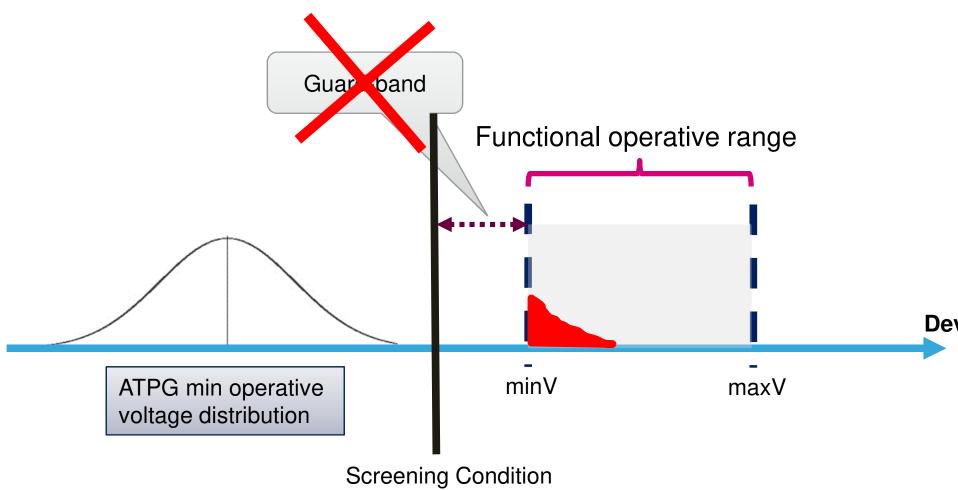

# Effects of variability

Device Supply Voltage

# Qualitative Coverage Analysis

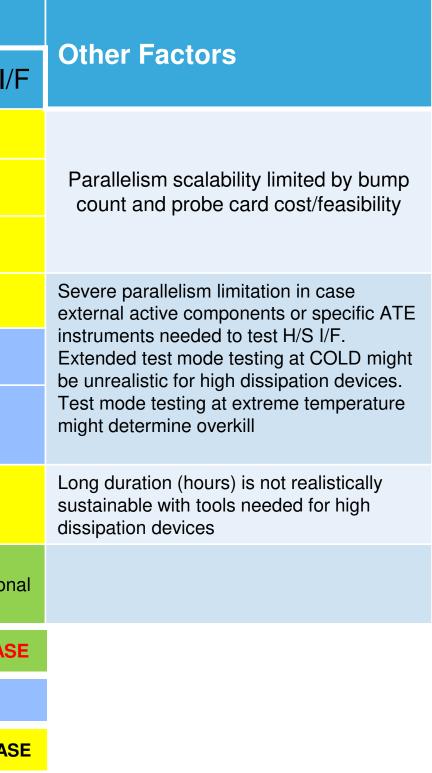

|               |             | Tradeoff                                                        | Coverage                                                                                 |                                  |               |          |

|---------------|-------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------|---------------|----------|

| Stage         | Temperature | Pro's                                                           | Con's                                                                                    | Logic & memories                 | Parametric    | H/S I/   |

|               | COLD        | Low static consumption                                          |                                                                                          |                                  |               |          |

| Wafer<br>sort | ROOM        | Less demanding industrial setup                                 | Not WC condition for majority of<br>known failure modes                                  |                                  |               |          |

|               | НОТ         |                                                                 | Probe limitations, high static consumption                                               |                                  |               |          |

|               | COLD        |                                                                 | Low efficiency and high cost industrial setup                                            |                                  |               |          |

| Final<br>Test | ROOM        | Less demanding industrial setup                                 | Not WC condition for majority of known failure modes                                     |                                  |               |          |

| 1651          | НОТ         | Best case for activation of most known package/assembly defects |                                                                                          |                                  | Ad hoc        |          |

| Burn-in       | ROOM→HOT    | Relatively low cost for <5W devices, with hours duration        | Costs not scalable for devices dissipating >5W                                           |                                  |               |          |

| SLT           | Multi-temp  | Exercise device in true functional conditions                   | Analytical coverage estimation<br>not available for any fault model<br>beside functional | Functional                       | Functional    | Functior |

| COLD = -45°C  |             | ROOM = 25°C to 40 °C HOT ≥ 125°C                                |                                                                                          | Screening effectiveness BEST CAS |               |          |

|               |             |                                                                 |                                                                                          |                                  | NEUTRAL       |          |

|               |             |                                                                 |                                                                                          | Screening ef                     | fectiveness W | ORST CAS |

life.augmented

Screening effectiveness WORST CASE

31

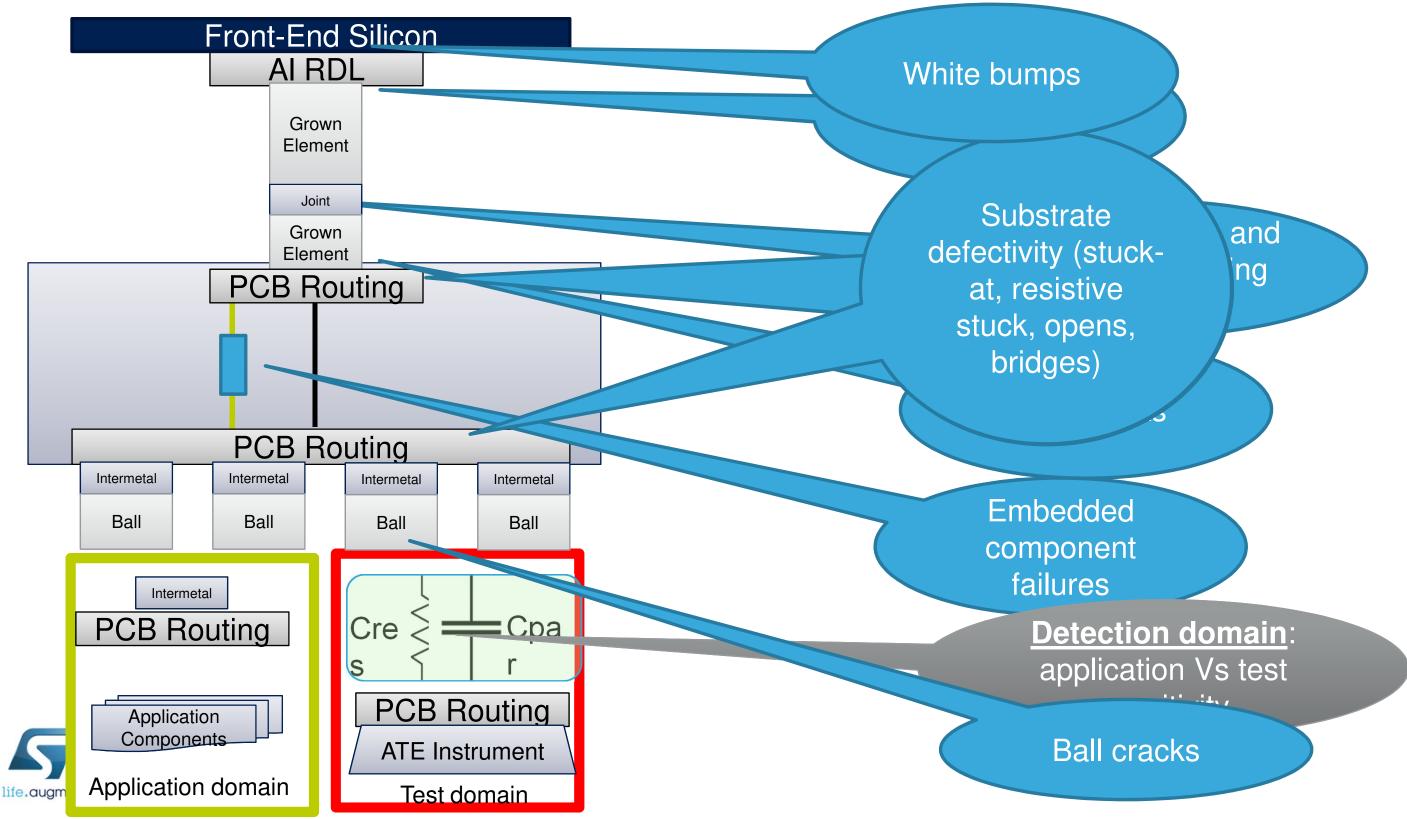

# Impacts examples: a special focus on Package Technology

# Key factors

# Package complexity: an empirical ranking

| Node                       | Unit | 90nm   | 65nm   | 40nm     | 28nm            | 16nm  | 7nm   |

|----------------------------|------|--------|--------|----------|-----------------|-------|-------|

| Power                      | W    | 1      | 2      | 3        | 6               | 20    | 100   |

| Speed                      | MHz  | 200    | 250    | 500      | 1600            | 2200  | 3600  |

| Dominant Package<br>type   | -    | QFP    | eQFP   | eQFP/BGA | FCBGA           | FCBGA | FCBGA |

| Dominant Pad<br>technology | -    | Al Pad | Al Pad | Al Pad   | Bumps / pillars | SB/CP | SB/CP |

| Package complexity index*  | -    | 1      | 2      | 2        | 5               | 6     | 7     |

Qualitative, considers signal count, bonding technology, materials, mission profile

### Package-level Testing Challenges: defect modelling

34

# FCBGA Defect Classification

| Defect Description              | Reliability<br>Sensitivity | Defectivity<br>Dependence | Fault Model                   | Electrical<br>Detectability |  |  |  |

|---------------------------------|----------------------------|---------------------------|-------------------------------|-----------------------------|--|--|--|

| "White" bumps                   | HIGH                       | HIGH                      | Any Stuck model               | MEDIUM                      |  |  |  |

| Orealia an nillar ailiaan isint | LOW                        | LOW                       | Stuck-open                    | HIGH                        |  |  |  |

| Cracks on pillar-silicon joint  | HIGH                       | LOW                       | Resistive open                | LOW                         |  |  |  |

| Pillar/bump defectivity         | LOW                        | MEDIUM                    | Resistive stuck               | LOW                         |  |  |  |

| Dillor/bump to substrate isint  | LOW                        | LOW                       | Stuck-open                    | HIGH                        |  |  |  |

| Pillar/bump to substrate joint  | HIGH                       | LOW                       | Resistive open                | LOW                         |  |  |  |

| Substrate defectivity           | LOW                        | HIGH                      | Stuck-at, bridge, AC coupling | MEDIUM                      |  |  |  |

| Substrate components presence   | LOW                        | HIGH                      | Stuck-open, resistive open    | MEDIUM to LOW               |  |  |  |

| Ball cracks or opens            | LOW                        | MEDIUM                    | Resistive open                | LOW                         |  |  |  |

High risk: defect might not be active/detectable @ t0

# Extending DFT Scope

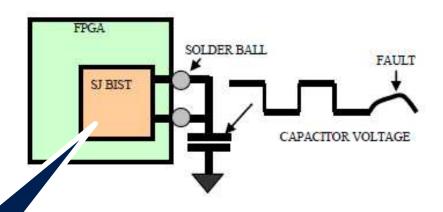

### **Ball Grid Array (BGA) Solder Joint Intermittency Detection: SJ BIST<sup>TM</sup>**

James P. Hofmeister Ridgetop Group, Inc. 3580 West Ina Road Tucson, AZ 85741 (520) 742-3300 hoffy@ridgetop-group.com

Terry A. Tracy Raytheon Missile Systems Bldg. M02, MS T15 1151 Hermans Road Tucson, AZ 85706-1151 (520) 794-3962 tatracy@raytheon.com

Pradeep Lall Dhananjay Panchagade Auburn University Dept. of Mech. Engineering and CAVE Auburn, AL 36849 (334) 844-3424 lall@eng.auburn.edu panchdr@auburn.edu

> Justin B. Judkins Kenneth L. Harris Ridgetop Group, Inc. 3580 West Ina Road Tucson, AZ 85741 (520) 742-3300 justin@ridgetop-group.com kharris@ridgetop-group.com

Norman N. Roth DaimlerChrysler AG Cabin/Power Train E/E 050/G009-BB GR/EEH 71059 Sindelfingen, Germany 49-(0) 7031-4389-398 norman.n.roth@daimlerchrysler.com

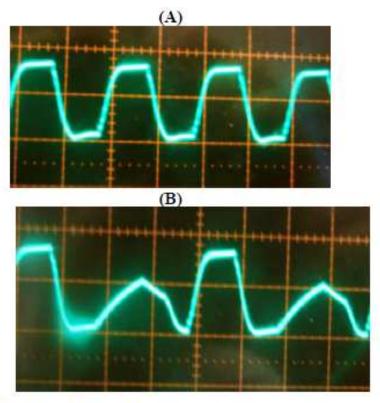

Figure 12: SJ BIST Block Diagram

Figure 13: SJ BIST: 1 MHz Capacitor Signal. (A) No Fault; (B) 100 Ω Fault - 0.5 µs x 2.0V Grid.

2008 IEEE Aerospace Conference

Extending package co-design concept: Add DFT IPs into die design to activate defects localized in the package.

# Impacts on Test Flow

# Key factors

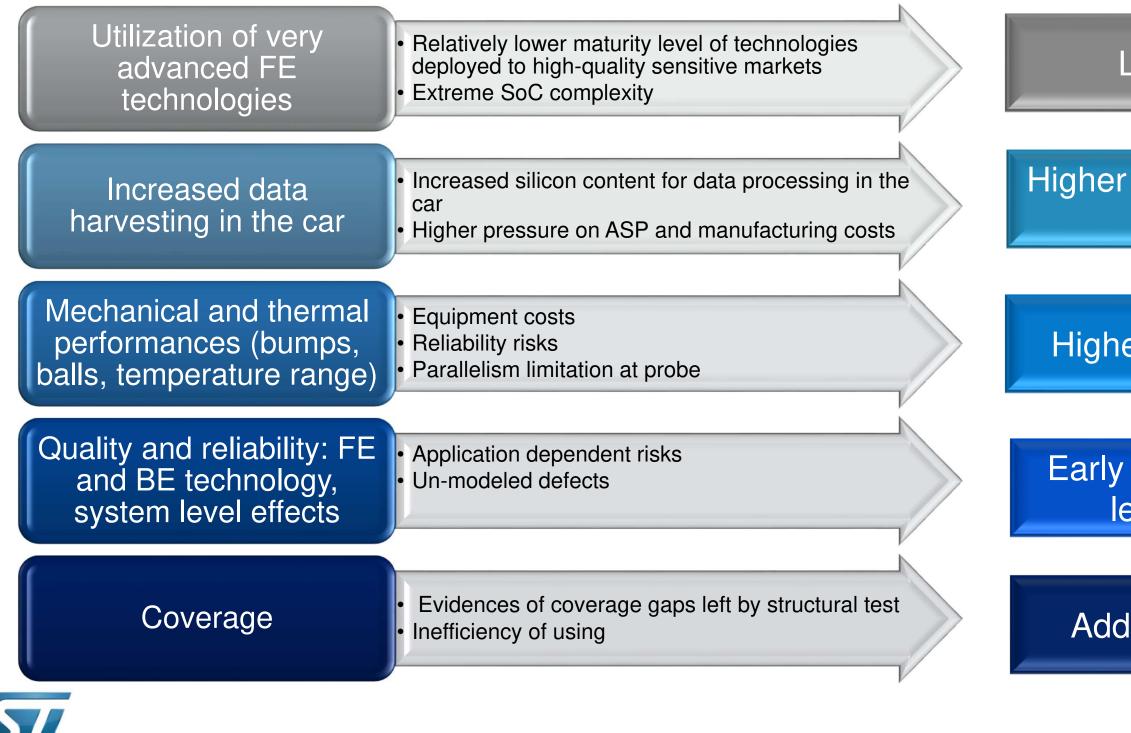

# Cause – Effects diagram

### Longer test time

Higher cost of test impact on device margin

### Higher cost of equipment

Early evaluation of system level marginalities

Additional testing types

### Effects on test flow

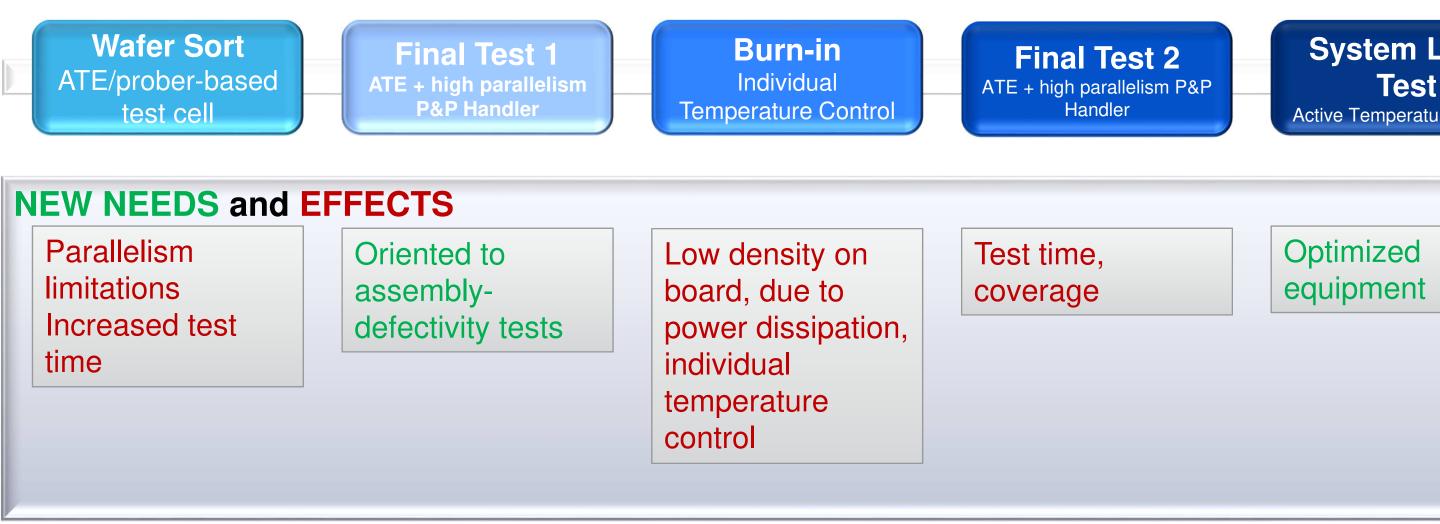

### System Level Test Active Temperature Control

## **Optimizations in The Radar**

**Final Test 1** ATE + high parallelism **P&P Handler**

**Burn-in** Individual **Temperature Control**

**Final Test 2** ATE + high parallelism P&P Handler

### **Optimization directions**

- Remove coverage overlaps

- Exploit similarities to merge requirements into single equipment/stages

- Augmented design for test

### Remove (by understanding...) existing coverage overlaps

### **Proven Massively Parallel Development Path**

Workflow from Single-Site to Massive Parallelism Scale Capacity & Functionality as Needed

## Augmented Design for Test

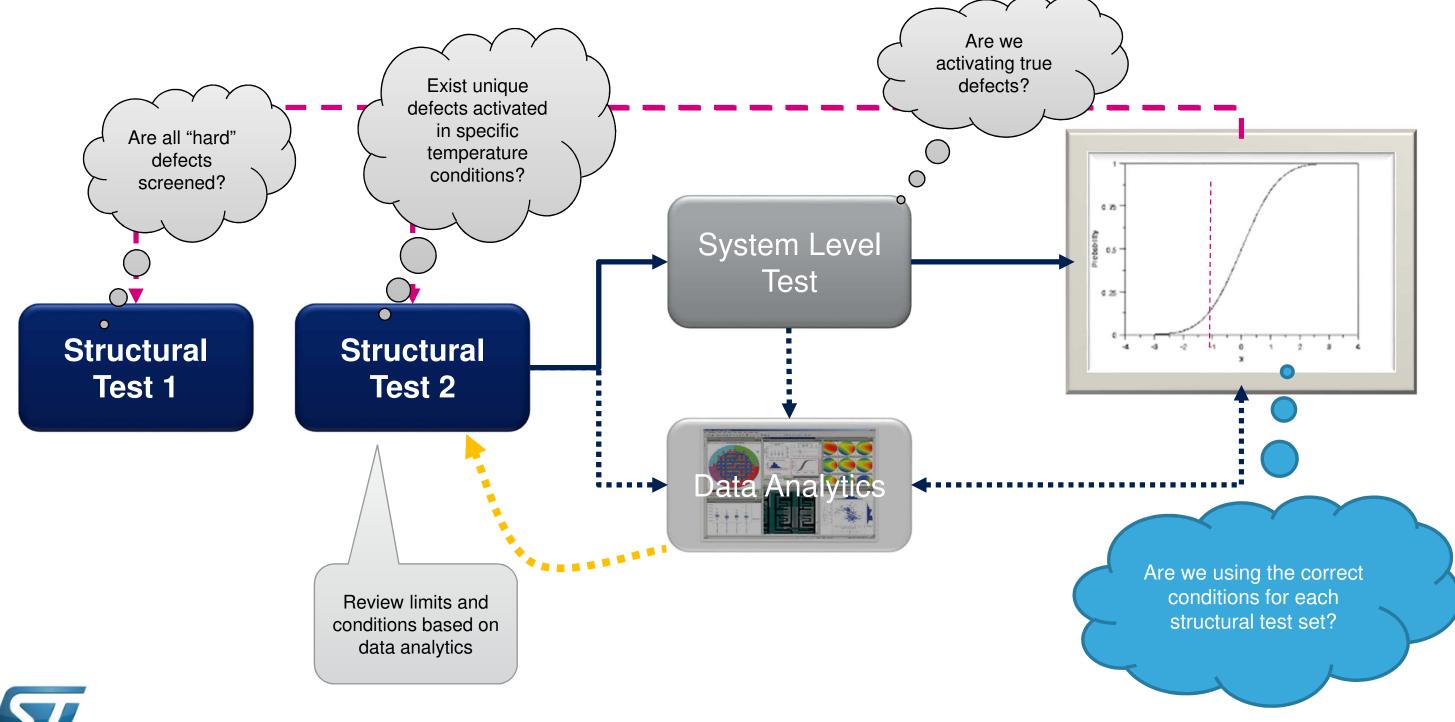

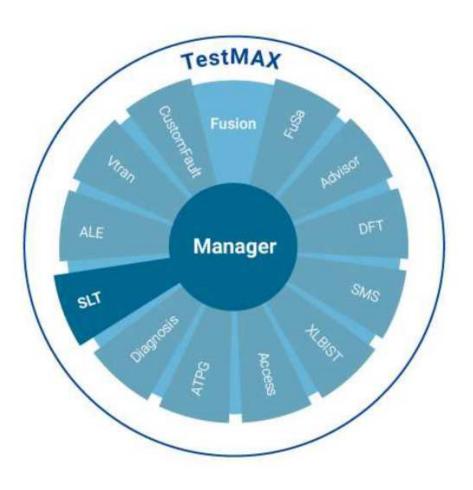

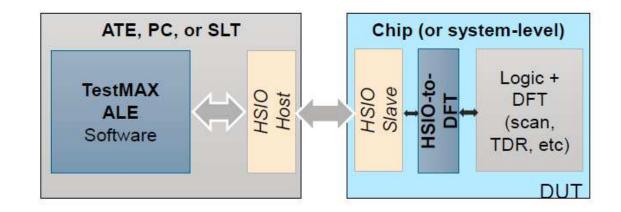

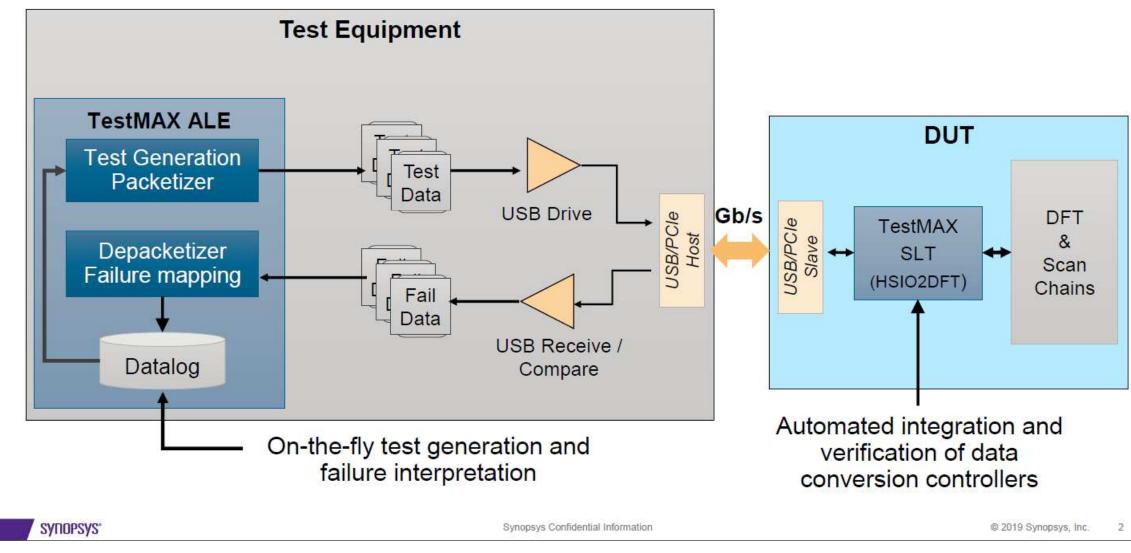

### TestMAX ALE and TestMAX SLT

High-speed / system-level interface for test

- Re-use existing high-bandwidth functional interfaces - USB, PCIe, etc with multi-gigabit data rates

- SLE inserts the HSIO2DFT controller for data format translation (de/packetizing); ALE provides software control

- · Benefits:

Synopsys Confidential Information

- High-bandwidth application helps reduce test time

- Reduces or eliminates need for dedicated test I/O

- Provides portability of tests through the product life-cycle

SYNOPSYS"

Source: Synopsys, Inc with permission

© 2019 Synopsys, Inc. 1

# Accessing DFT through Existing Functional Links

### Adaptive High-Bandwidth Test

Source: Synopsys, Inc with permission

### Take out from the product roadmap:

- Automotive is progressively accessing advanced technologies, sometime beyond what the rest of market segments are doing

- FinFet, SiC

- The roadmap of digital products includes few relevant factors to the test technology needed in the next years:

- Large die size, wide temperature spectrum, ultra-high bump count and long test time, leading to high parallelism needs

- High variability, high number of integrated IP's makes traditional structural test less effective on corners of boundary conditions (P, V. T)

- Package and back-end technologies in general increased their complexity introducing several defect mechanisms, whose detection might not happen only as a side result of testing the silicon

- Increased silicon content in the car puts pressure on ASP

### Factors relevant to the test technology roadmap:

- Silicon technologies

- No evidences of defects which can be activated in unique temperature conditions ٠

- Accurate review of BC/WC screening conditions

- Structural test is weakening progressively its efficiency across PVT:

- Applicative-oriented test considered to complement existing

- Data analytic necessary to minimize coverage overlaps ٠

- Test time duration puts challenges on equipment (performances vs cost)

- Package assembly

- New defects lead by complexity, BOM and manufacturing process ٠

- Possibly needed ad-hoc DFT for an effective screening

### Cost

Adding stages can be prohibitive, merging appears possible