# Reducing Test Costs by Optimizing the Prober Indexing Process

Author/presenter: Ken Walker, Intel Corp.

Contributor: Balbir Singh, Intel Corp.

#### **Reducing Test Costs by Optimizing the Prober Indexing Process**

#### Outline

- Objectives

- Introduction

- Equipment & Procedures

- Results

- Conclusions

- To-do List

#### **Objectives**

Develop means to quickly alter prober "recipes" (Before probe card design)

Quantify & correlate variables affecting index times ->

PREDICTABILITY

• Trim index times & costs

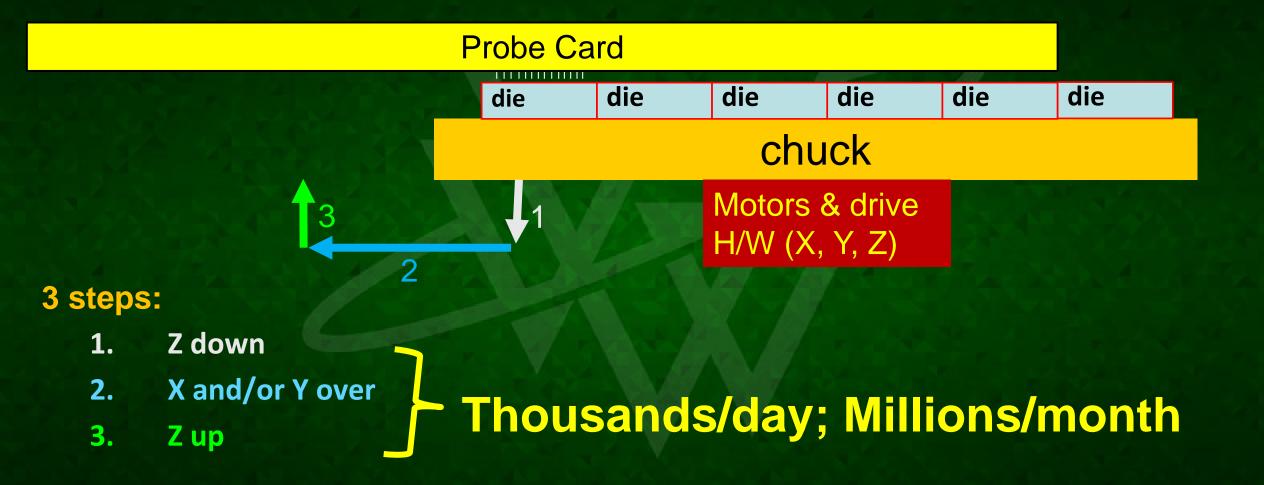

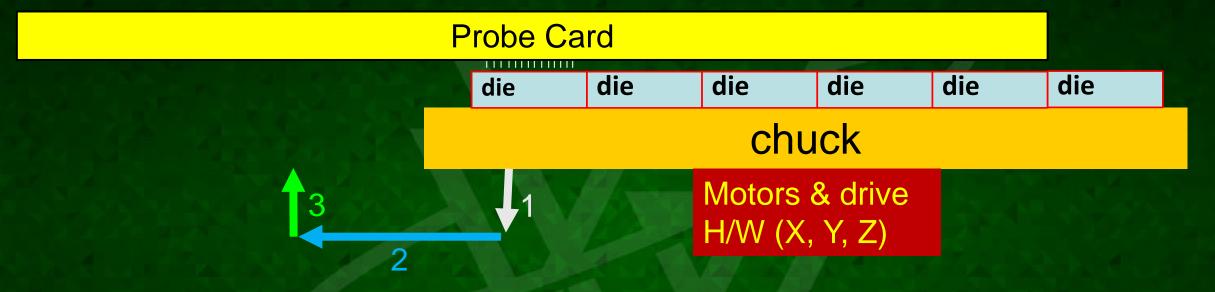

#### Introduction: prober indexing process

# Suspected Variables affecting index time

- Prober X/Y/Z drive H/W & S/W

- Die size & aspect ratio

- Index pattern:

- X-priority

- Y-priority

Author

Diagonal, vortex, etc.

Parallelism: # of sites, configuration, indexing choices

# **Equipment & Procedures**

- 2 probers (300-mm)

- S/W: index instructions ("maps")

- Maps → prober "recipe" file

- Start timer 1<sup>st</sup> die; end last die

NOT included:

- test program

- loading/unloading wafer

- wafer/probe alignment (demo mode); no:

- theta rotation of chuck

- slight stepping in "off" axis

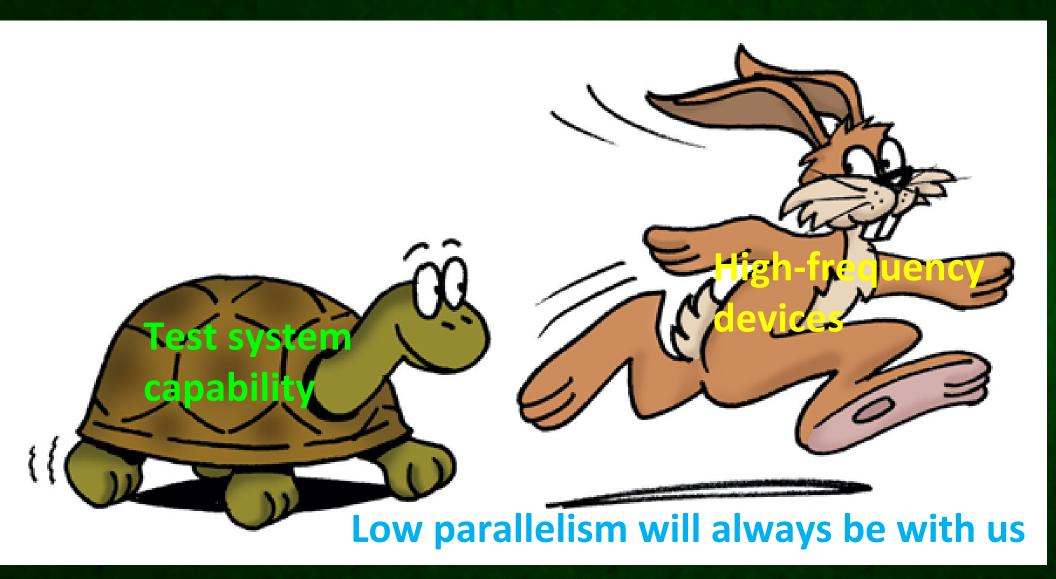

#### Fable? The Tester and the Die

Mostly X1

Some X4

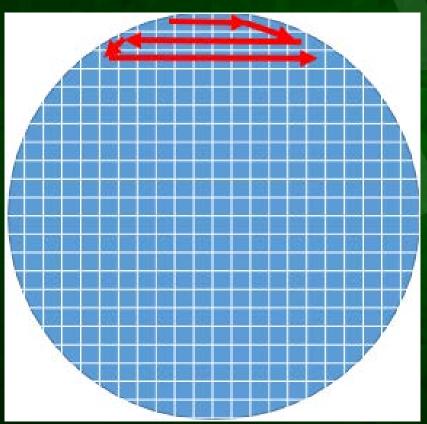

#### **Experiment #1: X vs. Y Indexing**

X indexing: hundreds of X steps; few Y

Y indexing: hundreds of Y steps; few X

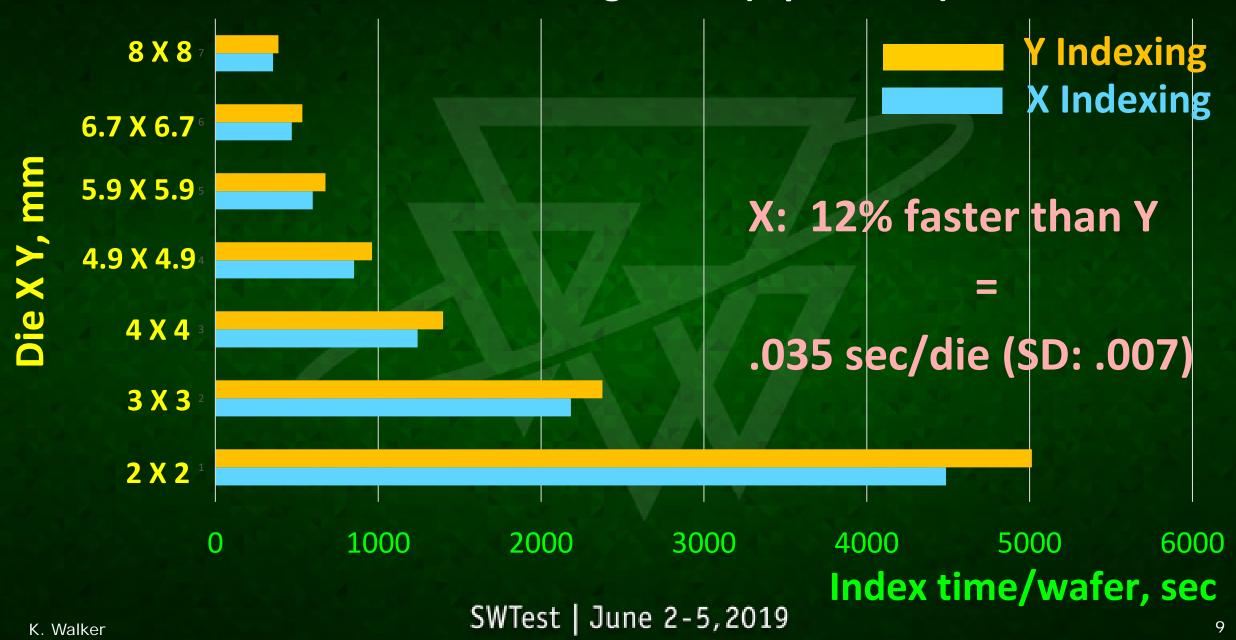

#### X vs. Y indexing times (square die)

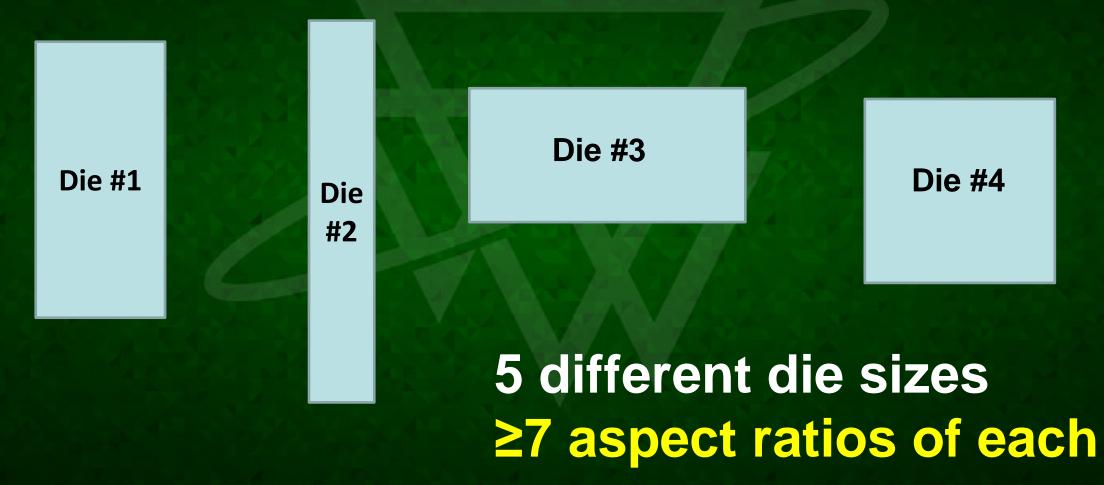

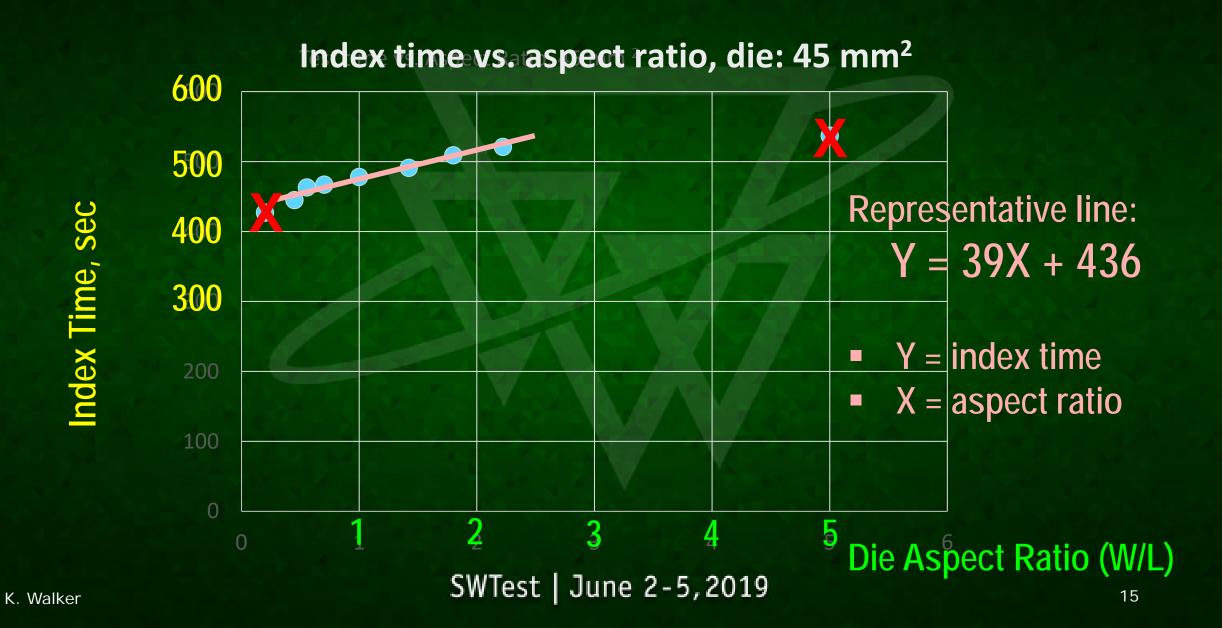

## Experiment #2: Die Aspect Ratio (W/L)

Which indexes faster? By how much? Why? Predictably?

SWTest | June 2-5,2019

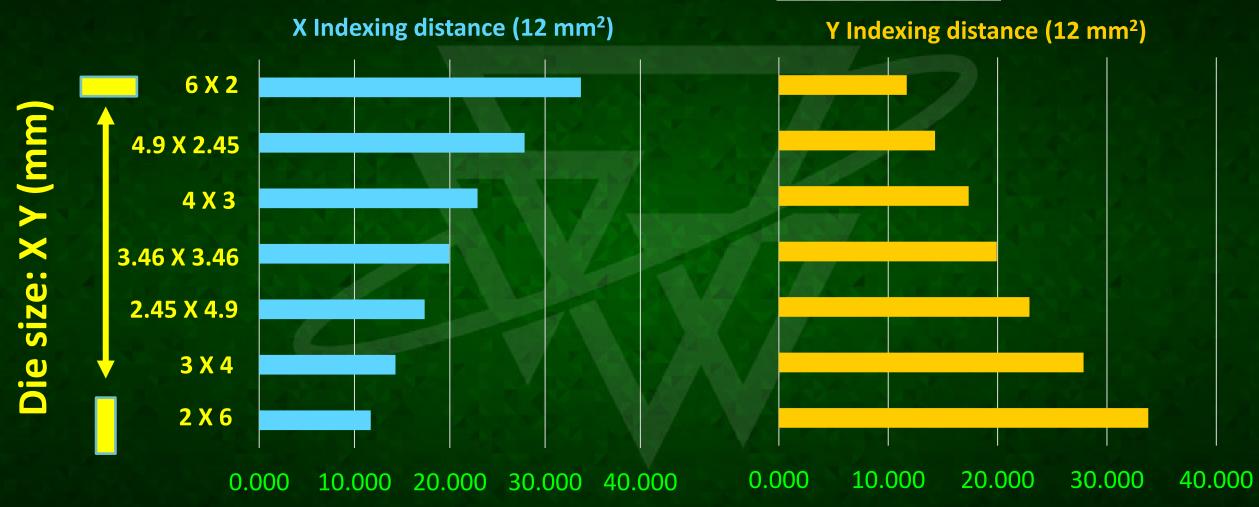

#### Varying aspect ratios (X indexing)

#### **Aspect ratios (Y indexing)**

SWTest | June 2-5,2019

Index time/wafer, sec

# Smaller aspect ratios (W/L) → faster X indexing

Larger aspect ratios → faster Y indexing

WHY??

#### **Indexing Distance (H/W travel)**

Index distance/wafer, m

#### **Predictability**

#### Predictability: trivia for your next social event

If we invert aspect ratio (AR),

- 2:1 to 1:2 AR, index distance drops ~2:1 (X indexing)

- $-3:1 \rightarrow 1:3$ , distance drops ~3:1

- $-4:1 \rightarrow 1:4, ~4:1$

AND... index distance → linear w/ index time – about 1:8.5

Drop distance 1 m → ~8.5 sec

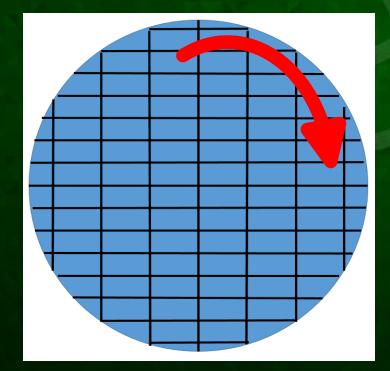

#### Conclusions, Experiment #2

**Since this:**

indexes faster than:

er than:

...design probe card & lay out (or rotate) wafer...

...to index like this

SWTest | June 2-5,2019

### Can't rotate wafer & probe card...?

| Die aspect (W/L) | Test this way:              |

|------------------|-----------------------------|

| < 2              | Xindexing                   |

| ~2               | X or Y (or Vortex) indexing |

| > 2              | Yindexing                   |

### Conclusions, Exp #2

...design die to be less square?

SWTest | June 2-5, 2019

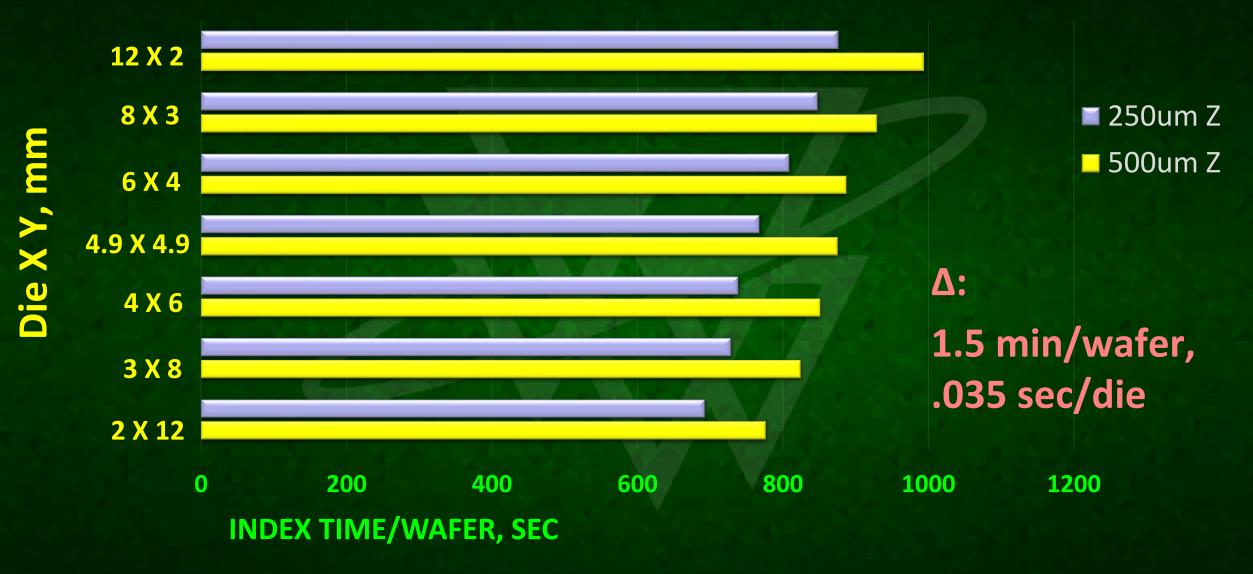

## Experiment #3: Z up/down travel

500 um up/down...

...or 250?

SWTest | June 2-5, 2019

#### Index time by Z up/dn, X indexing

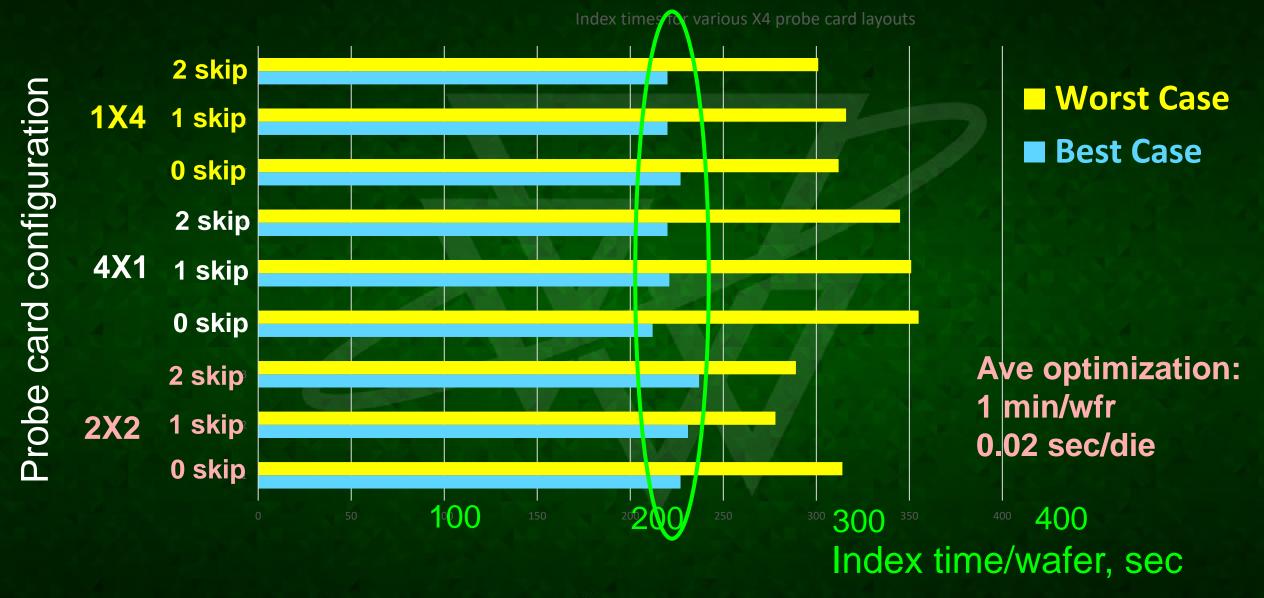

#### Experiment #4: Multi site (24 mm<sup>2</sup> die)

# **Bottom Line (X1 only)**

| Fastest indexing pattern                  | 0.035 sec/die  |

|-------------------------------------------|----------------|

| Rotate wafer/card, Design die less square | 0.040 sec/die  |

| 250 um Z up/dn                            | 0.035 sec /die |

| TOTAL                                     | 0.11 sec/die   |

Run rate: 10MU/yr...

Test cost: \$100-200/hr

Savings: \$40K/yr

# To do...

More work: X2 & X4

Design/Architecture → make die less square?

Test facilities → follow our index maps

Wafer/shuttle layout → short die side perpendicular to notch

Θ rotation & off-axis micro-stepping? (Work w/ probe card vendors to align more to prober axes?)

# Thank you