Opto-electronical probe card for high-volume wafer level test of photonic integrated circuits

Tobias Gnausch JENOPTIK Optical Systems GmbH Jena, Germany

> Hanjo Rhee, PhD Sicoya GmbH Berlin, Germany

**MORE LIGHT**

sicoya

# Content

- Application and background

- General test solution and setup

- Working principle

- Demonstrator

- Lab measurements and feasibility results

- Wafer prober compatibility

- Wafer-level test of EPIC DUT

- Conclusion and Outlook

# **Application and Market requirements**

# UFO Probe<sup>™</sup> - <u>ultra-fast opto-electronic probe card</u>.

JENOPTIK developed a solution for high-volume wafer level test of photonic integrated circuits (PIC) for optical transceivers.

What's the driver?

| data | center | • |

|------|--------|---|

|      |        |   |

Higher data rates

Optical communication.

PIC as core component.

Connected World

# **Application and Market requirements**

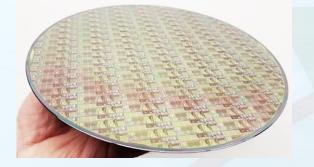

## Fabrication of photonic integrated circuits in CMOS technology

CMOS Wafer

Electronic Photonic Integrated Circuit

Optical ASIC or Module

- The PIC ecosystem is still under development. It needs to

- align with CMOS fabrication chain,

- meet current industry standards,

- reduce costs!

→ Opto-electronical testing plays a vital role!

Tobias Gnausch, 11/11/2020

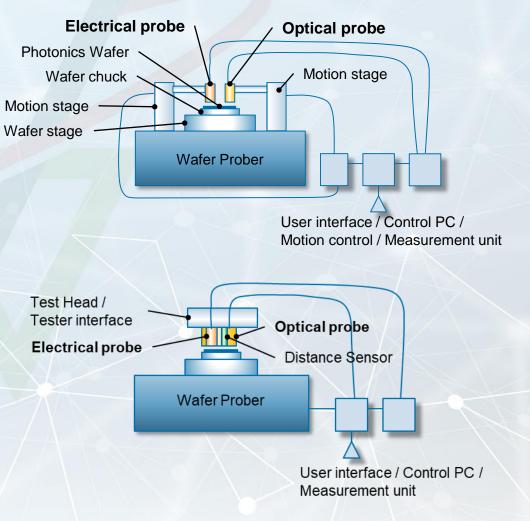

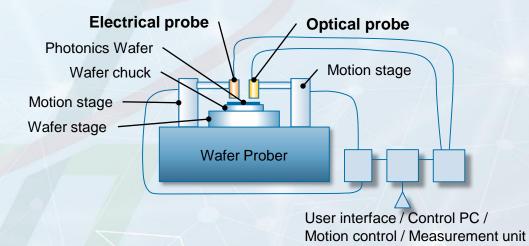

# **Current and Ideal Wafer Level Test Solutions**

#### **Current solutions**

- Fiber based

- Active alignment in sub-micrometer range

- Separated probes electrical and optical

- Dedicated or customized probing equipment

- Little to no possibility of parallelization

#### Ideal solution

- Plug & Play ready for existing standard IC wafer probers and automated test equipment

- No active alignment time per chip

- Parallel qualification → multi-DUT regime

- Operated by same personnel as standard IC equipment

# **Current and Ideal Wafer Level Test Solutions**

#### **Current solutions**

- Fiber based

- Active alignment in sub-micrometer range

- Separated probes electrical and optical

- Dedicated or customized probing equipment

- Little to no possibility of parallelization

#### Ideal solution

- **Plug & Play** ready for existing standard IC wafer probers and automated test equipment

- No active alignment time per chip

- Parallel qualification → multi-DUT regime

- Operated by same personnel as standard IC equipment

#### Consequences

- optical and electrical probe in one probe card

- Compatible to existing interfaces

- Deal with ,coarse' prober alignment tolerances

- Optics that works alignment insensitive

- Scalable solution with simple handling

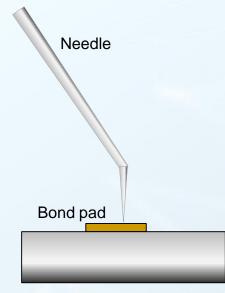

# **Working Principle**

**Big Question:**

• How to get ELECTRICAL and OPTICAL probes together?

Wafer / DUT

Micrometer position tolerance at bond pad

Sub-Micrometer position tolerance at grating coupler

Tobias Gnausch, 11/11/2020

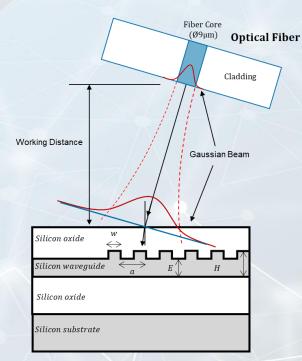

# **Working Principle**

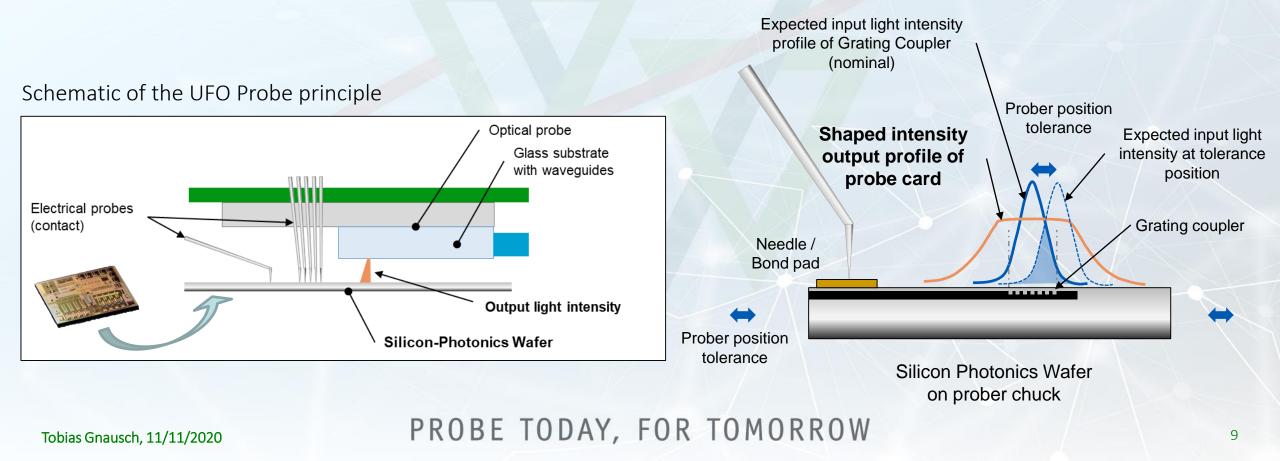

#### Challenge of an opto-electronical probe card:

• Realize an alignment insensitive optical probe.

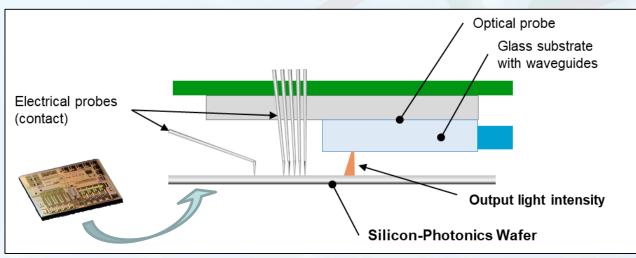

#### Schematic of the UFO Probe principle

# **Working Principle**

#### Challenge of an opto-electronical probe card:

• Realize an alignment insensitive optical probe.

# Optical concept compensates prober alignment tolerances.

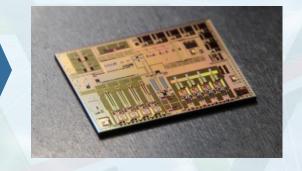

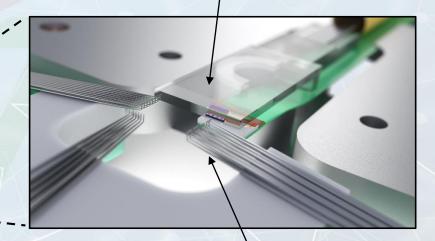

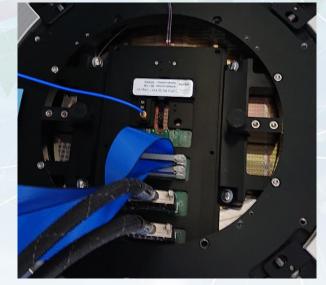

# **Technical Realization of Demonstrator**

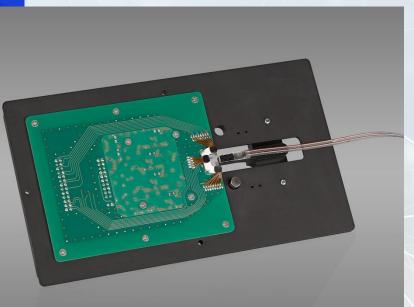

### Demonstrator

- Standard prober interface (Eurocard format)

- Monolithic optical module

- 16 optical I/Os

- Alignment insensitive optical coupling

- Simultaneous optical and electrical probing

Electrical Probe card module – PCB with cantilever needles

Metal frame as interface to prober head plate

**Optical module** with passive optical circuitry for multiple optical I/Os and active components for direct detection

Cantilever needle setup as electrical interface to the DUT

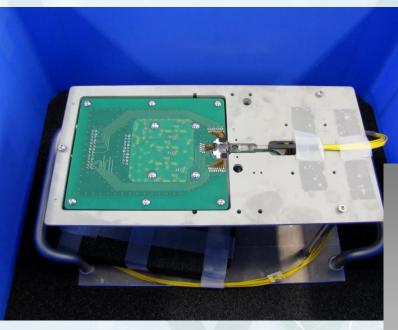

# **Technical Realization of Demonstrator**

#### Demonstrator

- Standard prober interface (Eurocard format)

- Monolithic optical module

- 16 optical I/Os

- Alignment insensitive optical coupling

- Simultaneous optical and electrical probing

Functional Model for prober compatibility check

PROBE TODAY, FOR TOMORROW

Functional Model for lab verification and integration purposes

# **Demonstration of Working Principle**

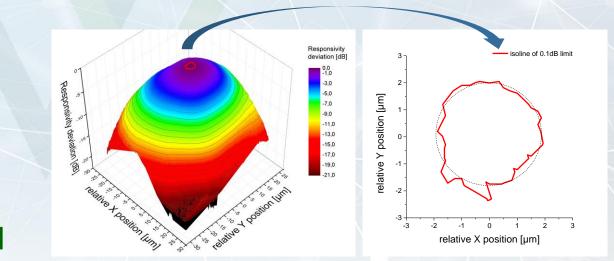

### Conformation of optical working principle under lab conditions

- Build lab setups for raster scan, free space imaging, integration feasibility

- Manufacturing setups

- PIC samples provided by Sicoya

- Measured displacement for -0.1 dB sensitivity range

- RX channel: ±1.9µm

- Alignment loop: ±1.0μm

$\rightarrow$  Working principle of probe card confirmed

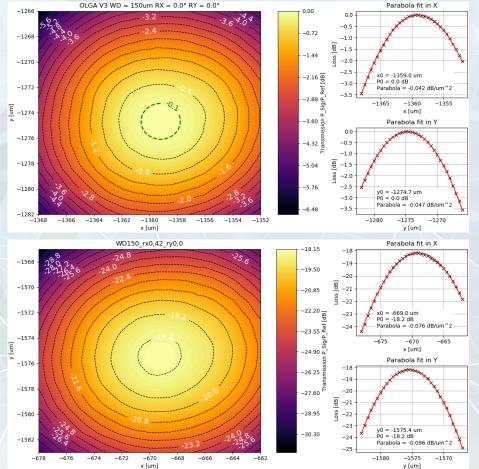

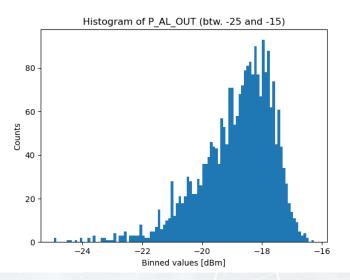

# **Demonstration of Working Principle**

### Conformation of optical working principle under lab conditions

- Raster scans for different optical modules together with PIC

- Optical working distances (WD): typical 50 200μm

- Alignment sensitivity: ±1.25 μm @ -0.1dB and 150μm WD

- Setup insertion loss : ~-18dB to -24dB (incl. loss of optical module, over-illumination, DUT with GC and waveguide)

Alignment insensitivity, insertion loss and optical working distance are not independent parameters to optimize.

→ Find optimum for test case.

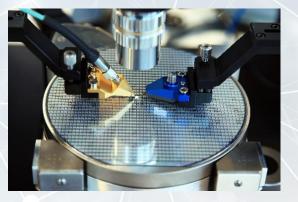

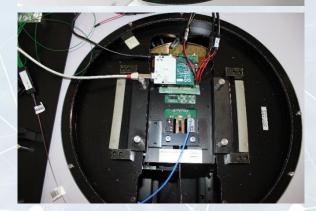

# **Prober compatibility**

LIEROOG

### Conformation of optical working principle - fab conditions

- Initial wafer-level tests on an Accretech UF200R prober

- Mechanical probe card interface

- Communication with prober

- Needle and probe card alignment

- Optical test of PIC alignment channel

- Further tests on Accretech UF3000EX under test floor conditions

- Online Cleaning successfully demonstrated

- Probing stability and working distance

- Alignment procedure and full test program

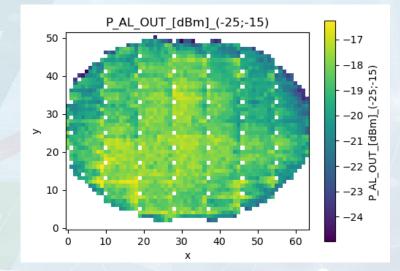

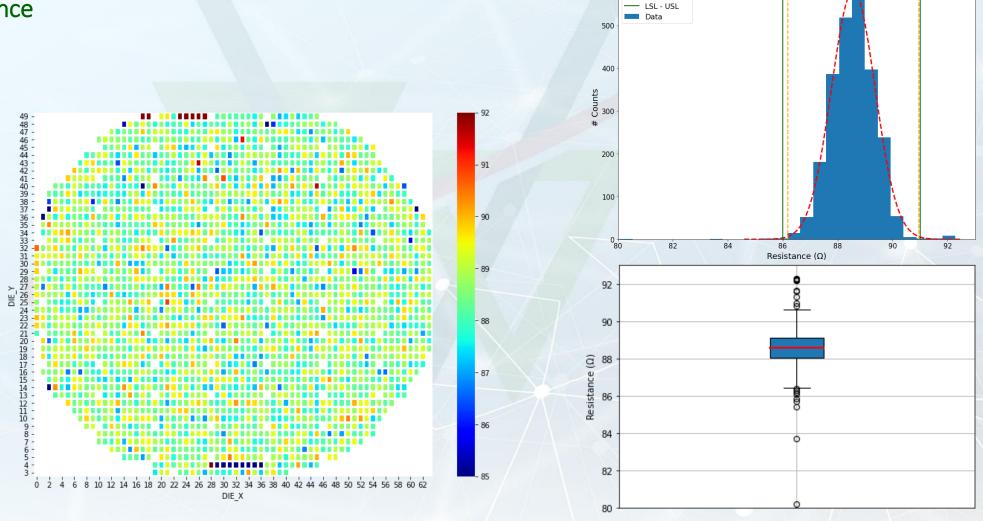

# Device Wafer-level Test – Optical Alignment Channel

#### Wafer-level test of transceiver device

- Final production test

- RX, TX, alignment channel and comprehensive electrical tests in a single touch-down

- 1x alignment per wafer, no additional alignment per chip

- Example of wafer map for optical alignment channel

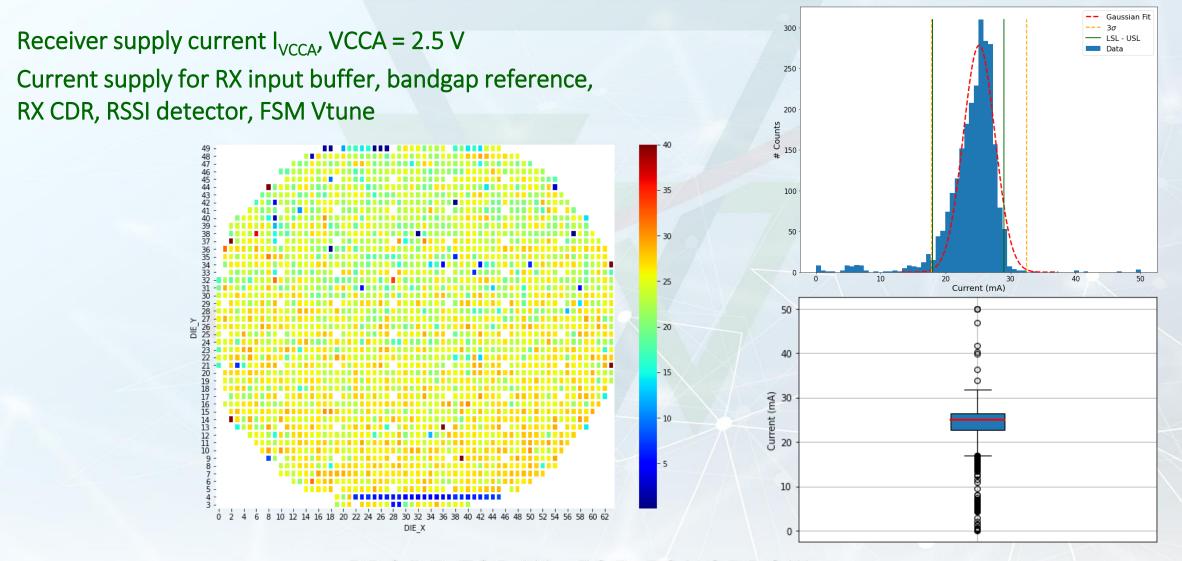

# Device Wafer-level Test – Receiver input current

PROBE TODAY, FOR TOMORROW

# **Device Wafer-level Test – Contact Resistance**

Contact Resistance

600

Gaussian Fit

3σ

# **Conclusion & Outlook**

- Realized a monolithic opto-electronical probe card for PIC measurement

- Proved working principle under lab and test floor conditions

- Showed compatibility with standard prober equipment

- Established final test for production runs

- Evaluation of insensitivity range vs. absolute loss ongoing

- Next steps:

- Improvement of insensitivity range

- Platform development for other needle types

- RF capable probe card

- Outlook: probe cards for multi-DUT and high count optical I/O testing (switches)

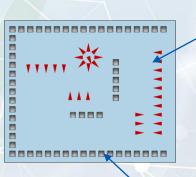

Grating couplers, 'arbitrary' position and orientation for:

- Fiber arrays

- Fiber bundles

- Single fibers

- Laser diodes

Bond pads with 'arbitrary' position

#### Tobias Gnausch, 11/11/2020

# Thank you for your attention!

# Time for questions...

Tobias Gnausch, 11/11/2020