# Micro-Textured Film for Universal Handling of Microelectronics

Raj Varma, Chief Technology Officer Gel-Pak, Hayward, CA rvarma@gelpak.com

#### **Abstract**

This paper will discuss the challenges associated with the constant evolution of IC device dimensions, and the need for carriers that can adapt quickly to the change in form factor but still maintain JEDEC standards for compatibility with existing equipment sets and pick & place tools. The paper will present a new technology inspired by gecko fibril microstructures with reversible adhesion that offers a unique approach to device handling.

## **Background and Motivation**

There is a growing trend and demand for Known Good Die (KGD) – a bare die that has been fully tested prior to packaging. This is introducing an additional step for die level testing vs. the conventional Wafer Probe Testing (WPT).

To truly assure a KGD, the ability to access yield at each intermediate fabrication step - thinning, bond & assembly, packaging - is critical. This is driving the need for more Singulated Die Testing (SDT). SDT is more precise over WPT and can closely represent the end use performance of the die. Also, since the entire wafer need not be handled during testing, dies can be rejected/accepted individually.

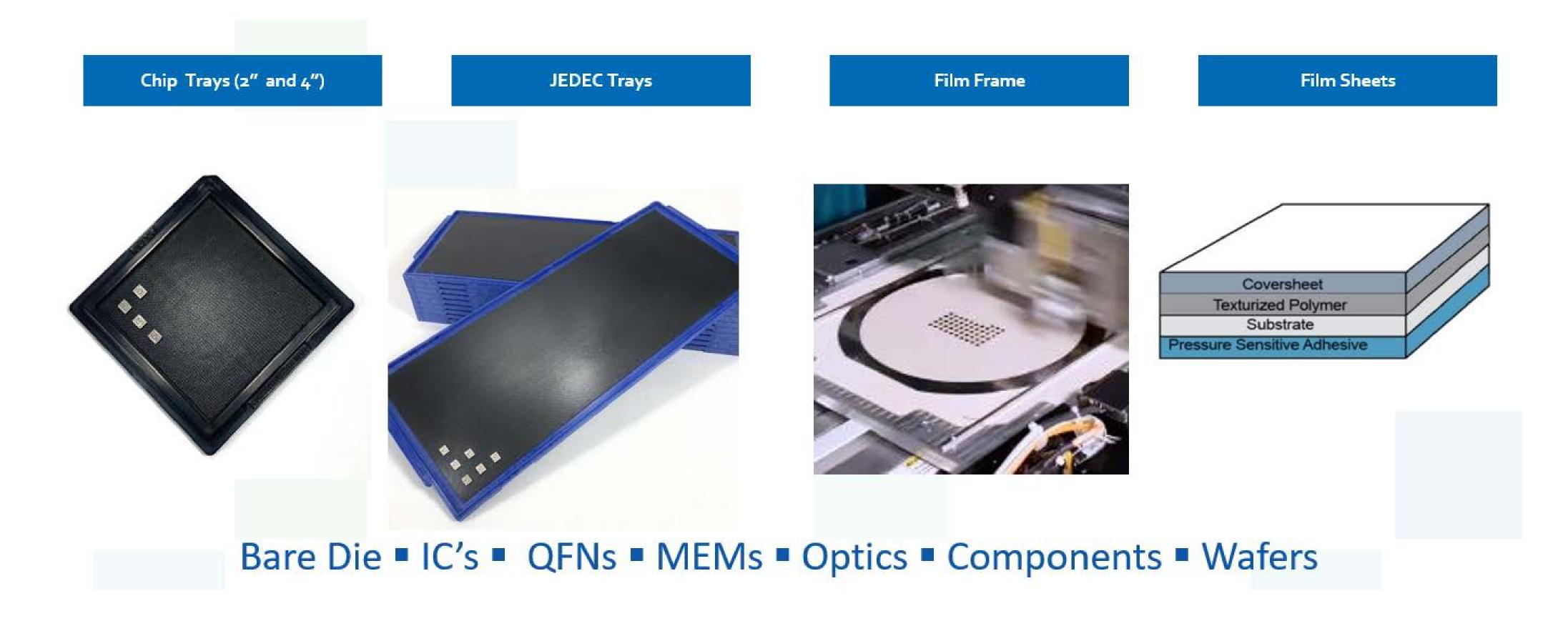

SDT requires open & random access to dies during processing so they can pick & re-pick for multiple tests [3,4]. A few options for die presentation exist but non are ideal. Current options (Figure 1) to present dies for SDT include:

- JEDEC trays Omnipresent for packaged die. Not bare die. Redesigned for each new device.

- Tape & Reel Used for packaged and bare die. Don't offer an easy pick & re-pick required for SDT.

- Sticky tapes, aka Dicing Tape Used for bare die handling. Single use.

Fig. 1: Dicing film, JEDEC trays and Tape & Reel- commonly used device handling formats.

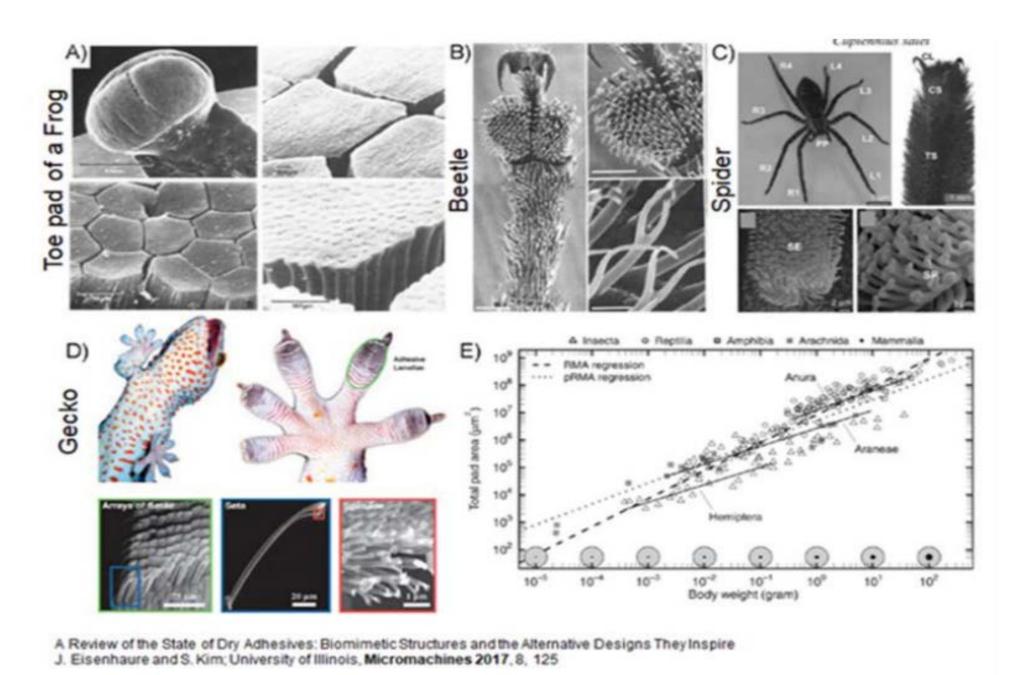

The true example of reversible adhesion is "gecko-like" grip, which can hold the device but will release it with minimum resistance in a PnP process. Geckos, lizards, beetles, spiders, and ants can attach themselves to different surfaces but also detach themselves very easily without disturbing the surface. These creatures have microtextured toe pads. Consisting of fibreleis that can conform to surface irregularities. The adhesion comes from the viscoelastic response of their outer membrane. Figure 2 shows toe pads of different species which helps them move seamlessly across different surfaces.

Figure 2: Images of toe pads of different species which help them move seamlessly across different surfaces.

Each species has a unique texture that helps it move, correlating across species relative to their body weight. Different industries have tried to learn and implement such micro-texturing to help solve issues ranging from optics, fog resistance, pressure sensing, tissue engineering, and microfluidics. In the field of Pressure Sensitive Adhesives (PSA), such micro-texturing has led to the development of dry adhesives, opening a new type of adhesive which offers strong bonding but easy and clean release

Goal: Material and texture combination with Gecko like reversible adhesion giving strong bonding but easy and clean release

### **Materials & Methods**

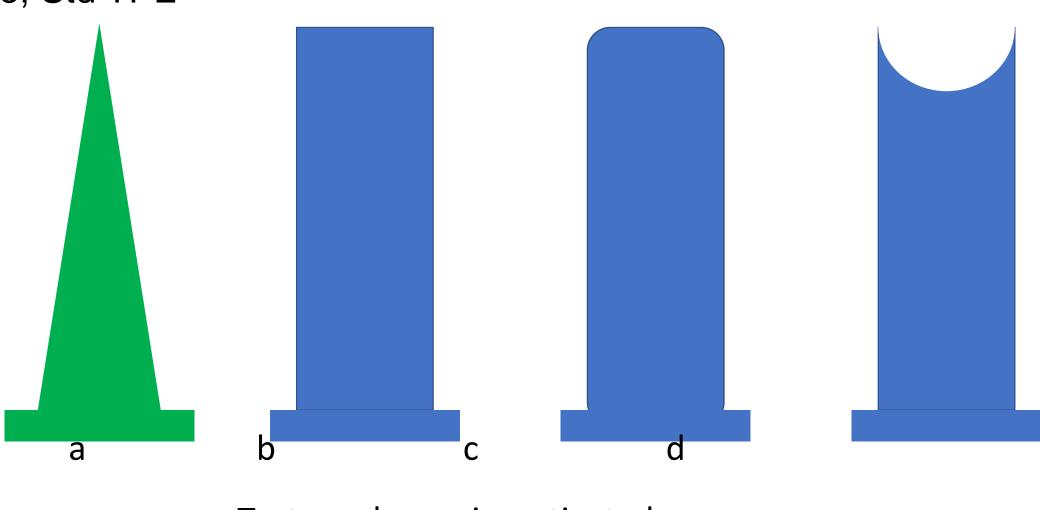

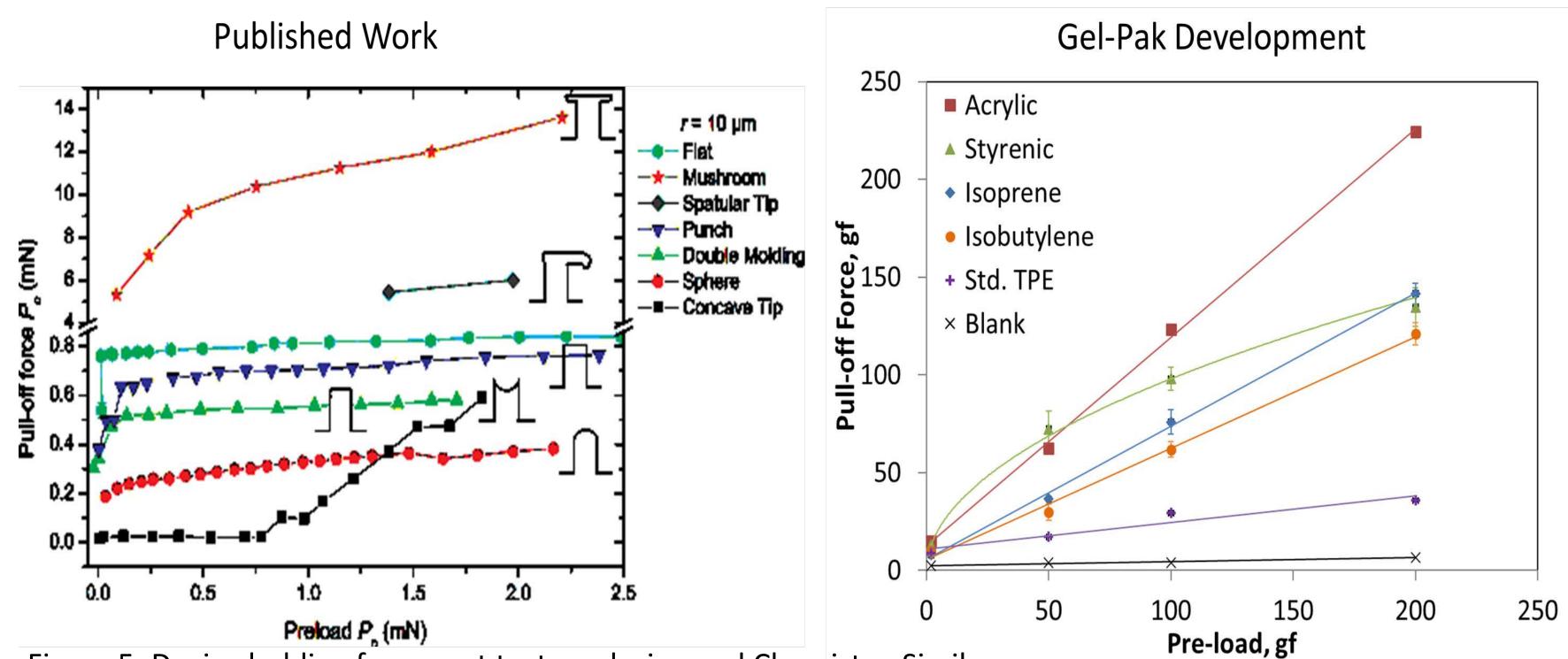

We focused on materials engineering as well as texture engineering compatible with High Volume Manufacturing (HVM), which means utilizing conventional plastics fabrication processes, such as injection molding and extrusion to fabricate, and using materials that are best suited for such process. We focused on materials engineering as well as texture engineering. Various geometric patterns were investigated. We tried 4 different pillar textures as shown in Figure 3, and over 20 different adhesive formulations and put them through various IC handling testing.

Material chemistries included: Acrylic, Styrenic, Isoprene, Isobutylene, Std TPE

Each texture/adhesive option was screened based on the following:

- Shock/vibration/drop at -10C, 20C and 50C

- Long-term tack growth IC backside residue

- PnP and SMT pick ability

The final products were tested on a few different PnP (Royce, Besi, Muhlbauer, MRSI) and SMT (Juki) machines to validate pick ability. PnP parameters including Down force at device contact, time to draw full Vacuum, Tip & Collet size w.r.t device size and Pick speed were investigated.

Texture shapes investigated

## **Results and Conclusions**

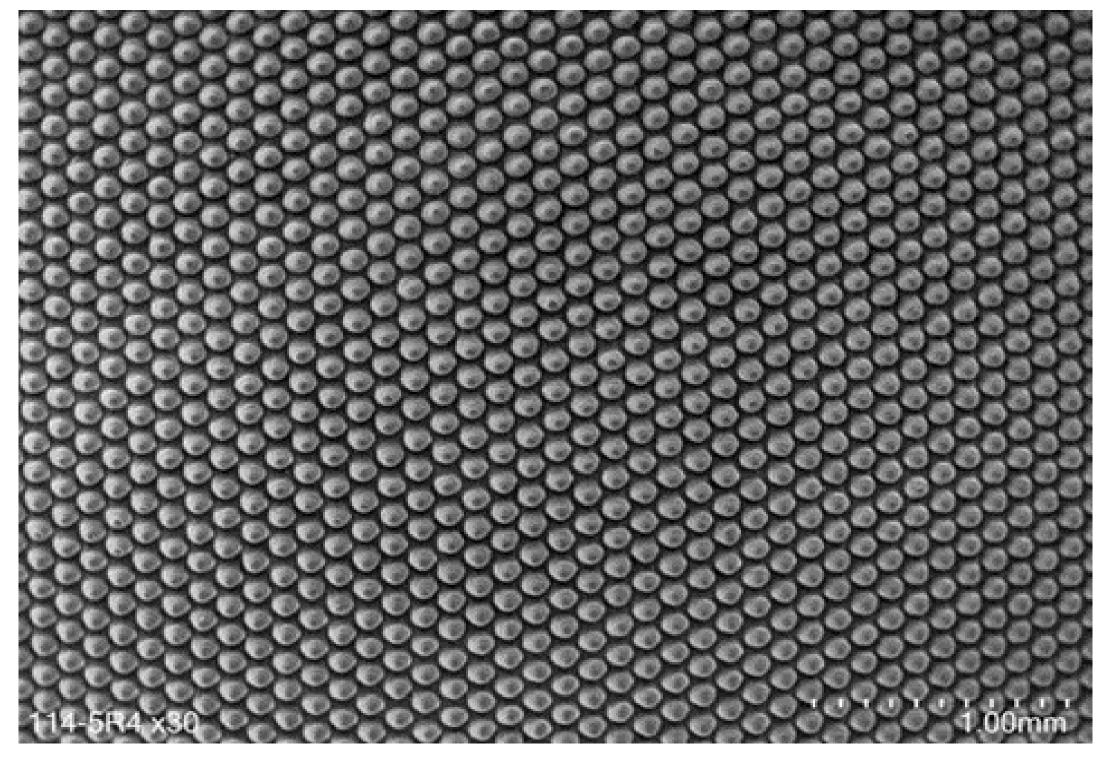

Of the four texture types tested, Type A was chosen. This tip design was the easiest to fabricate small pitches (Figure 4) required for small die. Using this one texture, and varying the polymer chemistry, a wide range of tack levels was achieved. (Figure 5)

Figure 4: Texture pattern developed for universal carrier

Figure 5: Device holding force w.r.t texture design and Chemistry. Similar response by changing chemistry instead of texture

## Results and Conclusions (cont.)

By varying the adhesive chemistry, a variety of tack ranges were created.

- 3 different adhesive formulations were developed

- The Low tack is designed for in-process device handling only

- Medium tack can be used for in-process but subsequently the bare dies can also be shipped on this carrier

- High tack is specifically designed for packaged devices like QFNs

With few modifications to parameters all PnP equipment's were able to successfully pick the IC devices from the trays at medium UPH rates. The key aspects were limiting down force to seal the vacuum cup with the device surface, pull vacuum to an optimum threshold and then initiate the pick.

Inspired by bio-based micro-structures, Gel-Pak has developed an IC tray technology that can be a universal handling solution best suited for SDT for KGD. The technology required fine-tuning adhesive technology and micro-texturing its surface to offer the tack that is just enough to hold the device but also easy to pick at high-speed PnP processes. The technology has been successfully scaled for a few different form factors, ranging from 2-inch chip trays to as large as 300mm wafers.

# Acknowledgements

PnP (Royce, Besi, Muhlbauer, MRSI) and SMT (Juki)

#### References

1] Robertazzi, Raphael & Scheurman, Micheal & Wordeman, Matt & Tian, Shurong & Tyberg, Christy. Analytical test of 3D integrated circuits. 1-10, 2017. 10.1109/TEST.2017.8242067. [2] Gallagher, Wesley, Ysidro, Sam. "Test Process and Apparatus for Testing Singulated Semiconductor Die, International Rectifier Corp.," US Patent 6246251 B1 2001. [3] Yin, Wen, Dingying, WU, Shao, Luyin. "Integrated Circuit Die Transport Apparatus and Methods, Intel", US Patent 2016/0375653 A1 2016. [4] Miller, Charles, Cooper, Timothy, Hatsukano, Yoshikazu. "Test method for Yielding a Know Good Die,", US Patent 7694246 B2 2010