#### Test Consumables – The Road Ahead

## The Changing Cost Structure of Semiconductor Test

June 2020

John West VLSI Research Europe

#### First, we need to talk about the market environment

Impact of COVID-19. What we know for sure...

Fundamental market drivers for semiconductor still in place Chips still need testing

Technical problems for semiconductor test not going away Economic challenges just got a little harder

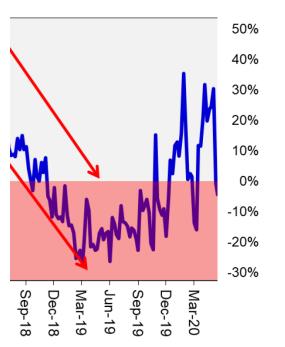

## Semiconductors: Short-Term View **Increased Volatility**

Weekly semiconductor sales compared to the same week last year.

First half of 2020 much better than first half of 2019

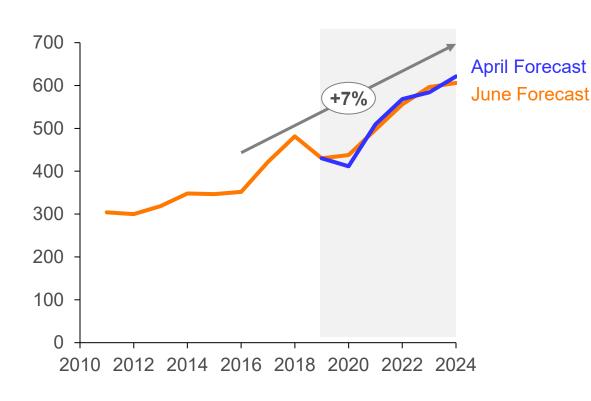

## Semiconductors: Long-Term View, \$Bn

#### Outlook for 2020 is improving

VLSI upgraded forecast for 2020 from -4% to +2%

Growth for Advanced Logic, Foundry and DRAM flat to slightly positive in 2020

Double digit growth for NAND in 2020

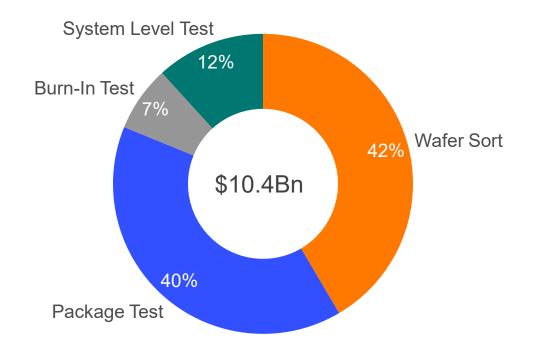

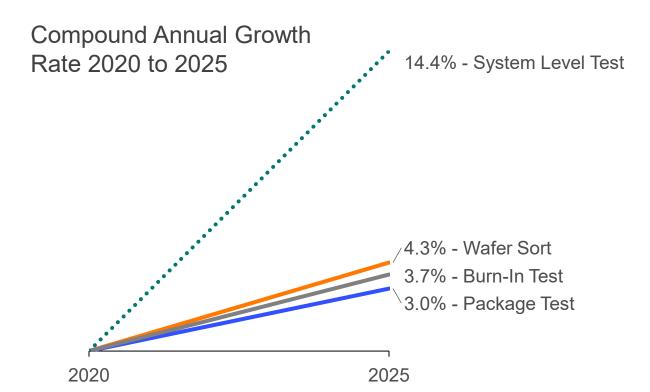

### Semiconductor Test

Wafer Sort

Package Test

Burn-in Test

System Level Test

Multiple points where die can be tested: on wafer, in package, in module, in system

### The Cost of Test – 2019

#### Test hardware and consumables

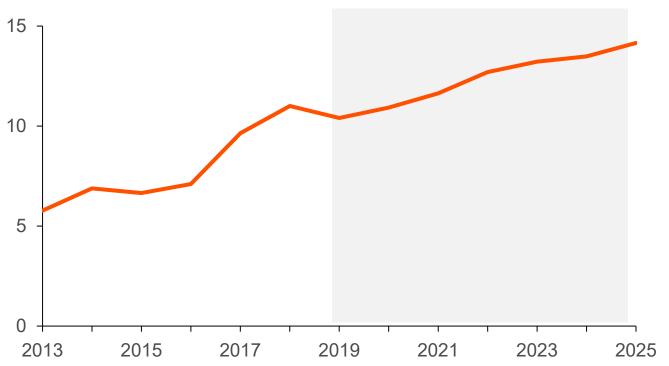

## Cost of Test: a big market and it's growing

Test hardware and consumables, \$Bn

#### Cost of Test

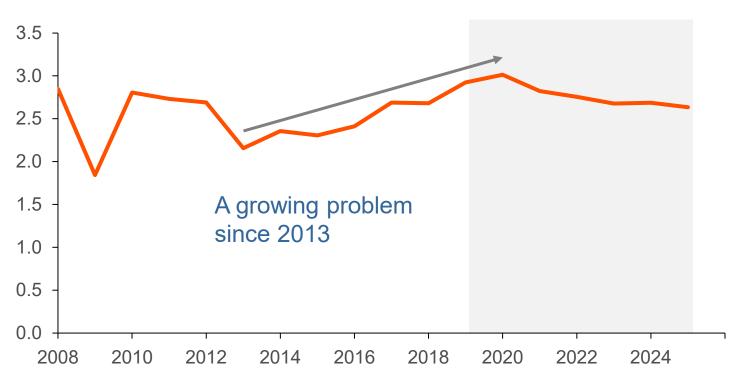

Test hardware and consumable costs as a % of IC revenues

VLSI's forecast very conservative. Assumes cost of test will return to 2.5% of IC revenues

#### Cost of Test

#### Test hardware and consumable costs as a % of IC revenues

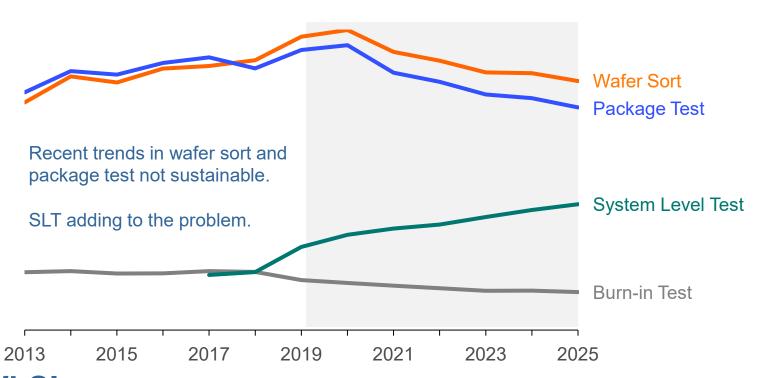

## Rapid growth of SLT

Likely to pull existing cost structure out of shape

## Measuring System Level Test Costs

The market for SLT equipment and consumables not easy to measure: until recently quite small, and suppliers not well known

SLT now entering the mainstream and attracting companies with experience in the semiconductor industry

Market likely to be in excess of \$1Bn in 2020

# Understanding the Dynamics of System Level Test Costs

- Is the recent ramp up just the start of something big, or will it take time for the first round of capacity expansion to be digested?

- Will chipmakers test some or all products?

- Can test handlers be recycled/re-used for new products?

- What are the efficiency gains to be made over time, if any?

- Will some chipmakers continue to make their own test systems?

# System Level Test Costs

Currently around \$1.0Bn

Growing at a compound annual growth rate of 14.4% over next 5 years

This will result in a change of the cost structure of test

# Cost has become a critical problem so what can be done?

Change in test strategy

Squeeze suppliers

### Both options involve risk

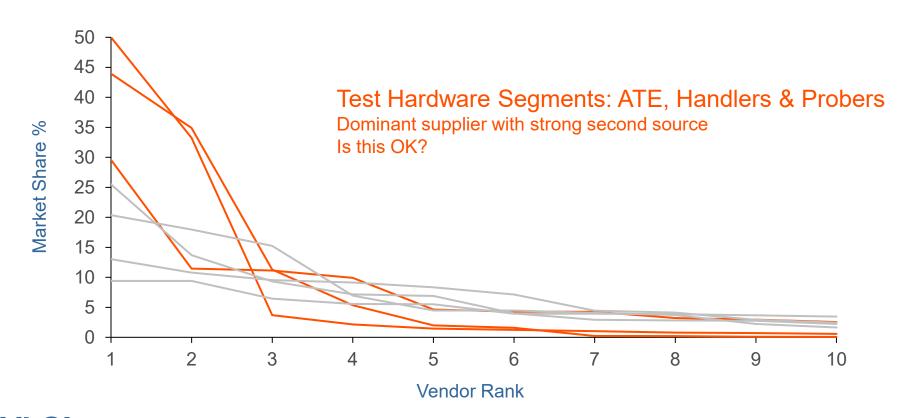

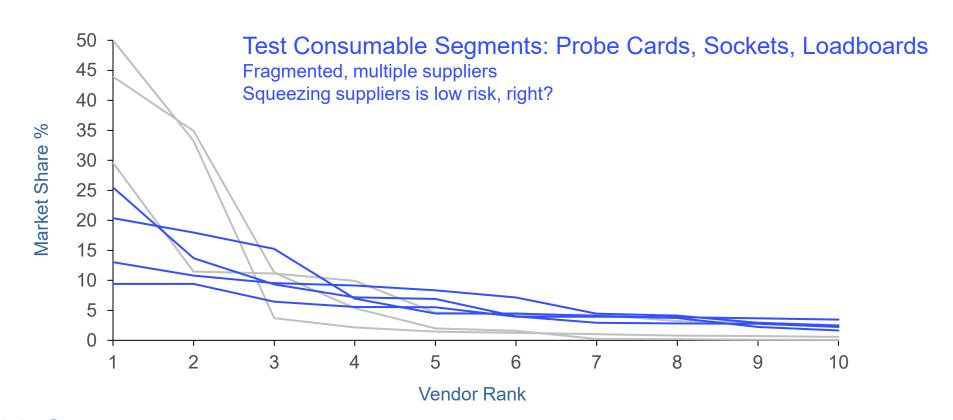

## Squeezing Suppliers: Cost vs. Risk

Buyers are asking a new set of questions

Am I paying too much?

We are not happy with the existing supplier, who else should I be talking to?

We want to encourage and support new entrants. Who are good candidates?

Which suppliers need help, which need to be challenged?

What type of relationships should I be having with my suppliers?

Answering these questions requires more than just numbers

## Example of Risk Analysis

Segment market shares by vendor rank 2019

## Example of Risk Analysis

Segment market shares by vendor rank 2019

# The buyers' challenge

The cost structure of test is changing

You need data, data analytics, and the stories behind the data so that you can...

Identify where costs can be managed, and where they cannot

Evaluate risks and understand how they change over time

## Final thoughts

Challenges exist and are not going away

Closer collaboration between suppliers & buyers would be nice

Find solutions that you can live with

# Questions?

... and backup slides

#### Terms and Conditions, Notices, and Disclaimers, etc.

By accepting this report, opening it, or using it you are agreeing to these terms. This report contains valuable data, intellectual property, and trade secrets developed or acquired by VLSI Research. You have a limited license to hold these materials but do not become the owner of any materials provided are protected by copyright, trade secret, and trademark law. This presentation has been approved by VLSI Research for public release with attribution. The information in the materials may be used by you on a limited basis in your own documents provided that those documents are not-for-sale; VLSI Research's name, brand, or trademarks are not used to endorse a product or company for sales purposes; VLSI Research is clearly referred to as the source of such information; and you obtain written approval prior to use.

This report is provided on an "AS IS," "WHERE IS", "WHERE AVAILABLE", "WITH ALL FAULTS" basis. VLSI Research does not warrant these materials or the information provided therein, either expressly or impliedly, for any particular purpose and VLSI Research specifically disclaims any express or implied warranties, including but not limited to, any express or implied warranties of TITLE, ACCURACY, NON-INFRINGEMENT, MERCHANTABILITY or FITNESS FOR ANY PARTICULAR PURPOSE OR USE.

The sources of the information in this report include numerous individual reports, memos and bulletins from various segments of the industry, annual reports, financial reports, interviews, questionnaires, surveys, technical symposia, trade journals, technical journals and individual assessments by knowledgeable company or industry representatives as well as our own analysis and judgment. Some companies are more cooperative about providing information than others and some companies decline to provide or validate the accuracy of any information. Although the information provided is obtained or compiled from sources VLSI Research believes to be reliable given the oftentimes difficult circumstances under which it is collected, VLSI Research cannot and does not warrant or guarantee the accuracy, validity, truthfulness, timeliness, or completeness of any information or data made available to you for any particular purpose. In no event will VLSI Research be liable to you or any third party, whether in contract, tort or under any other legal theory, for any direct, indirect, special, consequential or incidental damages, or any other damages of any kind even if VLSI Research has been advised of the possibility thereof.

We receive letters and e-mails on current topics covered in our services and/or reports that are of interest to our subscribers, as well as comments on our reports. We value that subscriber input and like to use it. By submitting such material to us, unless you tell us specifically not to publish it, or except to the extent that you give us an embargo date before which you instruct us not to publish it, you authorize us to publish and republish it in any form or medium, to edit it for style and length, and to comment upon or criticize it and to publish others' comments or criticisms concerning it, as the case may be.

This report may contain information concerning stocks that is obtained from the opinions of industry analysts. Quoted past results are not necessarily indicative of future performance. None of the information should be seen as a recommendation to buy or sell any securities. We are not stock analysts or investment advisors. You should contact a registered investment advisor as to the nature, potential, value or suitability of any particular investment action. No information provided is investment advice and any such information is just an opinion and is not tailored to the investment needs of any specific person. Certain statements in this report, other than statements of historical fact, and other written or oral statements made by VLSI Research may be forward-looking. In some cases, you can identify forward-looking statements by terminology such as "may", "will", "should", "expects", "intends", "plans", "anticipates", "believes", "thinks", "estimates", "seeks", "predicts", "potential", and similar expressions. Although VLSI believes that these statements are based on reasonable assumptions, they are subject to numerous factors, risks and uncertainties that could cause actual results and outcomes to differ materially different from those stated or projected. Those factors, among others, could cause actual results and outcomes to differ materially from the results and outcomes stated or projected in, or implied by, the forward-looking statements. You should understand that forward-looking statements are not guarantees of results or outcomes. New risks and uncertainties arise from time to time, and VLSI Research can not predict those events or how they may affect you, the reader. VLSI Research Inc does not have any intention or obligation to update forward-looking statements after the date of this report.

No part of this report may be used in any legal proceedings nor may any of these materials or the information contained therein be disclosed to any third party, including investors or affiliated firms belonging to investors, outside directors or to your affiliated companies, or reproduced or transmitted to any third party, in any form or by any means – mechanical, electronic, photocopying, duplication, microfilming, videotape, verbally or otherwise – without the prior written permission of VLSI Research.

The Chip Insider® and the CSS 10 BEST logo are registered trademarks of VLSI Research Inc. All other trademarks, service marks, and logos are the property of their respective owners.