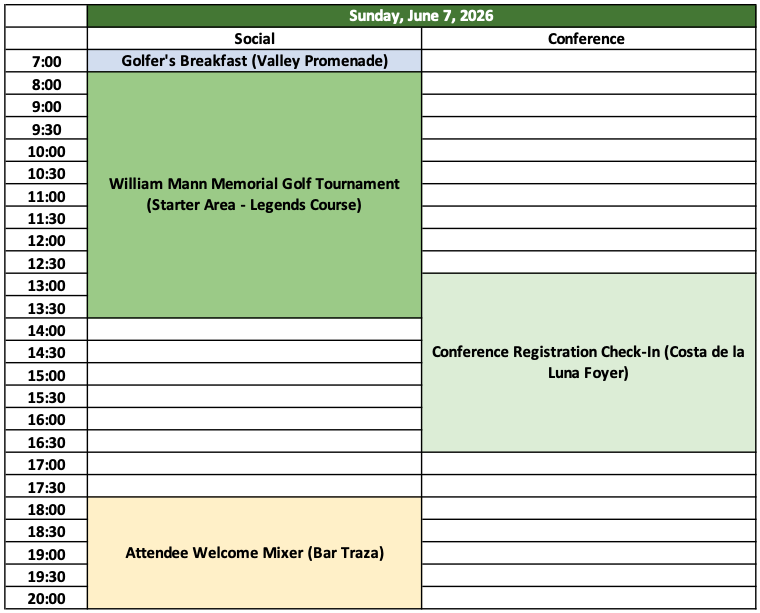

Times in PST | Tentative, subject to change

The detailed schedule will be available in April 2026

For an overview of the general schedule, please refer to the Schedule-At-A-Glance below. This schedule is subject to change.

Detailed Schedule

Sunday, June 7

| Time | Event | Location |

|---|---|---|

| 7:00 a.m. – 8:00 a.m. | Golfers Breakfast | Valley Promenade |

| 8:00 a.m. – 1:30 p.m. | William Mann Memorial Golf Tournament | Starter Area – Legends Course |

| 1:00 – 5:00 p.m. | Conference Registration Check-In | Costa de la Luna Foyer |

| 6:00 – 8:00 p.m. | Attendee Welcome Mixer | Bar Traza |

Monday, June 8

| Time | Event | Location |

|---|---|---|

| 7:00 – 8:00am | Continental Breakfast | Costa de la Luna Courtyard/Lawn |

| 7:00 – 8:00am | Speakers’ Breakfast | Las Palmas 1 and 2 |

| 7:00am – 12:00pm | Exhibitor Check-in | Costa de la Luna Foyer |

| 7:00am – 4:00pm | Conference Registration Check-In | Costa de la Luna Foyer |

| 8:00 – 9:15am | Poster Setup | Costa de la Luna Foyer |

| 8:00 – 8:30am |  Welcome to SWTest 2026 Welcome to SWTest 2026Jerry BROZ, PhD (SWTest Conference General Chair – USA) | Costa de la Luna Ballroom |

| 8:30 – 9:30am |  VISIONARY KEYNOTE SPEAKER (more details) VISIONARY KEYNOTE SPEAKER (more details)Connectivity Scalability: Architecting the Invisible Backbone of the AI Data Center Radha NAGARAJAN, PhD Senior Vice President and Chief Technology Officer, Optical Engineering Group (Marvell – USA) | Costa de la Luna Ballroom |

| 9:30 – 10:00am | Technical Poster Session and Coffee Break | Costa de la Luna Foyer |

| 10:00am – 12:00pm | Technical Session 1: High-Volume Photonics and Optical Test Challenges Session Chair: Mark OJEDA (Infineon Semiconductor – USA) | Costa de la Luna Ballroom |

| 10:00 – 10:30am |  Advancing Test Solutions for High-Volume Manufacturing of Photonic Devices Advancing Test Solutions for High-Volume Manufacturing of Photonic DevicesNikta JALAYER (PI (Physik Instrumente) L.P. – USA), Philipp DIETRICH, Andrés MACHADO, Roman ZVAHELSKYI (Keystone Photonics GmbH – Germany), Axel GRABOWSKI, Jones SCHANSKER, Markus SIMON (Physik Instrumente – Germany) | Costa de la Luna Ballroom |

| 10:30 – 11:00am |  Demonstration of integrated sources and detectors used for ATE optical wafer testing of Silicon Photonic ASICs Demonstration of integrated sources and detectors used for ATE optical wafer testing of Silicon Photonic ASICs Chris BARNARD, Brandon GOMEZ, George SOSNOWSKI, Vu NGUYEN (OpenLight Photonics – USA) | Costa de la Luna Ballroom |

| 11:00 – 11:30am |  Achieving high volume test for silicon photonic devices with a fully integrated and automated solution: EclipsePhotonic from Technoprobe and the Teradyne silicon photonics test platform Achieving high volume test for silicon photonic devices with a fully integrated and automated solution: EclipsePhotonic from Technoprobe and the Teradyne silicon photonics test platformMonica DAVIS, Ethan DWYER, Lakshmi-Anusha CONDON (Teradyne, Inc. – USA), Alessia GALLI (Technoprobe SpA – Italy), Amit AGNIHOTRI, Andy CHANG (Marvell – USA) | Costa de la Luna Ballroom |

| 11:30 – 12:00pm |  Opto‑electronic wafer‑level probe card with optical fiber array and RF interface Opto‑electronic wafer‑level probe card with optical fiber array and RF interfaceTakaharu OHYAMA, Takahiro NAKAMURA, Yasushi WATANABE, Tomohisa HOSHINO (YOKOWO CO., LTD. – Japan), Shigeki OKA (YOKOWO AMERICA CORPORATION – USA) | Costa de la Luna Ballroom |

| 12:00 – 1:30pm | Enjoy Lunch and Networking with Colleagues and Attendees! | Costa de la Luna Courtyard/Lawn |

| 12:00 – 4:00pm | Exhibitor Setup | Costa Del Sol Ballroom |

| 1:30 – 3:00pm | Technical Session 2: Advanced Materials and Probe Architectures Session Chair: Nyi Nyi THEIN (SanDisk Corporation – USA) | Costa de la Luna Ballroom |

| 1:30 – 2:00pm |   Micro-bump probing for advanced System-on-Chip testing: A Preview into Native-Pitch Solutions and their challenges Micro-bump probing for advanced System-on-Chip testing: A Preview into Native-Pitch Solutions and their challengesChandru PERIASAMY, Nikhila MAHADEVAPURAM, Saad AHMED, Ashwin ASHOK (Intel Foundry – USA), Francesco PARLATO, Alice GHIDONI, Daniele PEREGO, Federico LUCCHI, Francesca CATTANEO(Technoprobe SpA – Italy) | Costa de la Luna Ballroom |

| 2:00 – 2:30pm |  New Pogo-MEMS (PEMS) Probe and Wire Probe Designs Enabled by High-Conductivity Pd Alloys New Pogo-MEMS (PEMS) Probe and Wire Probe Designs Enabled by High-Conductivity Pd AlloysPatrick BOWEN, Grant JUSTICE (Deringer-Ney Inc – USA), Hiroyuki NAKAMURA (Nidec SV Probe – Japan), Taeyoon KIM (PTK – Korea) | Costa de la Luna Ballroom |

| 2:30 – 3:00pm |  Resolving the Contact Dilemma: An Industrialized Framework for Fine-Pitch Wafer Test using µ3D Printed Probes Resolving the Contact Dilemma: An Industrialized Framework for Fine-Pitch Wafer Test using µ3D Printed ProbesFrancesco COLANGELO, Wabe KOELMANS, Edgar HEPP, Patrik SCHüRCH (Exaddon AG – Switzerland) | Costa de la Luna Ballroom |

| 3:00 – 3:30pm | Technical Poster Session and Coffee Break | Costa de la Luna Foyer |

| 3:30 – 5:00pm | Technical Session 3: System-Level Integration and HBM Specific Solutions Session Chair: Joey WU (Toward Technologies – Taiwan) | Costa de la Luna Ballroom |

| 3:30 – 4:00pm |  The Ever-Increasing Challenge of Probe Card Power Delivery The Ever-Increasing Challenge of Probe Card Power DeliveryBlake RAPP (Micron Technology, Inc. – USA) | Costa de la Luna Ballroom |

| 4:00 – 4:30pm |   Integrated Solution for HPC Testing in AI Era Integrated Solution for HPC Testing in AI EraOscar LEE, Kenny TANG (TSMC – Taiwan) | Costa de la Luna Ballroom |

| 4:30 – 5:00pm |  A Novel Advanced Probe Card Approach for Multi-Temperature HBM Testing A Novel Advanced Probe Card Approach for Multi-Temperature HBM TestingSeunghoon YANG (SK Hynix – South Korea), Timothy BLOMGREN, Kalyanjit GHOSH, Alan LIAO (FormFactor – USA) | Costa de la Luna Ballroom |

| 5:00 – 8:00pm | SWTest 2026 EXPO Open | Costa Del Sol Ballroom |

| 8:00 – 10:00pm | Sponsor Hospitality Events |

Poster Session

Session Chair: Rey RINCON (SWTest Conference – USA)

(Costa de la Luna Foyer)

- First Probe Card for DUT Measurements at 120 GHz to Support 1.6 Tbps

Christopher LEMOINE (FormFactor – USA) - Lens-Based Free-Space Characterization of High-Resistivity Silicon Wafers at Microwave Frequencies

Zhonghao HU, Bevan JONES (Ascan Technologies – Australia), Anton SARESSALO, Iiro LEHTO, Katja PARKINEN (Okmetic – Finland) - Enabling Die Level KGD Testing for CPO Optical Engine

Ai Heong TAN, Jiawei LIN, Tim JIN (Nexustest Pte Ltd – Singapore) - New approaches to protect probe cards during high-power short-circuit test

Alvaro ROSA, Georg FRANZ, Rainer GAGGL (T.I.P.S. Messtechnik GmbH – Austria) - Demonstration of High Precision Silicon Photonics Wafer Measurements Using a PLC (Planar Lightwave Circuit) Probe and Its Applicability to Multi Channel, Large Scale Inspection

Shinji MINO, Akihito DOI, Kenya SUZUKI, Masaki UENO, Yoshinori HIBINO (NTT Innovative devices – Japan) - 448 Gbps Probe Architecture for High-Speed, High-Power Test

Don THOMPSON (PTSL – USA) - Introduction of an MLO with Excellent Geometric Stability

Osamu OGURA (Lincstech – Japan) - High-Precision Low‑Resistance Measurement for Advanced Interconnects in the AI Era

Kenichi TAKANO (Keysight Technologies – Japan) - 1.6T Ethernet DSP: Testing 200G Lanes with Loopback

Jeffery ARASMITH (MPI Corporation – USA), Alex YANG (MPI Corporation – Taiwan) - Atomic-Level Design of Palladium Alloys: Decoding the Mechanisms for High-Performance Semiconductor Test Materials

Jonas FECHER (Sickert – Germany) - Eliminating Cleaning-Induced Failures: Achieving Zero-Debris Probe Tips in Low and High Temperature Wafer Testing

Victoria TRAN (Gel-Pak – USA), Tomonao NAKASHIMA (Japan Electronic Materials – Japan) - High Density Laser Drilling in Semiconductor Test Hardware: Evaluating the Trade-Off Between In-House Capability and Outsourced Manufacturing

Chris STOKES, Namrata LACHMAN (Oxford Lasers Ltd – United Kingdom)

Tuesday, June 9

| Time | Event | Location |

|---|---|---|

| 7:00 – 8:00am | Continental Breakfast | Costa de la Luna Courtyard/Lawn |

| 7:00 – 8:00am | Committee Breakfast | Las Palmas 1 and 2 |

| 7:00am – 3:00pm | Conference Registration Check-In | Costa le la Luna Foyer |

| 8:00 – 9:30am | Technical Session 4: Market Outlook and Emerging Probing Solutions Session Chair: Alistair LAING (Micron Technology – USA) | Costa de la Luna Ballroom |

| 8:00 – 8:30am |  Semiconductor Market Outlook – Challenges and Opportunities Semiconductor Market Outlook – Challenges and OpportunitiesBoris METODIEV (TechInsights – UK) | Costa de la Luna Ballroom |

| 8:30 – 9:00am |   High-Volume Wafer Testing Solutions for Released-MEMS and BioChip Applications High-Volume Wafer Testing Solutions for Released-MEMS and BioChip ApplicationsMickey YANG, Wen Yuan HSU (Hermes Testing Solutions Inc. – Taiwan) | Costa de la Luna Ballroom |

| 9:00 – 9:30am |  Integer Linear Programming Optimization for Wafer Sort Touchdown Reduction and Mechanical Risk Mitigation Integer Linear Programming Optimization for Wafer Sort Touchdown Reduction and Mechanical Risk MitigationKelvin LO (Google – Taiwan) | Costa de la Luna Ballroom |

| 9:30 – 10:00am | Technical Poster Session and Coffee Break | Costa de la Luna Foyer |

| 10:00 – 12:00pm | Technical Session 5: Thermal Management Innovations Session Chair: Geert GOUWY (IMEC – Belgium) | Costa de la Luna Ballroom |

| 10:00 – 10:30am | Milos BASOVIC, Alexander MAMCHIK, Goutham KUKKADAPU (Intel – USA), Federica BERETTA, Flavio MAGGIONI, Elia MISSAGLIA (Technoprobe SpA – Italy) | Costa de la Luna Ballroom |

| 10:30 – 11:00am |  Breaking the Limits Of HPC Testing Breaking the Limits Of HPC TestingShoun YU (SEMICS INC. – Korea) | Costa de la Luna Ballroom |

| 11:00 – 11:30am |  Various thermal control solution capability under actual device testing Various thermal control solution capability under actual device testingTakehiko TOMITA (TEL – Japan), Xin-Reng FOO (AMD – Singapore) | Costa de la Luna Ballroom |

| 11:30 – 12:00pm |  Marvell ATE Test Cell Digital Thermal Feedback Loop Architecture & Implementation Marvell ATE Test Cell Digital Thermal Feedback Loop Architecture & ImplementationEnrico ZSCHEMISCH, Kris HUBLITZ (Marvell – USA) | Costa de la Luna Ballroom |

| 12:00 – 1:30pm | Enjoy Lunch and Networking with Colleagues and Attendees! | Costa de la Luna Courtyard/Lawn |

| 12:00 – 1:30pm | Poster Removal | Costa de la Luna Foyer |

| 1:30 – 3:00pm | Technical Session 6: Test Cell Optimization Session Chair: Karan MANIAR (AEM – USA) | Costa de la Luna Ballroom |

| 1:30 – 2:00pm |  Real-Time Total Path Resistance Measurement and Dynamic Compensation for Accurate High-Volume Post-Silicon IO Testing Real-Time Total Path Resistance Measurement and Dynamic Compensation for Accurate High-Volume Post-Silicon IO TestingSujith THOMAS, Dinesh SHARMA, Mathangi RAGHURAMAN, Siva Elango S (SanDisk Corporation – India) | Costa de la Luna Ballroom |

| 2:00 – 2:30pm |  High-Throughput SiC KGD Testing: Enabling Mass Production via Dual-Die Handler Architecture High-Throughput SiC KGD Testing: Enabling Mass Production via Dual-Die Handler ArchitectureMarcus KONTOROWITZ, Jiawei LIN (NEXUSTEST – Singapore), Allen ZHANG, Yishen ZHANG (Semight Instruments – China) | Costa de la Luna Ballroom |

| 2:30 – 3:00pm |   The Dual‑Action MEMS Solution: Cleaning Innovation Meets Cost Reduction The Dual‑Action MEMS Solution: Cleaning Innovation Meets Cost ReductionKaden BYRD (Texas Instruments – USA), Kenneth BOBLAK (Entegris – USA), FormFactor, Inc. (FormFactor, Inc. – USA) | Costa de la Luna Ballroom |

| 3:30 – 5:00pm | SWT CREW Mixer | Costa Del Sol Terrace |

| 5:00 – 8:00pm | SWTest 2026 EXPO Reception | Costa Del Sol Ballroom |

| 8:00 – 10:00pm | Sponsor Hospitality Events |

Poster Session

Session Chair: Rey RINCON (SWTest Conference – USA)

(Costa de la Luna Foyer)

- First Probe Card for DUT Measurements at 120 GHz to Support 1.6 Tbps

Christopher LEMOINE (FormFactor – USA) - Lens-Based Free-Space Characterization of High-Resistivity Silicon Wafers at Microwave Frequencies

Zhonghao HU, Bevan JONES (Ascan Technologies – Australia), Anton SARESSALO, Iiro LEHTO, Katja PARKINEN (Okmetic – Finland) - Enabling Die Level KGD Testing for CPO Optical Engine

Ai Heong TAN, Jiawei LIN, Tim JIN (Nexustest Pte Ltd – Singapore) - New approaches to protect probe cards during high-power short-circuit test

Alvaro ROSA, Georg FRANZ, Rainer GAGGL (T.I.P.S. Messtechnik GmbH – Austria) - Demonstration of High Precision Silicon Photonics Wafer Measurements Using a PLC (Planar Lightwave Circuit) Probe and Its Applicability to Multi Channel, Large Scale Inspection

Shinji MINO, Akihito DOI, Kenya SUZUKI, Masaki UENO, Yoshinori HIBINO (NTT Innovative Devices – Japan) - 448 Gbps Probe Architecture for High-Speed, High-Power Test

Don THOMPSON (PTSL – USA) - Introduction of an MLO with Excellent Geometric Stability

Osamu OGURA (Lincstech – Japan) - High-Precision Low‑Resistance Measurement for Advanced Interconnects in the AI Era

Kenichi TAKANO (Keysight Technologies – Japan) - 1.6T Ethernet DSP: Testing 200G Lanes with Loopback

Jeffery ARASMITH (MPI Corporation – USA), Alex YANG (MPI Corporation – Taiwan) - Atomic-Level Design of Palladium Alloys: Decoding the Mechanisms for High-Performance Semiconductor Test Materials

Jonas FECHER (Sickert – Germany) - Eliminating Cleaning-Induced Failures: Achieving Zero-Debris Probe Tips in Low and High Temperature Wafer Testing

Victoria TRAN (Gel-Pak – USA), Tomonao NAKASHIMA (Japan Electronic Materials – Japan) - High Density Laser Drilling in Semiconductor Test Hardware: Evaluating the Trade-Off Between In-House Capability and Outsourced Manufacturing

Chris STOKES, Namrata LACHMAN (Oxford Lasers Ltd – United Kingdom)

Wednesday, June 10

| Time | Event | Location |

|---|---|---|

| 7:00 – 8:00am | Continental Breakfast | Costa de la Luna Courtyard/Lawn |

| 7:00 – 10:00am | Exhibitor Teardown | Costa Del Sol Ballroom |

| 8:00 – 9:30am | Technical Session 7: Challenges of Wafer Test Scaling Session Chair: Matthew ZEMAN (FormFactor, Inc. – USA) | Costa de la Luna Ballroom |

| 8:00 – 8:30am |  Micro Bump Probing: High Volume Experience Driven Capability Demonstration and Direction for Advanced 3D/2.5D Packaging Micro Bump Probing: High Volume Experience Driven Capability Demonstration and Direction for Advanced 3D/2.5D PackagingSaad AHMED, Hamed BARGHI, Karthik SUBRAMANIAN, Thakshila WICKRAMARATNE (Intel Foundry – USA), Jeremy STREIFER, Ethan CAUGHEY (FormFactor – USA) | Costa de la Luna Ballroom |

| 8:30 – 9:00am |  Benefits and Challenges of High Temperature Probe Benefits and Challenges of High Temperature ProbeEmmett RICKS (Micron – USA) | Costa de la Luna Ballroom |

| 9:00 – 9:30am |   A New 300mm Vertical Probing Solution Enabling Automotive Microcontroller High Volume Manufacturing and Test A New 300mm Vertical Probing Solution Enabling Automotive Microcontroller High Volume Manufacturing and TestFrancesco CASARTELLI, Raffaele VALLAURI (Technoprobe SpA – Italy), Johann HEITZER, Oliver NAGLER (Infineon Technologies AG – Germany) | Costa de la Luna Ballroom |

| 9:30 – 9:45am | Coffee Break | Costa de la Luna Foyer |

| 9:45 – 12:00pm | Technical Session 8: ATE Interface Performance and Signal Integrity Session Chair: Jerry BROZ (SWTest Conference – USA) | Costa de la Luna Ballroom |

| 9:45 – 10:15am |  UltraFLEXplus Z-Stack Deflection and Its Effect On Continuity Performance Across UltraFLEXplus Interface Types (SPTL/UPTL) and Application Space Sizes (SAA/EAA) At Wafer Probe UltraFLEXplus Z-Stack Deflection and Its Effect On Continuity Performance Across UltraFLEXplus Interface Types (SPTL/UPTL) and Application Space Sizes (SAA/EAA) At Wafer ProbeDoug GARRETT (NXP – USA), Chris BUCKHOLTZ (Teradyne, Inc. – USA) | Costa de la Luna Ballroom |

| 10:15 – 10:45am |  Loadboard Cooling Technology to Support Higher Currents on ATE Boards Loadboard Cooling Technology to Support Higher Currents on ATE BoardsQuaid Joher FURNITUREWALA (Advantest America Inc. – USA) | Costa de la Luna Ballroom |

| 10:45 – 11:15am |  Telemetry‑Driven Predictive Maintenance for Wafer Acceptance Test Probe Cards Telemetry‑Driven Predictive Maintenance for Wafer Acceptance Test Probe CardsMohammed Hussain SUHAIL, Chuan Hau CHUAH, Ei Zin EL, Joo Chuan GOH, Tee Whay LIM, Meng Yew SEAH (GlobalFoundries – Singapore) | Costa de la Luna Ballroom |

| 11:15 – 11:45am |  Revolutionary Solutions for Cryogenic On-Wafer Test Revolutionary Solutions for Cryogenic On-Wafer TestGarrett TRANQUILLO (Celadon Systems, Inc. – USA) | Costa de la Luna Ballroom |

| 11:45 – 12:00pm |  SWTest 2026 Awards and Adjournment SWTest 2026 Awards and AdjournmentJerry BROZ (SWTest Conference – USA) See you June 7-9, 2027 at the Omni La Costa Resort! Travel Safe and Stay Healthy! | Costa de la Luna Ballroom |

Please note: You can find details on all of the earlier program eProceedings in the SWTest Conference Archives.

| Monday, June 6, 2022 | |

|---|---|

| 7:00 – 8:00 | Continental Breakfast |

| 7:00 – 12:00 | Registration |

| 8:00 – 9:30 | Welcome and Visionary Keynote Speaker |

| 8:00 – 8:30 | Opening Remarks for SWTest 2022 Jerry Broz, PhD, SWTest General Chair, Advanced Probing Systems |

| 8:30 – 9:30 | KEYNOTE

Architecting Test Solutions for the Next Generation of Compute Architecting Test Solutions for the Next Generation of ComputeJohn Yi, Product Engineering Organization Fellow Advanced Micro Devices (AMD) AbstractAs the world of compute continues to grow from consumer devices to supercomputers to edge compute, new generation of products are being created with ever growing complexity. Future product architectures are evolving to supply the increasing demand for compute power, automation, and data. It is essential to work closely across multiple disciplines from silicon design, DFT, and test hardware/software to ensure success in being able to test these new generation of products with minimal test costs and the highest level of quality & reliability. As compute products continue to push fab process geometries in addition to pushing more complex 2.5D & 3D construction processes, this has required more emphasis on increasing test coverage & capacity for probe test solutions. Probe test requirements will demand higher current capability, tighter pitches, & higher test frequencies while sustaining high production lifetimes & test integrity. This will bring a new level of innovation in probe technologies as new metallurgy and construction schemes are being developed along with enhanced test methods across the industry. This keynote presentation will provide a general compute overview & roadmap, methods of innovating new test solutions, and provide wafer probe test needs going forward. BiographyJohn is a Fellow in the Product Engineering organization at AMD and currently manages a team of architects responsible for co-developing new DFT methods & test solutions. His current focus is defining manufacturable test solutions for the challenges of AMD’s heterogenous 2.5D & 3D products. In his previous role, John was responsible for defining the architecture & test strategy for ATE, Burn-in, and System-Level test hardware across the wide spectrum of AMD products. John has been at AMD for 28+ years responsible for driving many test innovations from concept to production deployment. Prior to joining AMD, John graduated from the University of Texas in Austin in Electrical Engineering. |

| 9:30 – 10:00 | Break – Poster Session |

| 9:30 – 10:00 | POSTER SESSION: Probe Potpourri 1 |

Magnetic Testing Tutorial – Wafer probing with 3D magnetic stimulation Georg Franz (T.I.P.S. Messtechnik GmbH – Villach, Austria)

Georg Franz has worked in the Semiconductor Industry for 20 years. After receiving his masters degree in mechanical engineering at the Technical University in Vienna, Austria he worked 7 years at Carinthian Tech Research in Villach, where he developed wafer handling equipment and micromanufacturing machines and conducted finite element simulations. In 2012 he joined T.I.P.S. Messtechnik, a probe card manufacturer focused on power, automotive and sensor devices. His main field of activity is the advancement of test technologies and the development of new products, especially high voltage test and magnetic sensor stimulation. Hydra Probes – Simplifying and Standardizing Semiconductor Test Tes Olson (Cohu – St Paul, USA) Rob Stoner (Cohu – Saint Paul, USA)

Rob Stoner is a Program Manager for the Interface Solution Group (ISG) of Cohu Incorporated. He graduated from Minnesota State University with a BSME and holds an MBA from the University. of St. Thomas. He spent the first 11 years of his career in the Defense industry, where he managed the development and production of avionic and shipboard systems. He joined Cohu in 2021 and has since managed the development of new R&D contactor solutions. Increasing transparency in wafer test probecard maintenance processes through targeted key performance indicators Lasse Meyer (Infineon Technologies Dresden GmbH & Co. KG – Dresden, Germany) Dr. Veronika Haehnel (Infineon Technologies Dresden GmbH & Co. KG – Dresden, Germany)

Dr. Veronika Haehnel joined the FE wafer test division at Infineon Dresden in 2017 and is currently as Staff Engineer Material Science responsible for the management and optimization of the probecard processes including database management, cleaning procedures, KPI creation & tracking as well as all quality and audit relevant topics. Initially, she worked as a Senior Engineer Wafer Test for Chipcard products including wafer test monitoring. Prior to joining Infineon she spent 8 years with Leibniz Institute for Solid State and Materials Research Dresden in basic research of nano- & microstructured electrodeposited systems. She holds a diploma engineering degree and a PhD in Materials Science from Technische Universität Dresden. Automated temperature calibration routine for prober chucks Harald Ibele (Sigma Sensors (TCL) GmbH – Sigmaringen, Germany)

Harald Ibele is the Owner, Technical and Quality Manager of Sigma Sensors, an A2LA ISO17025:2017 accredited Temperature Calibration Laboratory He first joined the Semiconductor Industry in 2003 working for a Microelectronic distributor and established an accredited calibration laboratory in 2005. In 2007 he joined a European thermal chuck manufacturer establishing their presence in the US before relocating to Asia to build their support network in 2012. Harald has extensive experience with temperature aspects of waferprobe, custom temperature solutions, prober sealing and thermal upgrades. After having returned to Europe in 2017 he directed global sales and customer support for thermal chucks before starting his own business in 2019. Sigma Sensors is based in Sigmaringen Germany with a newly established branch in the US. Sigma Sensors performs on site, accredited thermal chuck calibrations and manufactures the made for global mobility Cowboy Wafer. He currently lives in Germany and has 4 children. Small Pad/Small Pitch Dual-Sided Single-Level Space Transformer Dominik Schmidt (Translarity Inc. – Fremont, USA) Probe Debris Rating Scale Karan Maniar (Nidec SV TCL – Tempe, USA) Kyle Cotner (Nidec SV TCL – Tempe, USA)

Kyle graduated with a Bachelor of Science degree (cum laude) in Mechanical Engineering from the University of Arizona in 2005. He has worked in Germany and in the U.S. for start-ups, mid-size companies, and multinational corporations across the automotive, medical device, and now semiconductor test industries. Kyle joined the Nidec SV TCL team in late 2015 as the Product Engineering Manager based in Tempe, Arizona. He used his experience from other industries in project management and new product industrialization to improve the operational performance of the product engineering team and quickly came up to speed with the unique aspects of wafer test. In 2019, Kyle was promoted to Director of Engineering and added overall responsibility for engineering and design to his role. He has focused heavily on removing internal barriers and improving communication to streamline operations, improve quality and performance, and shorten lead time. In his free time, Kyle enjoys traveling (when Covid allows), golfing, running, and homebrewing. Novel Micro-Textured Film Offers Promise in Universal Handling during IC Test Raj Varma (Gel-Pak – Hayward, USA)

Raj Varma has over 26 years of industry experience working in Semiconductor, Packaging and Consumer markets. Raj has been with Gel-Pak as the CTO since 2012. Prior to Delphon he was CTO at Neocork, and various R&D & commercial roles at GLS Corp. Raj has a B.S in Chemical Engineering, M.S. in Polymer Engineering from the University of Akron, and an MBA from the Illinois Institute of Technology, Chicago. He has presented more than 20 papers at various conferences and holds 6 U.S. and International patents. |

|

| 10:00 – 12:00 | SESSION 1: Innovative Materials and Processes Session Chair: Jerry Broz, PhD (SWTest Conference General Chair) |

| 10:00 – 10:30 | PALYSIUM – A Revolutionary Material For Probing Jonas Sorg, Marc Raettig (Heraeus – Hanau, Germany) Jonas Fecher (Heraeus – Hanau, Germany)

|

| 10:30 – 11:00 | New Ceramic Technology Noh Tae Hyung (Disruptive Innovation Technology (DIT) – Siheung, Korea) Paul Kim (Disruptive Innovation Technology (DIT) – Siheung, Korea)

Paul Kim is the head of global sales for GI technology. We have been working together with our partner company (DIT) Disruptive Innovation Technology to perfect a new process to make thin ceramic substrates that can be made into MLC’s and various other products. All the credit for this new technology goes to Mr. Noh, the founding CEO of DIT. I will be the main presenter due to the lack of English proficiency. |

| 11:00 – 11:30 | Does Femto Laser micro machining match with guide plates and probes requirements? Angelo Rizzo (Posalux SA – Biel/Bienne, Switzerland)

Mr. Angelo Rizzo joined Posalux in 2006 and is currently Business Area Manager Electronic. He is active in the micro-machining world since the beginning of his career and served in different sales and management roles. With a long experience in the micro-drilling/routing of Printed Circuit Boards, he started focusing on the semiconductor industry by introducing high-tech mechanical and Laser machines. More specifically, he was responsible for developing the guide plates and probes micro-machining market. Passionate about technology, today Angelo is working closely with Laser R&D process engineers, the goal being to push applications like square holes and MEMS probes cutting beyond the limit. Angelo graduated from the University of Neuchâtel, Switzerland with a master degree in International Business Development. |

| 11:30 – 12:00 | Methodology to improve WAT probe card Probe Mark and Lifetime Eric Sik Kiang Lau, Tai Lin Goh, Tee Whay Lim (GLOBALFOUNDRIES – Singapore, Singapore), Yang Qu, Toh Wei Leong, Jean Tan (STAr-Quest Technologies Pte. Ltd. – Singapore, Singapore), Yu-Ming Chien (Star Technologies – Hsinchu City, Taiwan) Jeffrey Lam (STAr-Quest Technologies Pte. Ltd. – Singapore, Singapore)

Dr. Jeffrey Lam is currently the GM/Vice-President of Engineering at STAr-Quest Technologies. Prior to joining STAr Technologies, Dr. Lam was VP of Product, Test and Failure Analysis with GlobalFoundries for 19 years. He possesses more than 40 years of experience in Process Module, Design Engineering, Product/Yield engineering, Failure Analysis and Test Development Engineering. He has 17 technical patents and more than 100 publications. He has also been the chairman for SEMI “SGPSEA Product & Test Committee” since 2009 and serves as an Adjunct Associate Professor at the National University of Singapore. Dr. Lam received his B.S and M.S. in Chemical Engineering from UC Berkeley and UC Davis in 1979 and 1981 respectively. He obtained a second M.S in Electrical Engineering and Computer Science from the University of Santa Clara in 1986. In 2014, he received his PhD from the School of Physical and Mathematical Sciences, Nanyang Technological University. |

| 12:00 – 13:00 | Enjoy Lunch on the Luna Lawn! |

| 13:00 – 15:00 | SESSION 2: High Speed and RF Session Chair: Mark Ojeda (Infineon Technologies – San Jose, USA) |

| 13:00 – 13:30 | High Speed Digital: How to Optimize a Probe Card for PAM4 to a non-50 Ω deviceDaniel Bock (FormFactor – Beaverton, USA)

Daniel Bock got his Ph.D. in Physics at Carnegie Mellon University in 2006, working on Superconducting Nanowire Bolometers in the NanoFabrication Lab. He joined Form Factors RF Product Group in June of 2012. He led the development of the Custom Calibration Substrate (Custom ISS) product line to supplement the standard ISS line to improve the RF calibration methods for multi-DUT, irregular layout probe cards. He is also investigating the increase in digital signals, moving to PAM4 with higher baud rates, to improve wafer test for these devices. He enjoys camping with his family, as well as playing board games. |

| 13:30 – 14:00 | Contactless Measurement of RF Voltage Distribution in Antenna Switches at High Spatial Resolution Prof. Georg Schitter, Martin Schober (TU Wien – Vienna, Austria), Dr. Sergey Bychikhin (Alten Gmbh – Munich, Germany), Dr. Hans-Dieter Wohlmuth (Infineon Technologies AG – Neubiberg, Germany), Dr. Werner Simbürger (High Power Pulse Instruments GmbH – Haar, Germany) Mathias Poik (TU Wien – Vienna, Austria)

Mathias Poik is PhD student at the Automation and Control Institute (ACIN) at TU Wien, Austria. He received his MSc. in Energy Systems and Automation Technology from TU Wien in 2017. His primary research interests are the development of scanning probe-based methods for the evaluation of integrated circuits, and the development of electrical measurement modes for Atomic Force Microscopy. He currently works on a research project aimed at enabling contactless characterization of RF products on wafer-level at high spatial resolution. |

| 14:00 – 14:30 | 55GHz Octal-site Wafer Test Probecard for 5G mmWave devices Peter Cockburn (Cohu – Saint Paul, USA)

Peter Cockburn has worked in the ATE industry for over 30 years at Schlumberger, NPTest, Credence, LTXCredence, Xcerra and now Cohu. He is currently responsible for High Performance Contactor products, including fine-pitch coaxial contactors and probe heads for emerging 5G applications. After developing realtime and GUI software for ATE systems, he moved into product marketing and launched several new SOC ATE systems and analog test options as well as providing marketing and sales support in USA, Asia and Europe. As leader of the Test Cell Innovation team, he was responsible for defining and delivering complete test cells to customers to reduce cost, increase uptime and improve quality when testing pressure and motion sensors, microphones and wafer-level packages. He has an Engineering degree from the University of Southampton, UK. |

| 14:30 – 15:00 | 5G mmWave: Multi-site RF Probe Cards Enable Lower Cost-of-Test in Mass ProductionRyan Garrison (FormFactor, Inc. – Beaverton, USA)

Ryan Garrison is a Senior Product Business Manager with FormFactor’s Probes BU focused on RF probing solutions. With nearly 20 years at FormFactor, he has held multiple engineering and leadership roles in operations and the development of Analytical RF Probes, Probe Stations, and now Production RF Probes. His current responsibility centers on the business of expanding RF test parallelism for sub-6 GHz and mmW antenna devices. Most recently Ryan lead a team through the development-process-to-product-release of a new probe head effectively doubling the parallelism of RF test using FormFactor’s membrane technology. Prior to joining FormFactor, Ryan graduated from the Oregon State University in Industrial and Manufacturing Engineering. |

| 15:00 – 15:30 | Break – Poster Session |

| 15:00 – 15:30 | POSTER SESSION: Probe Potpourri 1 |

Magnetic Testing Tutorial – Wafer probing with 3D magnetic stimulation Georg Franz (T.I.P.S. Messtechnik GmbH – Villach, Austria)

Georg Franz has worked in the Semiconductor Industry for 20 years. After receiving his masters degree in mechanical engineering at the Technical University in Vienna, Austria he worked 7 years at Carinthian Tech Research in Villach, where he developed wafer handling equipment and micromanufacturing machines and conducted finite element simulations. In 2012 he joined T.I.P.S. Messtechnik, a probe card manufacturer focused on power, automotive and sensor devices. His main field of activity is the advancement of test technologies and the development of new products, especially high voltage test and magnetic sensor stimulation. Hydra Probes – Simplifying and Standardizing Semiconductor Test Tes Olson (Cohu – St Paul, USA) Rob Stoner (Cohu – Saint Paul, USA)

Rob Stoner is a Program Manager for the Interface Solution Group (ISG) of Cohu Incorporated. He graduated from Minnesota State University with a BSME and holds an MBA from the University. of St. Thomas. He spent the first 11 years of his career in the Defense industry, where he managed the development and production of avionic and shipboard systems. He joined Cohu in 2021 and has since managed the development of new R&D contactor solutions. Increasing transparency in wafer test probecard maintenance processes through targeted key performance indicators Lasse Meyer (Infineon Technologies Dresden GmbH & Co. KG – Dresden, Germany) Dr. Veronika Haehnel (Infineon Technologies Dresden GmbH & Co. KG – Dresden, Germany)

Dr. Veronika Haehnel joined the FE wafer test division at Infineon Dresden in 2017 and is currently as Staff Engineer Material Science responsible for the management and optimization of the probecard processes including database management, cleaning procedures, KPI creation & tracking as well as all quality and audit relevant topics. Initially, she worked as a Senior Engineer Wafer Test for Chipcard products including wafer test monitoring. Prior to joining Infineon she spent 8 years with Leibniz Institute for Solid State and Materials Research Dresden in basic research of nano- & microstructured electrodeposited systems. She holds a diploma engineering degree and a PhD in Materials Science from Technische Universität Dresden. Automated temperature calibration routine for prober chucks Harald Ibele (Sigma Sensors (TCL) GmbH – Sigmaringen, Germany)

Harald Ibele is the Owner, Technical and Quality Manager of Sigma Sensors, an A2LA ISO17025:2017 accredited Temperature Calibration Laboratory He first joined the Semiconductor Industry in 2003 working for a Microelectronic distributor and established an accredited calibration laboratory in 2005. In 2007 he joined a European thermal chuck manufacturer establishing their presence in the US before relocating to Asia to build their support network in 2012. Harald has extensive experience with temperature aspects of waferprobe, custom temperature solutions, prober sealing and thermal upgrades. After having returned to Europe in 2017 he directed global sales and customer support for thermal chucks before starting his own business in 2019. Sigma Sensors is based in Sigmaringen Germany with a newly established branch in the US. Sigma Sensors performs on site, accredited thermal chuck calibrations and manufactures the made for global mobility Cowboy Wafer. He currently lives in Germany and has 4 children. Small Pad/Small Pitch Dual-Sided Single-Level Space Transformer Dominik Schmidt (Translarity Inc. – Fremont, USA) Probe Debris Rating Scale Karan Maniar (Nidec SV TCL – Tempe, USA) Kyle Cotner (Nidec SV TCL – Tempe, USA)

Kyle graduated with a Bachelor of Science degree (cum laude) in Mechanical Engineering from the University of Arizona in 2005. He has worked in Germany and in the U.S. for start-ups, mid-size companies, and multinational corporations across the automotive, medical device, and now semiconductor test industries. Kyle joined the Nidec SV TCL team in late 2015 as the Product Engineering Manager based in Tempe, Arizona. He used his experience from other industries in project management and new product industrialization to improve the operational performance of the product engineering team and quickly came up to speed with the unique aspects of wafer test. In 2019, Kyle was promoted to Director of Engineering and added overall responsibility for engineering and design to his role. He has focused heavily on removing internal barriers and improving communication to streamline operations, improve quality and performance, and shorten lead time. In his free time, Kyle enjoys traveling (when Covid allows), golfing, running, and homebrewing. |

|

| 15:30 – 17:00 | SESSION 2A: Pushing the Test Limits Session Chair: Jerry Broz, PhD (SWTest Conference General Chair) |

| 15:30 – 16:00 | 3D IC probe card solution Brian Chang (Chunghwa Precision Test Tech.Co., Ltd. – Santa Clara)

Brian Chang is CHPT USA office manager, managing CHPT US sales/design/FAE team. Brian has worked for CHPT since 2003, was a PCB designer until 2005, then got promoted to PCB manager. 2006 setup Hsinchu office and serviced customer locally, 2010 established US office and got promoted as an office manager. Paul Tai (Chunghwa Precision Test Tech. Co., Ltd – Santa Clara)

Sales manager for CHPT North America |

| 16:00 – 16:30 | Automated temperature calibration: Tackling the challenge of temperature accuracy and uniformity measurements in wafer probing Bengt Haunerland (ERS electronic GmbH – Munich, Germany)

Bengt Haunerland joined ERS electronic GmbH in 2018 and is today Head of Software and Electronics. He has a Master’s degree in Electronics Engineering from Simon Fraser University in Canada. |

| 16:30 – 17:00 | Advancing Probe Card Parallelism for SOC Devices Johann Heitzer (Infineon – Munich, Germany), Cameron Harker (FormFactor – Livermore, USA) Pouya Dastmalchi (FormFactor Inc. – Livermore, USA)

Pouya Dastmalchi got his PhD in EE from LSU and joined FormFactor in 2016. Worked in probecard design team as an EDE for over 3 years and currently he is an Application Eng. Manager for SoC products working closely with different Semiconductor Wafer Test Groups. |

| 17:00 | Technical Sessions Adjourn and EXPO Opens at 17:00 |

| 17:00 – 20:00 | SWTest EXPO – 2022 |

| 17:00 – 20:00 | SWTest 2022 – Supplier and Sponsor EXPO Communicate, Collaborate and Celebrate! |

| 20:00 | Sponsor Hospitality Suites and Events |

| Tuesday, June 7, 2022 | |

|---|---|

| 7:00 – 8:00 | Continental Breakfast |

| 7:00 – Noon | Registration |

| 8:00 – 9:30 | Welcome and Visionary Keynote Speaker |

| 8:00 – 8:30 | Opening Remarks for SWTest 2022 Jerry Broz, PhD, SWTest General Chair, Advanced Probing Systems Introduction to the SWT Crew Initiative Karen Armendariz (Celadon Systems) and Amy Leong (FormFactor) |

| 8:30 – 9:30 | KEYNOTE

Advanced Packaging and Test Enabling Our Digital Society Advanced Packaging and Test Enabling Our Digital SocietyRebeca Jimenez, Corporate Vice President Advanced SiP Business Unit Amkor Technology, Inc AbstractSemiconductors are the building blocks of our modern digital society and allow us to be connected anywhere and everywhere. We interact with semiconductors every day through almost everything we do, whether using our smartphones, personal electronics, connected homes or our cars, which have become digital cockpits, immersed with advanced safety features. All of these digital interactions require massive computing and connectivity power to process, store and transfer data. Join me as we explore innovations in advanced packaging and test technology and how they enable further transformation in our digital society with a focus on the key catalysts of 5G, High Performance Computing, IoT and Automotive applications. BiographyRebeca Jimenez joined Amkor in 2014 and is currently Corporate Vice President, Advanced SiP Business Unit. Prior to assuming her current role, Ms. Jimenez served in various sales and strategic program management roles. She has more than 25 years of experience in the global semiconductor industry. Prior to joining Amkor, she spent 15 years with IDT (previously ICS) in both test engineering and operations roles as well as management positions. In addition, Ms Jimenez worked in various engineering and engineering management roles at Motorola. She holds a BS in Electrical Engineering from Arizona State University, as well as an MS in Electrical Engineering from National Technological University. |

| 9:30 – 10:00 | Coffee Break |

| 10:00 – 12:00 | SESSION 3: Reducing Costs (Cost of Ownership) Session Chair: Karen Armendariz (Celadon Systems – USA) |

| 10:00 – 10:30 | The Use of Artificial Intelligence and Big Data in the Production of Advanced Vertical Guide PlatesDr. Alan Ferguson (Oxford Lasers – Didcot, United Kingdom)

Alan has a degree from the University of Glasgow, Scotland in Theoretical Chemistry, and a doctorate in laser spectroscopy from the University of Cambridge. Whilst at Cambridge he gained a Research Scholarship to study at the Max Plank Institute in Gottingen, Germany. He has worked for several companies specialising in the “Applications of Lasers” and has been working in the field of lasers for over 35 years. At Oxford Lasers, Alan has held a number of positions including managing Research and Development as well as Sales and is currently a Director at Oxford Lasers with responsibility for Business Development. Alan has extensive knowledge on the use of lasers in the area of laser micro-machining covering a multitude of applications in particular the drilling of guide plates used in probe cards for wafer test. He has published numerous technical papers and patents and has written articles for a variety of magazines. Last year at SW Test he was awarded the “People’s Choice Award” for his presentation. |

| 10:30 – 11:00 | Control System for Enhancing the Life and Capability of Legacy, Modern and Mixed-Floor Probe Systems Albert Soto (Soto Technologies International – Pflugerville, USA)

Albert has 40 years of experience in the Robotics/Automation/Semiconductor industries. He started his career in 1982 at IBM implementing Robotics and Automation applications on the RT-PC Unix computers project. In 1988 transferred to Motorola MOS Digital/Analog semiconductor test group as Test Engineer for a decade ending as Test Director. Albert is currently the President/CEO of Soto Technologies which focuses on Prober Cell Controllers that standardize and enhance legacy probers to be more competitive with newer models. Also focuses on Test Data Analysis/STDF tools and non-intrusive machine OEE/Utilization tracking for wafer sort and final test. He has a diverse skill set ranging from hardware/embedded design using MCU/FPGA’s, machine shop skills and C/C++ programming for Embedded/Windows/LINUX systems. He holds a BSEE from University of Puerto Rico and has published articles at IEEE symposiums and is active in Martial Arts. |

| 11:00 – 11:30 | Probe Card Total Cost of Ownership in the Era of Complexity Steve Ledford (Teradyne – North Reading, USA)

Steve has 33 years experience in the semiconductor industry. He started his career with Motorola Semiconductor developing products for wireless applications. In 2000 he switched to the ATE equipment market during the birth of the SOC test market bringing multiple generations of systems, instrumentation, applications, and services to market for the past 22 years. Steve is currently the General Manager of the Device Interface Solutions business unit of Teradyne. He holds a Bachelors degree in Electrical Engineering from the University of Florida and a Masters of Business Administration from the University of Alabama. Steve has published over 20 articles in leading industry journals and conferences and is an inventor for more than 10 patents. |

| 11:30 – 12:00 | Assessing the Overall Cost of Ownership Bert Brost (Technoprobe – San Jose , USA) Mike Palumbo (Technoprobe – San Jose , USA)

Mike holds a BSEE degree from George Mason University in Fairfax VA. He spent the first 14 years of his career working at IBM facilities in East Fishkill, NY and Manassas, VA. Where he worked as test engineer evaluating the degradation of parametric test structures caused by ionizing radiation for IBM’s space products group. Next Mike joined Intel Corporation where he spent 22 years in Hillsboro, OR. Where the majority of those year he worked as a parametric test engineer. The last four years Mike worked as a commodity development engineer managing the creation of wafer level full die probe cards. Mike’s entire semiconductor career has been spent developing test solutions for evaluating next generation silicon process development products. Mike is now a director of new business development and product marketing at Technoprobe. |

| 12:00 – 13:00 | Enjoy Lunch on the Luna Lawn! |

| 13:00 – 15:00 | SESSION 4: New Probe Technologies Session Chair: Connie Smith (Texas Instruments) |

| 13:00 – 13:30 | Probing challenges using magnetic field Jory Twitchell (NXP Semiconductor)

Jory Twitchell works for NXP Semiconductors and has been with the company for 22 years. He currently works as a hardware development engineer. He oversees the development of wafer test hardware for business lines worldwide working with internal production partners to ensure the hardware meets their requirements. Jory is happy to have the opportunity to be back at SWTW in person to present to everyone. Brandon Mair (TechnoProbe America)

Brandon Mair is currently a strategic account manager for Technoprobe America Inc. Previous to this role, he had various roles at Texas Instruments spanning a total of 11 years. These positions ranged from Probe Manager to Equipment Engineering in some of the TI Fabs. He has attended numerous SWTW conferences over the last ten years and collaborated with many suppliers in the room today. Brandon is happy to be here in person with everyone! |

| 13:30 – 14:00 | UFO Probe™ Card – New dimensions in wafer-level test of photonic integrated circuits Tobias Gnausch (Jenoptik Optical Systems GmbH – Jena, Germany)

Tobias Gnausch, Product Manager at JENOPTIK, received his diploma in physics from the University of Jena in 2005. He worked as a mechanical engineer and developer for interferometric stylus measurement systems at BOSCH. In 2008, he joined JENOPTIK as an optical designer for diffractive optical elements and systems. From 2012, he was responsible for the product management of UV- micro optics for Semiconductor Equipment. Beginning of 2016, he took over the product responsibility of a new business sector within the Business Unit Micro-Optics, which included a product development for wafer-level testing of PICs. |

| 14:00 – 14:30 | Extreme Power Probing – Challenges of 3000A and more Sebastian Salbrechter (TIPS Messtechnik- Austria) Dr. Rainer Gaggl (TIPS Messtechnik- Austria)

Rainer Gaggl, born in 1966, married, 3 kids, holds a PhD in Physics from the Technical University of Graz. He is passionate for micro-mechanics and aviation: 1994 Guiness Book of Records – “The smallest piston aircraft engine in the world.” Milestones in his career:

He is managing director in T.I.P.S. and responsible for product and process development as well as strategic sales activities. The main focus in his work is on test interfaces for High Power Devices, Automotive ASICS, Sensors and MEMS devices, Automotive RADAR. High Voltage, High Currents and probe cards with sensor stimuli are some of his “playgrounds as a physicist” and he holds several patents in that field. Diana Damian (TIPS Messtechnik- Austria)

|

| 14:30 – 15:00 | Copper pad probing with vertical technologies featuring hard metal tip: ARIANNA™ probe family Mattia De Nicola (STMicroelectronics – Italy) Dr. Emanuele Bertarelli, Raffaele Vallauri (Technoprobe – Italy) Dr. Alberto Pagani (STMicroelectronics – Italy)

Alberto Pagani received master degree in Electronic Engineering in 2000 from Politecnico di Milano, Italy. In the same year, he joined STMicroelectronics, Agrate Brianza, Italy. From 2000 to 2006 he worked in wafer sort department as Process and Test Engineer on Flash memories. Since 2006, he is in charge of Test R&D and Competitive Intelligence. He is member of STMicroelectronics Technical Staff and internal teacher. His work is mainly focused on innovative testing / probing technologies and new product / technology development for new markets. Dr. Pagani’s awards include 2010 Sesames Award and 2010 RFID Italy award. He was also the winner of the 2016 VLSI Test Symposium Best Special Session Award. He holds more than 100 patents in USA, Europe and China in several technical fields. Erwin Verardi (STMicroelectronics – Italy)

Erwin Verardi’s Current job: STM, sr. EWS process Eng. Salvatore De Siena (Technoprobe – Italy)

Salvatore De Siena is R&D Lab Manager, working in Technoprobe Italy headquarter since 2018. Previously he worked as Process Engineer for Technology team and Process Kaizen Engineer – team leader, following in particular probe head manufacturing processes. He is currently responsible for Technoprobe R&D Laboratories. |

| 15:00 | Technical Sessions Adjourn and EXPO Opens |

| 15:00 – 17:00 | SWTest EXPO – 2022 |

| 15:00 – 17:00 | SWTest 2022 – Supplier and Sponsor EXPO Communicate, Collaborate and Celebrate! |

| 17:00 – 18:00 | SWT Crew Social Event |

| 18:00 – 21:00 | SWTest Social Event – Luau Party |

| 21:00 | Sponsor Hospitality Suites and Events |

| Wednesday, June 8, 2022 | |

|---|---|

| 7:00 – 8:00 | Continental Breakfast |

| 8:00 – 9:30 | SESSION 5: Pads, Bumps, and Defects Session Chair: Dr. Michael Huebner (FormFactor) |

| 8:00 – 8:30 | An Advanced Method for Pad Stack Crack Assessment during Probe-Over-Active-Area Dr. Marianne Unterreitmeier, Dr. Eric Liau (Infineon Technologies Germany), Mark Ojeda (Infineon Technologies – USA) Dr. Oliver Nagler (Infineon Technologies Germany)

Dr. Oliver Nagler finalized his diploma degree (Dipl.-Ing.) of aerospace engineering at the Technical University of Munich in 1994 and received his physical doctorate degree (Dr.-Ing.) in electrical engineering from the Bundeswehr der Universität, Munich in 2008. He started his career as a research engineer at the Fraunhofer Institut for Solid State Technology in Munich in 1995. Since 1999, he’s been an employee at Infineon Technologies AG, Neubiberg, Germany, currently in the department of Test Technology and Innovation. He is a lead principal for contact technologies and head of Infineon’s R&D probing lab. Oliver holds several patents and international publications in probing technology and processes. In cooperation with national and international universities, he is regularly supervising bachelor, master, and Ph.D. students. |

| 8:30 – 9:00 | On Shifting Defect Detection in Quantum Chips From Cryogenic to Ambient Temperature Roy Li, Erik Jan Marinissen, Fahd Ayyalil Mohiyaddin, Michele Stucchi, Georges Gielen (IMEC – Leuven, Belgium) Francesco Lorenzelli (IMEC – Leuven, Belgium)

Francesco Lorenzelli received a Master’s Degree cum Laude in Electrical Engineering at the University of Bologna in October 2020, with the Thesis: “Development of Innovative Algorithms and Tools to Test Advanced Technology Cell Libraries”, with Prof. Cecilia Metra as main supervisor, Martin Omana and Erik Jan Marinissen as co-supervisors, in a joint project with Cadence Design Systems, TU Eindhoven and IMEC. He is currently a PhD student at IMEC, with a project on testing of circuits for quantum computers. His focus is testing of silicon spin qubit devices at ambient or at mildly lowered temperatures. |

| 9:00 – 9:30 | Reducing test time by exploiting scan ATPG-based patterns targeting high density Prof. Paolo Bernardi, Giusy Iaria, Prof. Matteo Sonza Reorda (Politecnico di Torino – Italy) Davide Appello, Giuseppe Garozzo, Vincenzo Tancorre, Roberto Ugioli (ST Microelectronics – Italy) Francesco Angione (Politecnico di Torino – Italy)

Francesco Angione is a Computer Engineering with an M.Sc., Embedded Systems track, obtained from Politecnico di Torino in 2020. Currently, he is a Ph.D. student at Politecnico di Torino in the CAD & Reliability group. His main interests are real-time operating systems, computer architectures, and their dependability applied to automotive System-on-Chip. |

| 9:30 – 10:00 | Novel reverse engineering way of fine pitch pre-bump probe head development in pureplay foundries to enable early-stage yield learning and DFA support via PBI/RDL MEMS technology Chan Yin Hong Patrick, Chithambaram Shaalini, Chen Changqing (GlobalFoundries – Singapore, Singapore), Dr. Jeffrey Lam, Yang Qu (Star-Quest – Singapore), Dr. Choon-Leong Lou (STAr Technologies – Taiwan), Dr. Szu Huat Goh (Qualcomm) Dr. Jeffrey Lam (Star-Quest – Singapore)

Dr. Jeffrey Lam is currently the GM/Vice-President of Engineering at STAr-Quest Technologies. Prior to joining STAr Technologies, Dr Lam was VP of Product, Test and Failure Analysis with GlobalFoundries for 19 years. He possesses more than 40 years of experience in Process Module, Design Engineering, Product/Yield engineering, Failure Analysis and Test Development Engineering. He has 17 technical patents and more than 100 publications. He has been the chairman for SEMI SEA Product & Test Committee since 2009 and serves as an Adjunct Associate Professor at the National University of Singapore. Dr. Lam received his B.S and M.S. in Chemical Engineering from UC Berkeley and UC Davis in 1979 and 1981 respectively. He obtained a second M.S in Electrical Engineering and Computer Science from the University of Santa Clara in 1986. In 2014, he received his PhD from the School of Physical and Mathematical Sciences, Nanyang Technological University. |

| 10:00 – 10:15 | Coffee Break |

| 10:15 – 12:00 | SESSION 6: Changes on the Horizon Session Chair: Patrick Mui (JEM America) |

| 10:15 – 10:45 | Advances in Vertical Probing for High-Speed Digital Test at Wafer Sort David Raschko (FormFactor – USA)

David Raschko currently works as a Product Marketing Manager at FormFactor where he manages their Apollo product line focused on the Logic and Foundry market. Prior to his current role at FormFactor, David worked as a Product Engineer at FormFactor where he was responsible for developing and growing the mmWave Probe Card business in the 5G AIP market. Raschko received his MBA from Washington State University in 2021 with a finance concentration and completed his M.S. in Applied Physics at the University of Oregon in 2015 with a focus in Optics |

| 10:45 – 11:15 | Shifting Left = More Wafer ProbeDave Armstrong (Advantest – USA)

In his capacity as Principal Test Strategist, Dave Armstrong works directly with customers and Advantest’s global R&D teams to define develop and deliver creative solutions to the most demanding test challenges. Additionally, Dave is chairs multiple working groups exploring the photonic device testing roadmap. Prior to joining Advantest in 2004, Dave spent over two decades in HP/Agilent’s IC test group working with customers to test industry leading devices. Prior to joining HP Dave worked in the semiconductor industry in areas of IC and system design, product/yield engineering, as well as test engineering. Dave Armstrong received degrees in Electrical, Computer, and Environmental Engineering from the University of Michigan in 1974. |

| 11:15 – 11:45 | The semiconductor industry is fast adapting to a new reality. How can suppliers of probe cards keep up? John West (Yole Intelligence – London, United Kingdom)

John is a Senior Division Director at Yole Intelligence and has more than 20 years of experience working in the semiconductor industry. His special areas of interest cover probe cards, test and burn-in sockets, device interface boards, and the key enabling technologies used in wafer fab equipment. |

| 11:45 – 12:00 | SWTest 2022 Awards and Adjournment |

See you in 2023!

Travel Safe and Stay Healthy!

| SWTest 2022 ON-Demand – Probe Potpourri 2 June 9 – July 9, 2022 |

|

|---|---|

| Introduction of new probe, VPT (Vertical Probe Transformed) Kazunori Kobayashi (Sinko Corporation – Niigata, Japan) Tadashi Rokkaku (Probe Innovation USA, LLC – Irving, USA)

Educational background

Professional Career

|

|

| Next Generation DRAM Temperature Requirements and Impacts to Full Wafer Contactor Probe Card Performance Hyun Ae Lee (Samsung – Suwon, Korea) Myungjin Lee (FormFactor – Livermore, USA)

MJ has been with FormFactor for over 10 years and is currently serving as Director of Product Marketing in the probes business unit. In this role, he has responsibility for Memory Probe card solutions specifically for the DRAM market. With over 25 years of experience in the Semiconductor Memory industry, MJ has held various roles in product marketing, sales, product engineering at Formfactor, SK Hynix, Micron, and Samsung. |

|